# OpenHW Group

CORE-V: Open Source RISC-V Cores Commercial Adoption

Lesson Learned

Rick O'Connor <u>rickoco@openhwgroup.org</u>

T <u>@rickoco</u> T <u>@openhwgroup</u>

www.openhwgroup.org

### Outline

- OpenHW Group History

- OpenHW ~ 3 Years Later Lessons Learned

- Lesson 1 Permissive Use

- Lesson 2 IP Quality

- Lesson 3 Roadmap & Ecosystem

- Summary

# OpenHW Launch June 2019

- OpenHW Group Launch at ETH Zurich 11 June 2019

- 13 Initial Sponsors & 2 Projects

- https://riscv.org/proceedings/2019/06/risc-v-workshop-zurich-proceedings/

#### OpenHW Group Initial Sponsors

• OpenHW Group becomes official committer for these repositories

| Core          | Bits/Stages        | Description                                                                                                                                                                                                                                                                                                                         |

|---------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>RI5CY</u>  | 32bit /<br>4-stage | A 4-stage core that implements, the RV32-IMC, has an optional 32-bit FPU supporting the F extension and instruction set extensions for DSP operations, including hardware loops, SIMD extensions, bit manipulation and post-increment instructions.                                                                                 |

| <u>Ariane</u> | 64bit /<br>6-stage | A 6-stage, single issue, in-order CPU implementing RV64IMCD extensions with three privilege levels M, S, U to fully support a Unix-like (Linux, BSD, etc.) operating system. It has configurable size, separate TLBs, a hardware PTW and branch-prediction (branch target buffer, branch history table and a return address stack). |

© OpenHW Group - RISC-V / WOSH ETH Zurich

11 June 2019

© OpenHW Group - RISC-V / WOSH ETH Zurich

© OpenHW Group

lune 2023

- OpenHW Group is a not-for-profit, global organization registered in Canada and Europe. The OpenHW ecosystem is driven by members (corporate & academic) and individual contributors where HW and SW designers collaborate in developing open-source cores, related IP, tools and SW such as the CORE-V Family of open-source RISC-V processors

- International footprint with developers in North America, Europe and Asia

- Providing an infrastructure for hosting high quality open-source HW developments in line with industry best practices

- Strong support from industry, academia and individual contributors worldwide

© OpenHW Group June 2023

whalemicro

### Academic Members 104+ Members & Partners

**Universidade do Minho**

Science and **Technology Facilities Council**

### Partner Ecosystem 104+ Members & Partners

# OpenUK & ORCRO

Accounting, Legal, Banking

# Working Groups & Task Groups

- Board of Directors approves elected Chairs of Working Groups and has final approval of working group recommendations

- Technical Working Group

- Cores Task Group

- Verification Task Group

- SW Task Group

- HW Task Group

- Marketing Working Group

- University Outreach Task Group

- OpenHW Asia Working Group

- OpenHW Europe Working Group

- Together with internal OpenHW Group engineering staff, member company development engineers (FTEs / ACs) establish and execute OpenHW Group projects

- 20+ active projects across CORE-V RTL, Verification, GCC / LLVM, IDE, RTOS, FPGA, SoC, etc. with more projects in the pipeline

# OpenHW Cores Task Group

- Chair: Arjan Bink, Silicon Laboratories

- Vice-Chair: Jérôme Quévremont, Thales Research & Technology THALES

- develop feature and functionality roadmap and the open-source IP for the cores within the OpenHW Group such as the CORE-V Family of open-source RISC-V processors.

- Initial contribution of open-source RISC-V cores from <u>ETH Zurich PULP Platform</u> and the OpenHW Group is the <u>official committer for these repositories</u>

| Core             | Bits/Stage         | Description                                                                                                                                                                                                                                                                                                                                         |

|------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CVE4<br>(RI5CY)  | 32bit /<br>4-stage | A family of 4-stage cores that implement, RV32IMFCXpulp, optional 32-bit FPU, instruction set extensions for DSP operations including HW loops, SIMD extensions, bit manipulation and post-increment instructions.                                                                                                                                  |

| CVA6<br>(Ariane) |                    | A family of 6-stage, single issue, in-order CPU cores implementing RV64GC extensions with three privilege levels M, S, U to fully support a Unix-like (Linux, BSD, etc.) operating system. The cores have configurable size, separate TLBs, a HW PTW and branch-prediction (branch target buffer, branch history table and a return address stack). |

© OpenHW Group

### **CORE-V**® Cores Roadmap

|                      | CODE                                                                                                                                                           | CORE TRL 2020 2021 2021 |           | 022        | 2023      |           |                   |         |           |                 |          |       |               |     |            |               |     |    |            |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------|------------|-----------|-----------|-------------------|---------|-----------|-----------------|----------|-------|---------------|-----|------------|---------------|-----|----|------------|

|                      | CORL                                                                                                                                                           | TARGET                  | Q1        | Q2         | Q3        | Q4        | Q1                | Q2      | Q3        | Q4              | Q1       | Q2    | Q3            | Q4  | Q1         | Q2            | Q3  | Q4 | ļ          |

|                      | CVA6:<br>CV32A60X                                                                                                                                              | 4                       |           |            | PC        |           | PL                |         |           |                 | PA       |       |               |     |            |               |     |    |            |

| ~                    | CV32A60X is R                                                                                                                                                  | V32IMCA                 | with CV-  | X-IF sup   | port; 202 | 23 target | t is TRL4         | LCVA6   | family ta | argets R        | V[32,64] | GC @T | RL5.          |     |            |               |     |    |            |

| APPLICATION<br>CLASS | CVA5                                                                                                                                                           | 3                       |           |            |           |           |                   |         |           |                 |          |       |               |     |            |               |     |    |            |

|                      |                                                                                                                                                                |                         |           |            |           |           |                   |         |           |                 |          |       |               |     |            |               |     |    |            |

| F 0                  | RV32IMA soft-core for FPGA                                                                                                                                     |                         |           |            |           |           |                   |         |           |                 |          |       |               |     |            |               |     |    |            |

| A                    | CV-WALLY                                                                                                                                                       | 4                       |           |            |           |           |                   |         |           |                 |          |       |               | PC  | P          | $\times$      | A — |    | 2024<br>Q4 |

|                      | RV32I, RV32E, and RV64I, 5-stage, support for A, C, D, F, and M extensions, and optional caches, branch prediction, virtual memory, AHB, RAMs, and peripherals |                         |           |            |           |           |                   |         |           |                 |          |       |               |     |            |               |     |    |            |

|                      | CV32E40PV1                                                                                                                                                     | 5                       | PC        | PL         | F         | А         | PF                |         |           |                 |          |       |               |     |            |               |     |    |            |

|                      | RV32IMC                                                                                                                                                        |                         |           |            |           |           |                   |         |           |                 | •        |       |               |     |            |               |     |    |            |

|                      | CV32E40PV2                                                                                                                                                     | 5                       |           |            |           |           |                   | PC      |           | PL              |          |       |               |     | PA         |               |     |    |            |

|                      | RV32IM[F]CZicou                                                                                                                                                | int_Zicsr_Zif           | encei[PU  | LP_XPUL    | .P][PULP  | _CLUSTE   | ER][PULP          | _ZFINX] |           |                 |          |       |               |     |            |               |     |    |            |

| Q                    | CV32E41                                                                                                                                                        | 3                       |           |            |           |           |                   | PC      | >         |                 |          |       |               |     |            |               |     |    |            |

| SS                   | RV32IMCZicount_                                                                                                                                                | _Zicsr_Zifend           | cei[_Zce] | [{F,_Zfinx | )][PULP_) | XPULP][i  | PULP_CL           | USTERI  |           |                 | •        |       |               |     |            |               |     |    |            |

| EMBEDDED<br>CLASS    | CV32E40X                                                                                                                                                       | 5                       |           |            |           |           | PL                | РА      |           |                 |          |       |               |     |            |               |     |    |            |

|                      | RV32[I,E][M Zmmul][A]Zca_Zcb_Zcmp_Zcmt[Zba_Zbb_Zbs Zba_Zbb_Zbc_Zbs]ZicntrZihpmZicsrZifencei[X]                                                                 |                         |           |            |           |           |                   |         |           |                 |          |       |               |     |            |               |     |    |            |

|                      | CV32E40S                                                                                                                                                       | 5                       |           |            |           |           | PL                | РА      |           |                 |          |       |               |     |            | •             | 1   |    |            |

|                      | RV32[I E][M Zmmul]Zca_Zcb_Zcmp_Zcmt[Zba_Zbb_Zbs Zba_Zbb_Zbc_Zbs]ZicsrZifenceiXsecure @TRL5                                                                     |                         |           |            |           |           |                   |         |           |                 |          |       |               |     |            |               |     |    |            |

|                      | CV32E20                                                                                                                                                        | 5                       |           |            |           |           |                   | PC      |           |                 | PL       |       |               |     | <b>—</b> ( | A >—          |     |    |            |

|                      | RV32{I,E}[M]CZic                                                                                                                                               | count_Zicsr_2           | Zifencei[ | Zce]       |           |           |                   |         |           |                 |          |       |               |     |            |               |     |    |            |

|                      |                                                                                                                                                                |                         | Openi     | HW Proj    | ect Gate  | es        | Project<br>Concep |         | PL        | Projec<br>Launc |          | PA    | Plan<br>Appro | wed | P          | Proj<br>F ree |     |    |            |

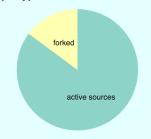

## OpenHW Collaboration Stats

#### CoderStats(openhwgroup)

GitHub user name

Get Stats

#### **OpenHW Group**

Joined GitHub 27 May 2019

- openhwgroup

- ☆ www.openhwgroup.org

- Ottawa, Ontario, Canada

#### Repo types

♦ Pushed to repos

♠ Main languages

♠ Total issues

▶ Total forks

★ Total stars

♣ Followers

♣ Following

54

10

769

1627

4171

326

0

#### **Summary**

OpenHW Group has 55 repositories on GitHub, the latest 55 with user activity were loaded from GitHub's web service for this evaluation. OpenHW Group has pushed to 54 of these repositories. This is a high ratio congratulations!

10 different main languages were identified across all repos pushed to. The main language is the one with the largest amount of code in a given repository, as identified by GitHub's linguist. Assuming a basic level of proficiency in all these languages OpenHW Group can be considered hyperpolyglot in the world of computer languages. **SystemVerilog** occurs most frequently - 14 times - as the main repo language.

The total number of forks across all pushed to repositories indicates that the GitHub projects OpenHW Group contributes to are actually used by other people.

#### Rankings

© OpenHW Group June 2023 1

# Silicon Labs OpenHW Leadership

"As a leader in secure, intelligent wireless technology for a more connected world, Silicon Labs products need efficient, low-cost, customizable processor cores to realize our customers' performance requirements.

The OpenHW CORE-V CVE4 family of open-source RISC-V cores satisfy these requirements, and Silicon Labs has taken a leadership position within the OpenHW ecosystem to help drive the execution of various CORE-V CVE4 projects.

A range of Silicon Labs SoC products have adopted various CVE4 cores and have launched into high-volume production," said Daniel Cooley, Silicon Labs CTO & Board Member, OpenHW Group.

# Thales OpenHW Leadership

"In 2018, Thales joined the RISC-V Foundation to help design the RISC-V open instruction set and above all to rally manufacturers and academics around a subject that is crucial for our sovereignty.

In 2019, Thales was a founding member of the OpenHW Group and has taken a leadership role within open-source hardware communities to design processors for critical embedded systems, particularly in the aerospace, defence and cybersecurity sectors with a particular focus on the OpenHW CORE-V CVA6 processor.

Open-source solutions for hardware as well as software are becoming more integral than ever to Thales's innovation strategy." said Daniel Glazman, VP Software Technologies at Thales.

### Open Source HW Adoption Lessons

- Lesson 1 Permissive use

- permissive open-source licensing and processes to minimize business and legal risks

- Lesson 2 IP quality

- harness community best-in-class design and verification methods and contributions

- Lesson 3 Roadmap & Ecosystem

- ensure availability of IDE, RTOS / OS ports, physical design etc. and create a roadmap of cores covering a range of PPA metrics

© OpenHW Group June 2023 14

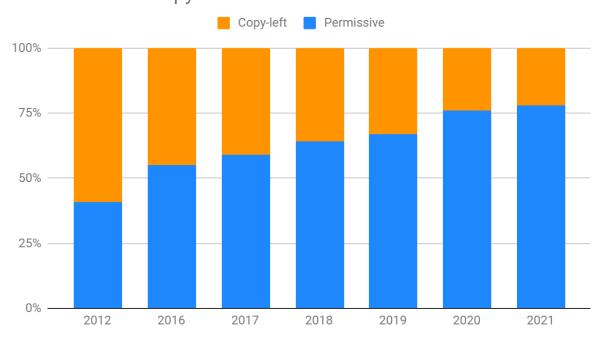

# Open Source License Usage

#### Permissive vs. Copy-left Licenses Over Time

#### Top Open Source Licenses in 2021

https://www.whitesourcesoftware.com/resources/blog/open-source-licenses-trends-and-predictions/

© OpenHW Group June 2023 15

# HW Companies & Open Source

- Large Systems & Semiconductor companies have very deep patent portfolios

- Copyleft / GPL style licenses are generally seen to pose a greater risk of unwanted patent exposure

- Companies need to see commercial benefit to 'give back' and not be forced to give back through license terms

- Apache provides permissive terms with both copyright and patent grants – also, most HW companies have already accepted Apache for SW projects

- But is Apache enough?

# Solderpad Hardware License 2.1

- A permissive open hardware license

- Based on, and acts as an exception to, Apache-2.0

- SPDX-License-Identifier: Apache-2.0 WITH SHL-2.1

- Covers physical hardware as well as open silicon and gateware

- Modifies, clarifies and extends various Apache definitions, and the scope of rights to explicitly cover hardware

- Not specifically OSI approved, but we know it falls within the OSI definition of "open source" because any licensee can treat as plain Apache-2.0

- http://solderpad.org/licenses/SHL-2.1/

### Open Source HW Adoption Lessons

- Lesson 1 Permissive use

- permissive open-source licensing and processes to minimize business and legal risks

- Lesson 2 IP quality

- harness community best-in-class design and verification methods and contributions

- Lesson 3 Roadmap & Ecosystem

- ensure availability of IDE, RTOS / OS ports, physical design etc. and create a roadmap of cores covering a range of PPA metrics

© OpenHW Group June 2023 1

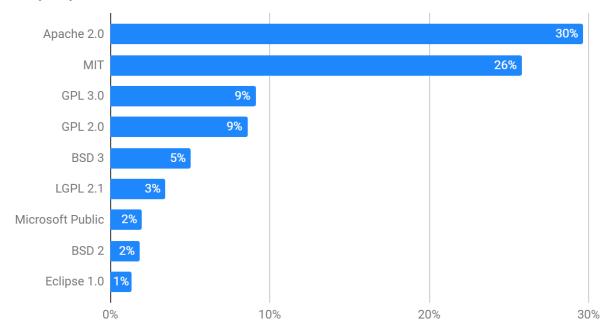

# OpenHW Verification Task Group

- · Chair: Simon Davidmann, Imperas

- Vice-Chair: Jean-Roch Coulon, Thales Silicon Security

### THALES

Develop best in class verification test bench environments for the cores and IP blocks developed within the OpenHW Group.

June 2023

# Industry Standard Tools

Use industry standard languages and verification methods

Open-Source projects need to fit easily into ecosystem companies' existing EDA tool flow. Leverage the best commercial tools for the job

ALDEC Cadence Imperas

EE metrics SIEMENS SYNOPSYS®

# Next Gen: universal UVM environment for CORE-V Verif

21

© OpenHW Group June 2023

### Open Source HW Adoption Lessons

22

- Lesson 1 Permissive use

- permissive open-source licensing and processes to minimize business and legal risks

- Lesson 2 IP quality

- harness community best-in-class design and verification methods and contributions

- Lesson 3 Roadmap & Ecosystem

- ensure availability of IDE, RTOS / OS ports, physical design etc. and create a roadmap of cores covering a range of PPA metrics

© OpenHW Group June 2023

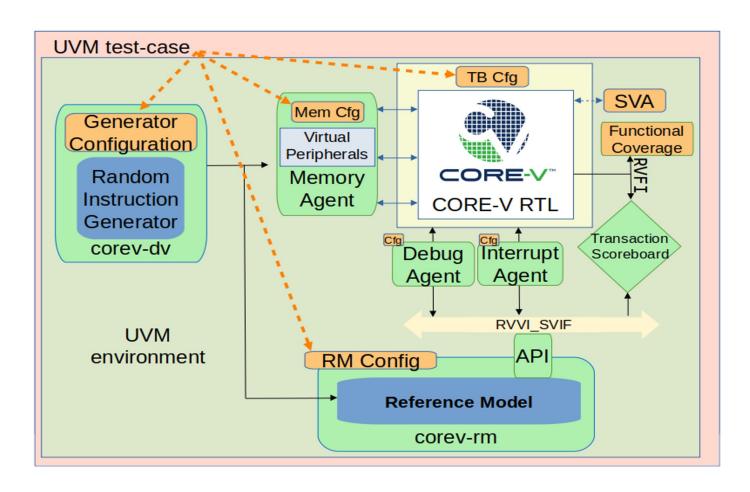

# SW Task Group

- Chair: Jeremy Bennett, Embecosm

- Vice-Chair: Yunhai Shang, Alibaba T-Head

- Define, develop and support SW tool chain, operating system ports and firmware for the cores and IP developed within the OpenHW Group

- SW TG active projects include: GCC / LLVM, IDEs, FreeRTOS, HAL, CORE-V MCU SDK, etc.

© OpenHW Group

© OpenHW Group

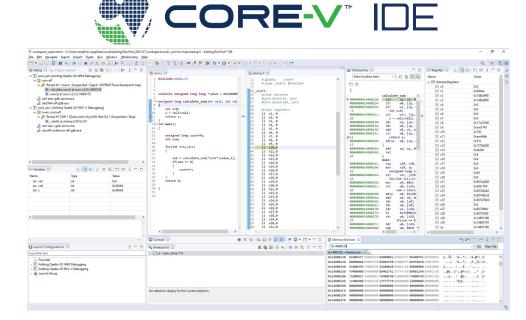

- CORE-V IDE is an opensource development under the SW TG at the OpenHW Group

- Eclipse based IDE for CORE-V development

- Includes the GCC Toolchain for CORE-V

- OpenOCD Debug Support

- "Ready-to-run" examples for Digilent FPGA boards

- Getting started guides

# HW Task Group

· Chair: Hugh Pollitt-Smith, CMC Microsystems

- · Vice-Chair: Tim Saxe, QuickLogic

- define, develop and support SoC and FPGA based evaluation / development platforms for the cores and IP developed within the OpenHW Group.

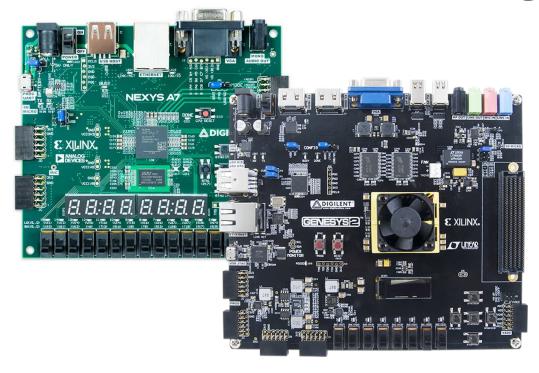

### **CORE-V® FPGA Emulation**

CORE-V projects leverage Digilent NexysA7 & Genesys2 FPGA boards for soft-core bring up for both CVE4 and CVA6 Families

Opella LD Debug Probe

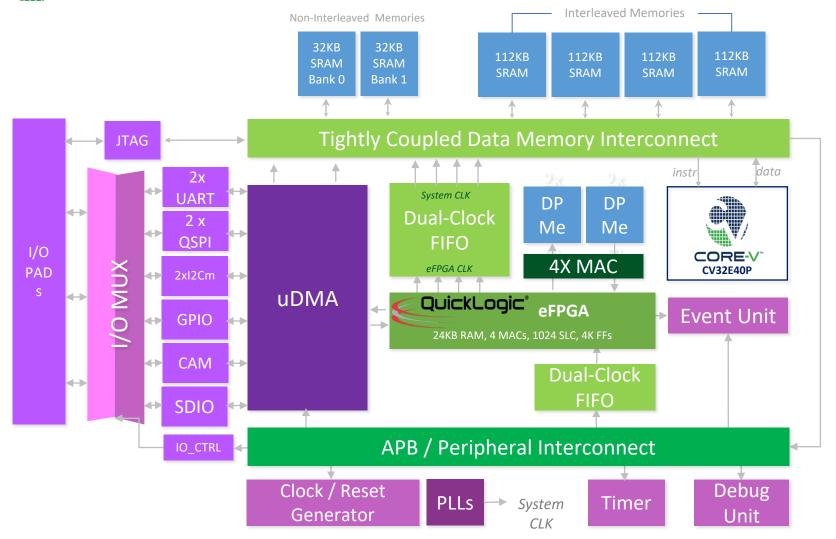

### CORE-V® MCU in fab now

- Real Time Operating System (e.g. FreeRTOS) capable

~300+MHz CV32E4 MCU

- Embedded FPGA fabric with hardware accelerators from QuickLogic

- Multiple low power peripheral interfaces (SPI, GPIO, I2C, HyperRAM, CAMIF, etc) for interfacing with sensors, displays, and connectivity modules

- Built in 22FDX with

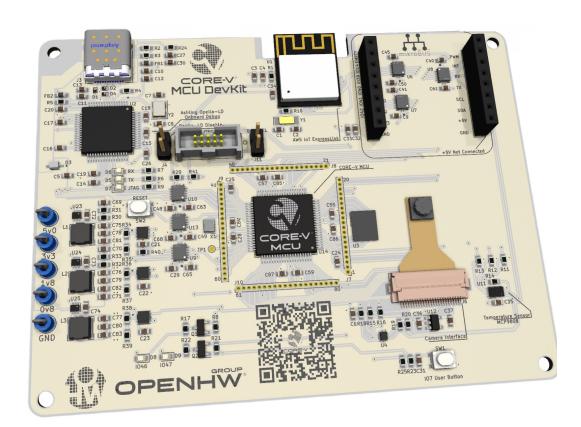

### CORE-V® MCU DevKit

**OpenHW CORE-V DevKits**

- CORE-V MCU SoC

- CV32E40P processor core

- Quicklogic ArticPro eFPGA

- Global Foundries 22FDX

- Ashling Opella-LD onboard JTAG debug module

- USB-C for terminal and onboard debug access

- JTAG connector for external debug access

- Espressif AWS IoT ExpressLink Module for AWS IoT cloud interconnect

- mikroBUS onboard socket, allowing access to a vast range of mikroBUS modules

- 40 pin expansion header

- I2C temperature sensor

- Early Access CORE-V MCU DevKits can be reserved on the <u>GroupGets campaign page</u> (quantities are limited)

June 2023

28

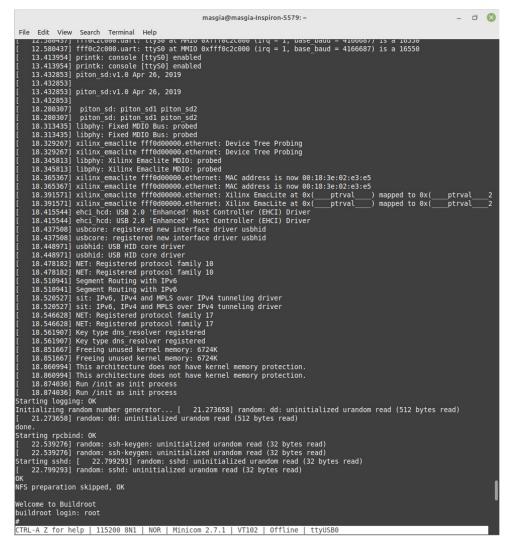

## CVA6 – dual core SMP Linux on Genesys2

### Open HW ~3 Years Later Lessons Learned

- Lesson 1 Permissive use

- permissive open-source licensing and processes to minimize business and legal risks

- Lesson 2 IP quality

- harness community best-in-class design and verification methods and contributions

© OpenHW Group

- Lesson 3 Roadmap & Ecosystem

- ensure availability of IDE, RTOS / OS ports, physical design etc. and create a roadmap of cores covering a range of PPA metrics

- OpenHW Group & CORE-V Family of open-source RISC-V cores for use in high-volume production SoCs

- Visit <u>www.openhwgroup.org</u> for community information

- Visit OpenHW GitHub <a href="https://github.com/openhwgroup">https://github.com/openhwgroup</a> for projects

- Learn more at <u>OpenHW TV</u>

Follow us on Twitter @openhwgroup & LinkedIn OpenHW Group

© OpenHW Group June 2023 31