# **RISC-V Is Firing On All Cylinders**

Charlie Su, Ph.D. CTO and President

2023/06/06

# **Andes Technology Corporation**

### Andes and RISC-V International (RVI)

- Founding & Premier Member from 2016

- Board of Directors

- Technical Steering Committee

- Chairs/Co-Chairs of Task Groups

- Ambassador

#

### **Quick Facts**

18 Years300+ CustomersPureplay CPU vendorLicensing AndesCore™

**80K**<sup>+</sup> Users AndeSight IDE **12Bn<sup>+</sup>** SoC Total Customer Shipment

ANDES Confidential

| AX60 Series<br>13-stage OOO MP         |                  | AX65                       | AX67                                      | AX60-SE            | A72~A78;<br>N1/V1/X1    |  |  |  |  |

|----------------------------------------|------------------|----------------------------|-------------------------------------------|--------------------|-------------------------|--|--|--|--|

| Categories                             | Power-efficient  | Mid-range                  | Extended                                  | FUSA               |                         |  |  |  |  |

| 45 Series<br>8-stage Superscalar       | N45, NX45        | <mark>NX45V*</mark><br>D45 | <mark>AX45MPV</mark><br>A45(MP), AX45(MP) | D45-SE             | A53/55, R52/<br>R82, M7 |  |  |  |  |

| 27 Series<br>5-stage MemBoost          |                  | NX27V                      | A27(L2), AX27(L2)                         |                    | A5/7/35                 |  |  |  |  |

| 25 Series<br>5-stage Fast&Compact      | N25F, NX25F      | D25F                       | A25(MP), AX25(MP)                         | D25F-SE<br>N25F-SE | A5/7/35, R4/5,<br>M4/33 |  |  |  |  |

| <b>Compact Series</b>                  | N225             | D23                        |                                           | D23-SE             | M0/0+/3/33/4            |  |  |  |  |

| Categories                             | Embedded Control | DSP/Vector                 | Linux AP                                  | FUSA               | References              |  |  |  |  |

| Note *: AX45MPV configured as one core |                  |                            |                                           |                    |                         |  |  |  |  |

# **Andes Powering RISC-V Applications Everywhere**

N25F, N45

Edge. Cloud. Space.

20 Detworks

N25F, A25, A45MP, AX45MP

N25F

### Taking 🔀 RISC-V\* Mainstream

# AIOT

### Renesas Voice-Control ASSP Solution

- R9A06G150 32-bit 100MHz ASSP with Andes DSP-capable D25F, which speeds up the application by over 50%.

- Cyberon, an expert in voice recognition technology

- **Orbstar**, a system integrator specializing in embedded solutions

- SEGGER, supporting the ASSP with Embedded Studio and J-Link

### ASUS IOT <u>Tinker V</u> Single-Board Computer:

- Based on Renesas RZ/Five 1GHz SoC with Andes AX45MP

- Supporting Linux Debian and Yocto distro with rich connectivity

- Ideal for Industrial IoT and gateway applications

### Powered by Andes D25F/AX45MP

Taking 🛃 RISC-V\* Mainstream

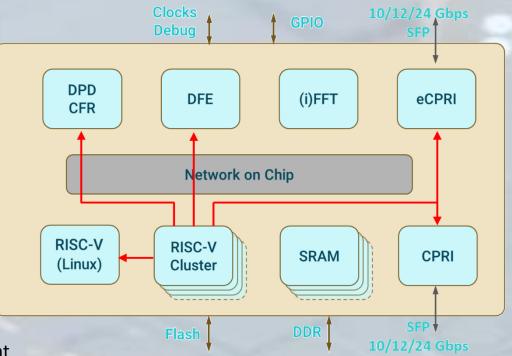

# **5G Small Cell SoC for Open-RAN**

### Picocom PC80x uses RISC-V Clusters and Linux core

4-lane

JESD204B

- Low power

- Flexible control for

- Task scheduling

- Memory management

- Event handling

- Computation assistance for

- DFE (Digital Frontend)

- DPD (Digital Pre-Distortion)

- Support protocol/interface upgrades

- CPRI (common public radio interface)

- eCPRI (enhanced CPRI)

### Friendly development environment:

Zephyr and Linux for application development

Powered by Andes N25F/A27

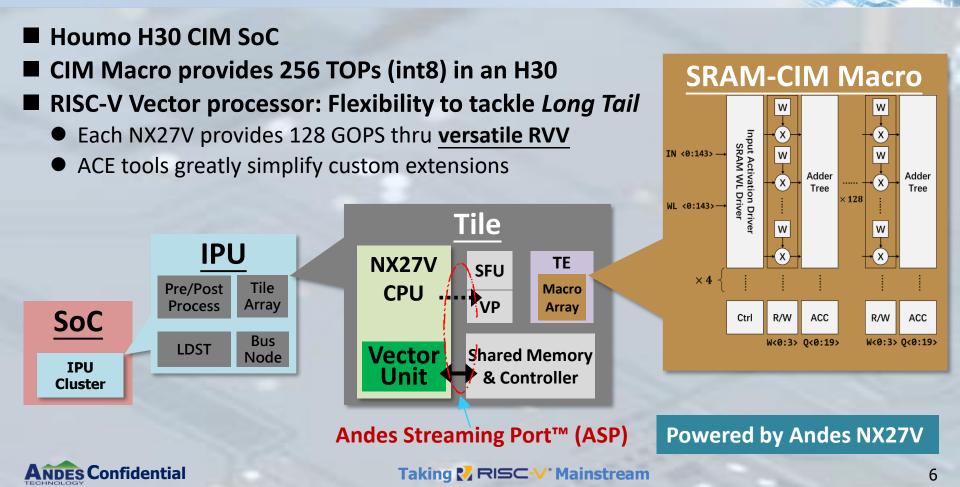

# **Compute-in-Memory (CIM) SoC**

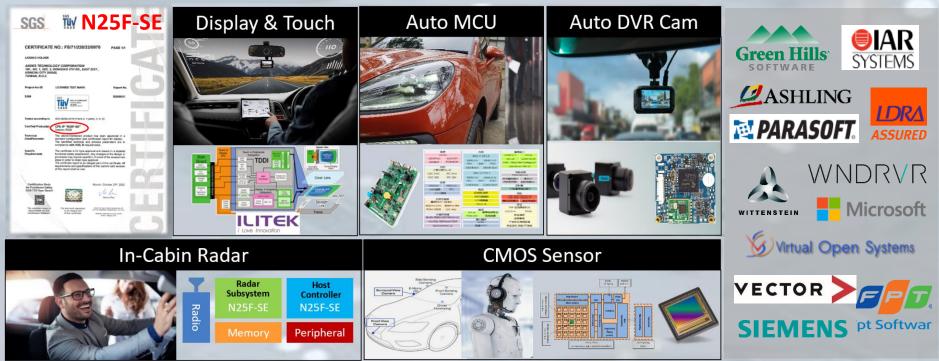

# **RISC-V Is Driving Innovations**

with Industry's 1<sup>st</sup> RISC-V ISO 26262 Fully Compliant Core, Andes N25F-SE

Isn't possible without partners for compilers, tools and RTOS/AutoSAR

### Taking 🛃 🛛 🖓 🖓 Taking 🛃 🖓

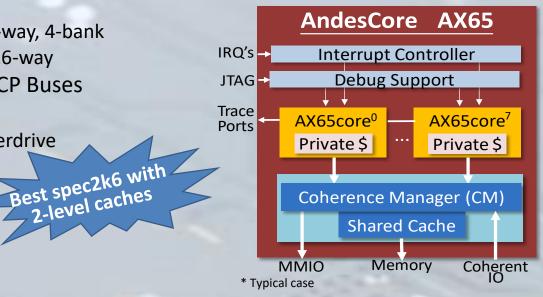

# AndesCore<sup>™</sup> AX65 OOO Application Processor

- 13-stage 4-way 64-bit OOO processor

RVA22 profile

- Multicore cluster up to 8 cores

- 8 Execution Pipes: 4 ALU, 2 LD/ST, 2 FP

- 2-Level BTB with TAGE-L Branch Predictor

• Caches:

- Private I/D caches: 64 KB, 4-way, 4-bank

- Shared cache: up to 8 MB, 16-way

- 256-bit AXI4, MMIO and IOCP Buses

- Performance:

- 2.4 GHz<sup>\*</sup> @7nm without overdrive

- Specint2006: 8.25/GHz

- Specfp2006: 10.2/GHz

• AX67:

- Further performance boost

- RVA23 (or RVA24)

| <u>B1 F1 F2</u>                 | <u>D1 D2 D3</u> | <u>I1</u>                  | <u>12</u>  | <u>E1</u>      | <u>E2</u> | <u>E3</u> | <u>E4</u> |    |  |

|---------------------------------|-----------------|----------------------------|------------|----------------|-----------|-----------|-----------|----|--|

|                                 |                 |                            |            | ALU            | WB        | x3        |           |    |  |

| batch, fetch,<br>align & buffer | decode, rename, | issue,<br>register<br>read | +br & misc |                | WB        | x1        |           |    |  |

|                                 | dispatch        |                            | m e        | mo             | r y       | WB        | x2        |    |  |

|                                 |                 |                            |            | floating point |           | nt        | WB        | x2 |  |

Taking 🔀 RISC-V\* Mainstream

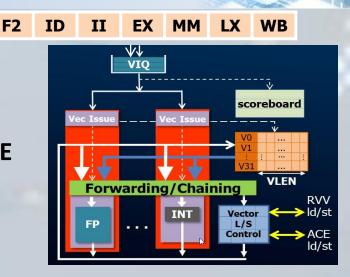

# **AX45MPV: 1024-bit Vector Processor**

### RISC-V Vector Extension (RVV v1.0)

- data format: int8~64, fp16~64; int4, bf16

- VLEN/DLEN: 128~1024 bits, 1:1 or 2:1 ratio

- Up to 6 DLEN results per cycle

## Efficient support needed for tight coupling with HWE

Data exchange performance (from/to shared memory in HWE)

Efficient control to the HWE

# 2 solutions offered in AX45MPV:

- Andes Streaming Port<sup>™</sup> (ASP) thru ACE

- Data bus: data transfer btw VR and HWE

- Command bus: to control/synchronize HWE operations

- HVM: High-speed Vector Memory

- CPU side: DLEN-wide load/store interface with dynamic wait cycles

- HVM module: accepting multiple accesses to multi-bank SRAM's

Andes Vector Core Memory Scalar A Subsys. Scalar A V P U P HVM

### Taking 🔀 RISC-V° Mainstream

**F1**

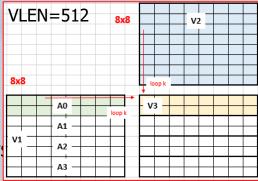

# **Matrix Multiplication Extension**

- To speed up MatMult

- Some common goals:

- High compute-to-memory ratio

- Leading to high MAC utilization

- Input/output registers: existing VRF and/or new (matrix) registers

- Scalability: VLEN-agnostic at the binary or source level

- Less-addressed issues:

- Matrix register file: more usage to be explored if used

- Boundary-case handling: several instructions needed to compute 2D mask

**VLEN 128**

Solutions to enable both inner-product or outer-product based computation sequence to defer the cost/performance tradeoff (from IP to IC)

VLEN=256

# **RISC-V Continues to ARISE Rapidly**

- RISE: RISC-V Software Ecosystem, a project under LF Europe

- To accelerate the development of RISC-V open source SW

- Led by industry leaders

- Areas to focus over time:

- Compilers & Toolchains

- Language Runtimes

- System Libraries

- Debug & Profiling Tools

- Simulator/Emulators

- Kernel and Virtualization

- Linus Distro Integration

- System Firmware

- More at https://riseproject.dev

# PRISC L Thank You !