## RISC-V in China: Embracing the Era of Open-Source Chip

Yungang Bao BOSC/ICT,CAS June 7, 2023

RISC-V Summit Europe 2023, 5-9 June 2023, Barcelona, Spain

## **Outline**

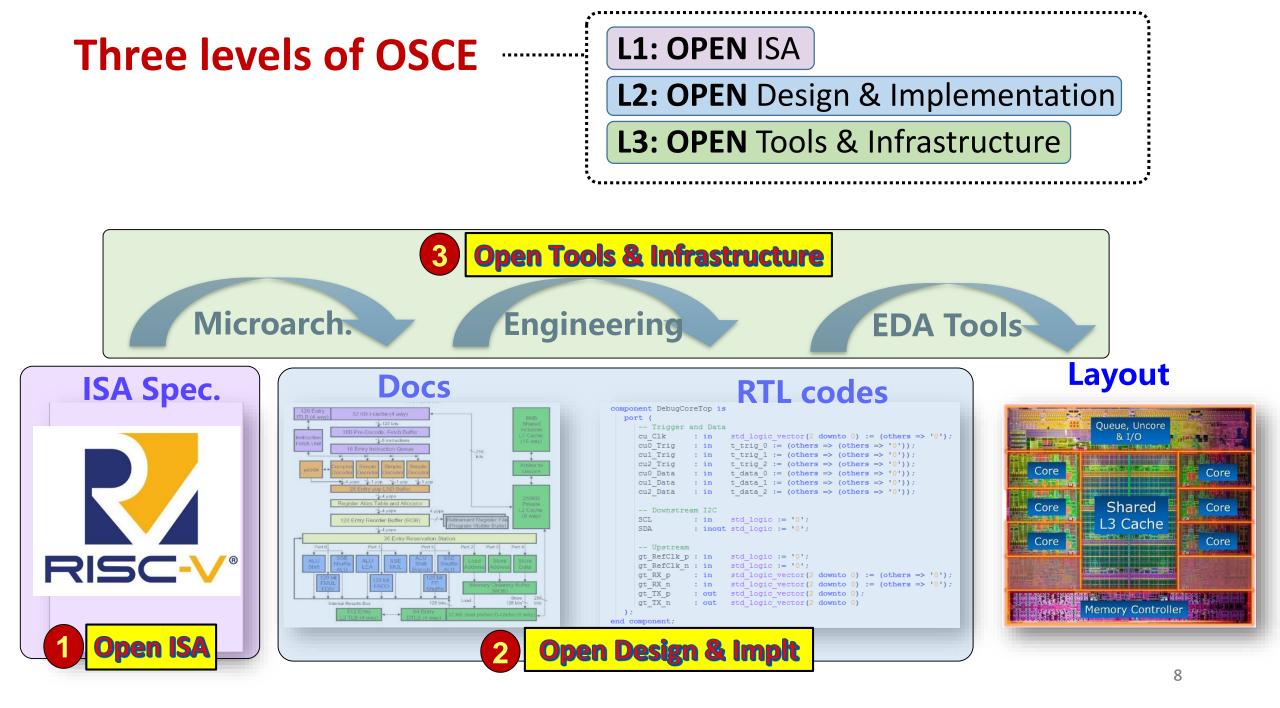

- Part I: Open-Source Chip Ecosystem (OSCE)

- Part II: RISC-V in China

- Part III: Progress in Building OSCE

## Part I

## **Open-Source Chip Ecosystem (OSCE)**

## **Three Dark Clouds Over the Chip Design Area**

## There are three dark clouds

- I. Moore's Law is ending

- II. Fragmentation in IoT is coming

- III. Global supply chain crisis is appearing

## • We need innovation to counteract the dark clouds

- Leverage HW-SW co-design & domain-specific architecture (DSA)

- Develop agile chip design methodology

- Build an open & shared ecosystem

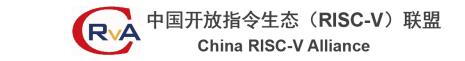

## **High Cost of Innovation for Chip Design**

Serge Leef, DARPA, Automatic Implementation of Secure Silicon, SIGARCH Visioning Workshop, 2019

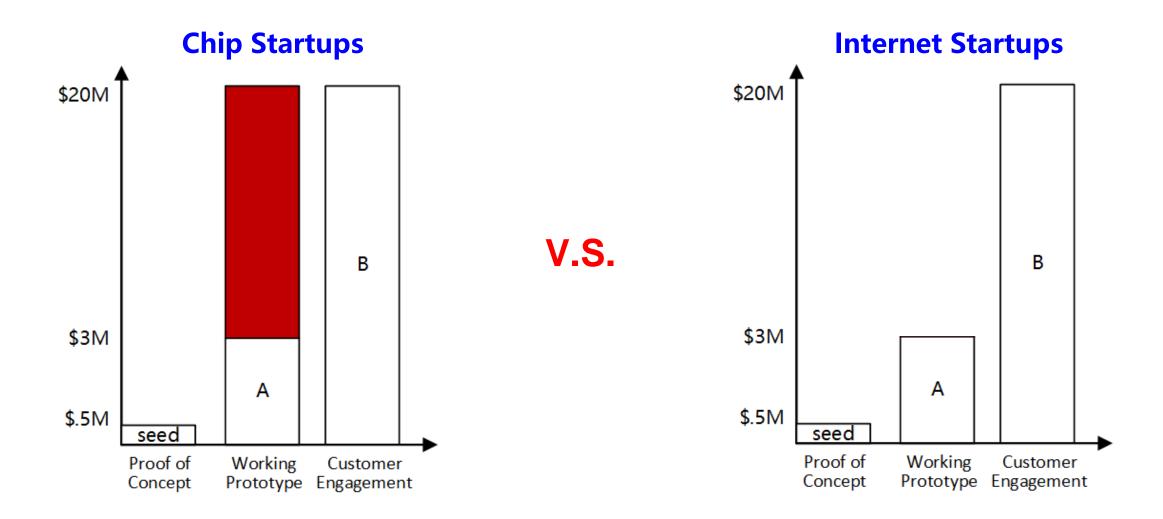

## Impact of Open-Source Software Ecosystem (OSSE)

## OSSE lowers the cost of innovation

- A small group (3-5 engineers) can build a mobile App prototype in 3-5 months

- There were 8.9 million mobile Apps by 2020

Image Source: <u>https://blogginbryan.wordpress.com/2020/02/11/7-</u> features-of-highly-successful-mobile-apps/

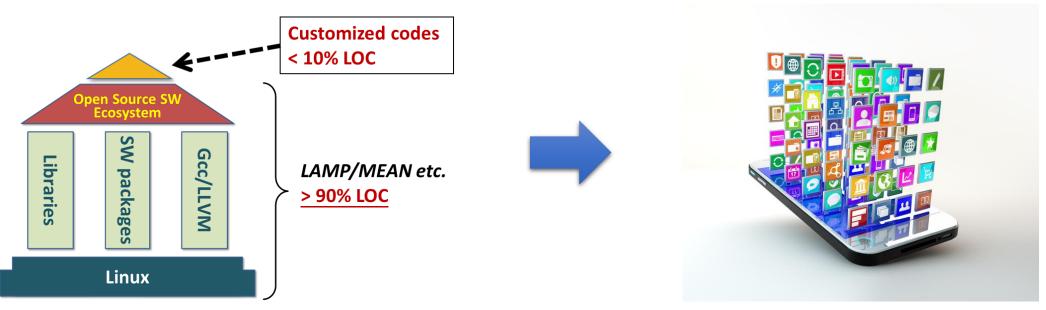

## **Open-Source Chip Ecosystem (OSCE)**

- Lower the barrier of chip development

- Save time-to-market and the cost of IPs, EDA tools and engineers

## Lessons from an unborn "national ISA"

- Various ISAs (Alpha, MIPS, PowerPC, SPARC, X86 etc.) were adopted in China around 2010

- In 2012, MIIT proposed to merge these ISAs into a unified ISA

- Hard to reach a consensus:

- Choose an existing ISA or design a new ISA?

- Which ISA to be chosen?

- Who own the unified ISA?

## RISC-V's answer:

### "ISAs should be free!"

## Part II

**RISC-V** in China

## **Timeline of RISC-V in China (partial)**

- 2015, Chinese version position paper was published on CCCF

- 2015, organizations became the founding members of RISC-V Foundation

- 2016, scholars present research work at the 4<sup>th</sup> RISC-V Workshop

- 2017, the 6<sup>th</sup> RISC-V Workshop was held in Shanghai

- 2018, CRVA and CRVIC were founded

- 2018, Alibaba/T-Head (BoD) and many RISC-V startups were founded

- 2019, CAS launched a project to promote RISC-V in China

- 2019, RIOS Lab was established (BoD)

- 2020, the 1<sup>st</sup> "One Student One Chip" Initiative was announced

- 2021, the 1<sup>st</sup> RISC-V Summit China was held

- 2021, Allwinner D1, XiangShan v1 and other ten RISC-V chips released

- 2021, BOSC (BoD) was founded

- 2022, more and more companies chose RISC-V, such as Tencent

- 2022, eleven RISC-V chips released

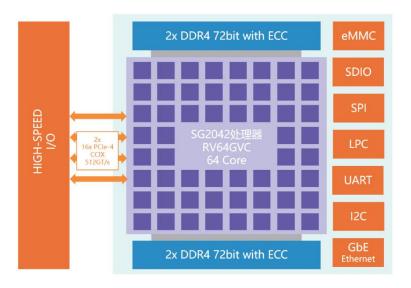

- 2023, Sophon announced 64-core RISC-V processor SG2042

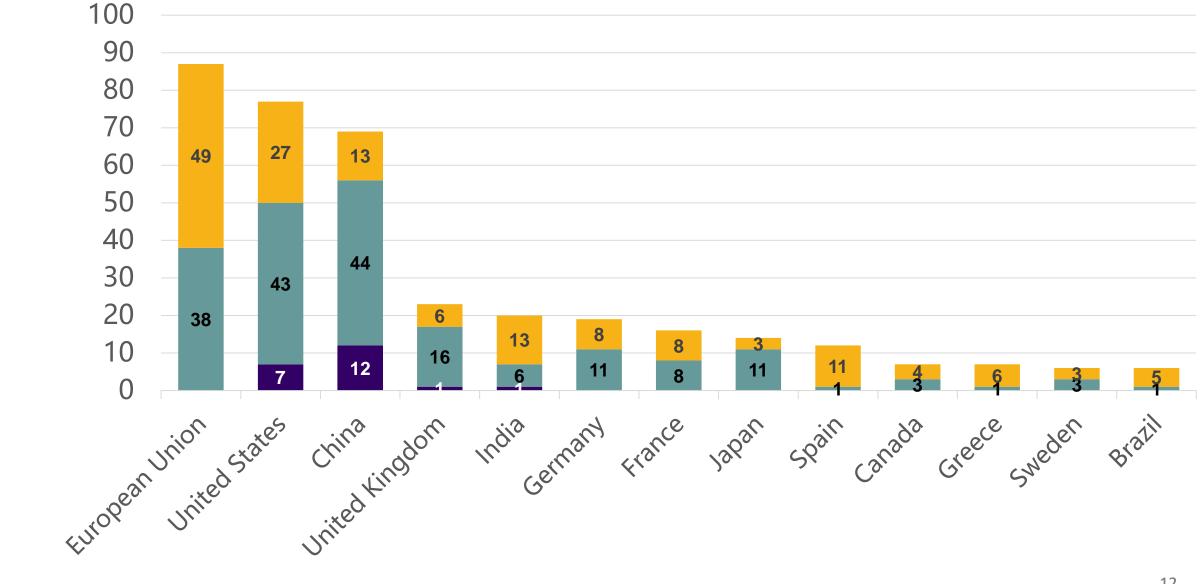

## Members of RISC-V International

Strategic Members

**Community Organization Members**

12

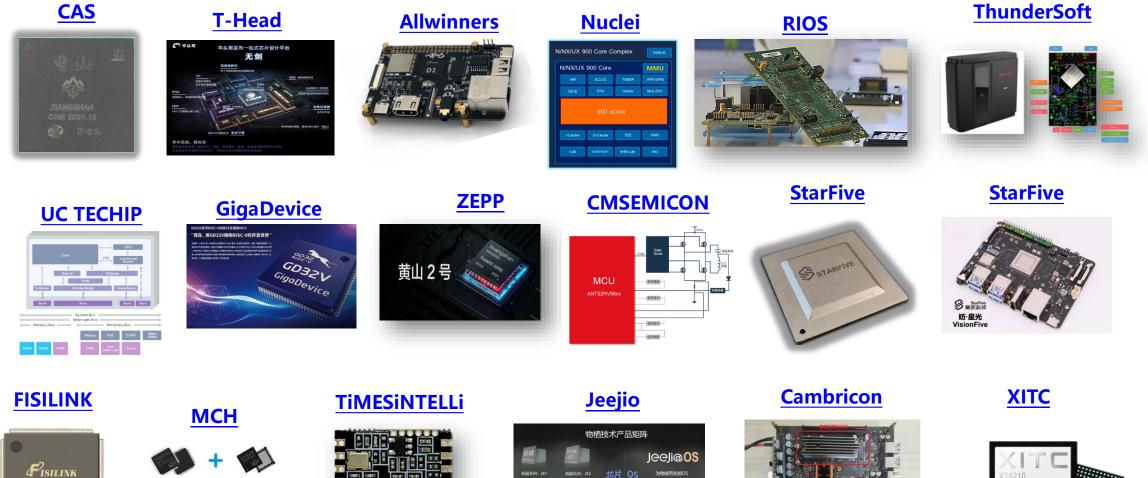

## **RISC-V Startups in China**

| Company    | <b>Round of Financing</b> | Total number of<br>financing | Total financing<br>amount (Million \$) |

|------------|---------------------------|------------------------------|----------------------------------------|

| Company-1  | С                         | 4                            | <b>916.2</b>                           |

| Company-2  | A+                        | Many times                   | 140.8                                  |

| Company-3  | D                         | 6                            | 34.5                                   |

| Company-4  | B+                        | 3                            | 27.9                                   |

| Company-5  | А                         | 5                            | 20.0                                   |

| Company-6  | A                         | 1                            | 14.1                                   |

| Company-7  | PreA+                     | 3                            | 14.1                                   |

| Company-8  | B+                        | 2                            | 7.0                                    |

| Company-9  | Angel Round               | 1                            | 2.8                                    |

| Company-10 | Pre-A                     | 1                            | 2.8                                    |

| Others     | -                         | —                            | Undisclosed                            |

|            |                           |                              | > 1180                                 |

## **RISC-V CPU IPs are widely adopted**

RISC-V通用工业级MCU RISC-V低功耗益牙MCU

RISC-V通用工业级无线型MCU 赤菟V208

## High performance RISC-V Chips (SOPHGO)

- 64 RISC-V cores (T-Head XuanTie C920) running at up to 2GHz

- Buy motherboard suites from Taobao (1000-1400 USD)

- SOPHGO donated 50 motherboards to RVI

## **Efforts in RISC-V Software Ecosystem**

#### **Compiler & Studio**

#### **HPC Platform**

#### **Compiler IDE**

| 卡姆派乐 RISCV IDE                           |

|------------------------------------------|

|                                          |

| 国内首款RISEV集成开发环境,型于图形化界面,一键式支装,主<br>要特点:  |

| ◇ 编译器支持代码长度优化:二进制代码长度比公版优化10-30%;        |

| ◇ 启动速度快、功能强大、界面简洁清晰;                     |

| ◇ 集成SPIKE模拟器;                            |

| ◇提供中英文两个版本;                              |

| ◇功能可定制:可以根据用户体系结构的需求,提供编译器、调试器<br>等定制服务; |

| ◇ 支持WINDDWS和LINUX操作系统。                   |

#### **OS for RISC-V**

| Tasks  | 89 total.   | 11       | une. | ina. | 88 5  | leeping         | . 0    | tonned | . 0 zo  | shie                              |                           |

|--------|-------------|----------|------|------|-------|-----------------|--------|--------|---------|-----------------------------------|---------------------------|

| Mem    |             | total    |      | 1437 | 12K u | sed.            | 72580  | free.  |         | 12 buffers                        |                           |

| Swap:  |             | total    |      |      | 0 u   | sed.            |        | free.  |         | 68 cached                         |                           |

| 100%cc | u 3luser    | 0%       | ice  | 31   | svs . | 95%idle         | 0%14   | W 0%   | iro 0%  | sirg Olhost                       |                           |

| PID    | USER        | PR       | NI   | VIRT | RES   | SHR S           | INCPUT | MEN    | TIME+   | ARGS                              |                           |

|        | root        | 20       |      |      |       | 1.8M R          |        | 0.2    | 0:04.65 |                                   |                           |

|        | system      |          |      |      | 36M   | 29M S           | 1.3    | 3.6    |         | foundation                        |                           |

|        | system      |          |      |      | 138   | 11M S           | 1.0    | 1.2    |         | distributeddata                   |                           |

|        | Logd        |          |      |      |       | 1.7M S          | 0.6    | 0.5    | 0:02.92 |                                   |                           |

| 107    |             |          |      |      |       | 872K S          | 0,6    | 0.1    | 0:00.73 |                                   |                           |

| 108    | system      |          |      |      |       | 6.1M S          | 0.3    | 0.7    |         | accountegr                        |                           |

|        | system      |          |      |      |       | 4.4M S          | 0.0    | 0.5    | 0:00.12 | audio_policy                      |                           |

|        |             |          |      |      |       | 2.0M S          | 0.0    | 0.2    | 0:00.03 |                                   |                           |

|        | system      |          |      | 23M  |       | 12M S           | 0.0    | 1.4    |         | time_service                      |                           |

| 219    | system      |          |      |      |       | 11M S           | 0.0    | 1.3    | 0:00.63 | telephony                         |                           |

| 209    |             |          |      |      |       | 4.5M S          | 0.0    |        | 0:00.13 | medialibrary_se                   |                           |

|        | system      | 20<br>20 | 0    |      | 14M   | 4.9M S<br>12M S | 0.0    | 0.5    |         | media_service                     |                           |

|        | cameraserve |          | ŏ    |      |       | 4.581 5         | 0.0    | 0.5    | 0:00.76 | inputmethod_ser<br>camera service |                           |

|        | root        | 20       | ă    |      |       | 6.8M S          | 0.0    | 0.7    |         | vifi manager se                   |                           |

|        | system      | 20       | ŏ    |      |       | 15M 5           | 0.0    | 1.7    | 0:00.23 | softbus server                    |                           |

| 170    | system      | 20       | ŏ    |      |       | 4.5M S          | 0.0    | 0.5    |         | pulseaudio                        |                           |

| 172    | system      | 20       |      | 100  | 5     | 4.6M S          | 0.0    | 0.5    |         | huks service                      |                           |

|        | system      | 20       |      |      |       | 5.2M S          | 0.0    | 0.6    | 0:00.15 |                                   |                           |

| 143    | root        | 20       |      |      |       | 3.5H S          | 0.0    | 0.4    |         | sample host hdf devhos            | t 0 sample host           |

| 142    | reet        | 20       |      |      |       | 3.58 5          | 0.0    | 0.4    |         | usbfnMaster host evhost           |                           |

| 141    | rest        | 20       |      | 8.8M | 4.38  | 3.5M S          | 0.0    | 0.4    | 0:00.11 | power host 7hdf devhost           | t 2 power host            |

|        | reat        | 20       |      | 8.6M | 4.38  | 3.6M S          | 0.0    | 0.4    | 0:00.12 | wifi host n/hdf devhost           | t 3 wifi host             |

|        | root        | 20       |      | 8.84 | 4.3M  | 3.5M S          | 0.0    | 0.4    |         | wifi_c_host hdf_devhost           |                           |

|        | rost        | 20       |      |      |       | 3.5M S          | 0.0    | 0.4    |         |                                   | t S audio_hdi_server_host |

|        | root        |          |      |      |       | 3.6M S          | 0.0    | 0.4    |         | camera_host hdf_devhost           |                           |

| 134    |             |          |      |      |       | 3.5M S          | 0.0    | 0.4    |         | input_user_host devhost           |                           |

| 133    |             |          |      |      |       | 3.6M S          | 0.0    | 0.4    | 0:00.12 | codec_host /hdf_devhost           | t 8 codec_host            |

|        |             |          |      |      |       | 3.6M S          |        |        |         | riladapter_host devhost           | t 9 riladapter_host       |

|        |             |          |      |      |       | 3.5M S          | 0.0    | 0.4    |         | hdf_devngr                        |                           |

|        | system      |          |      |      |       | 1.8M S          | 0.0    |        |         | faultloggerd                      |                           |

| 120    | system      |          |      |      |       | 7.1M \$         | 0.0    |        | 0:00.27 | distributedsche                   |                           |

| 119    | root        |          |      | 3.14 | 1.24  | 872K S          | 0,0    |        | 0:00.25 | udevd                             |                           |

#### **Simulator**

#### ....

## **Contributions from China to the RISC-V Ecosystem**

- AOSP RISC-V (upstreaming): main contributors (Alibaba T-Head, PLCT Lab@ISCAS, ESWIN, ...)

- **OpenJDK RISC-V** (upstreamed): main contributors & port maintainers (Huawei, Aliababa, PLCT Lab@ISCAS, ...)

- V8 RISC-V (upstreamed): main contributors & port maintainers (PLCT Lab@ISCAS), FutureWei, ...)

- Firefox Spidermonkey RISC-V backend (upstreamed): key contributors & port maintainers (PLCT Lab@ISCAS)

- GNU Toolchain, Clang/LLVM, MLIR, QEMU, Spike, Gem5: active contributors (RiVAI, Alibaba, PLCT Lab@ISCAS, Huawei, WindRiver, Tsinghua, ...)

- **Chisel:** active contributors & maintainers (PLCT Lab@ISCAS)

- **OpenCV RISC-V Vector Optimization**: key contributors (PLCT Lab@ISCAS)

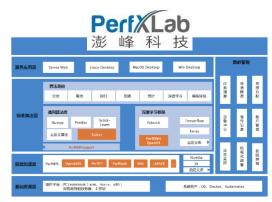

- **OpenBLAS RISC-V Arch**: key contributors & maintainers (PerfXLab, ...)

- **Box64**: key contributors (PLCT Lab@ISCAS)

- LualIT: contributors (PLCT Lab@ISCAS)

•

.....

- **Debian** (RISC-V port): many active contributors (PLCT Lab@ISCAS, ...)

- Fedora (RISC-V port): many active contributors (RedHat, PLCT Lab@ISCAS, ...)

- Arch Linux (RISC-V port): main contributors & maintainers (PLCT Lab@ISCAS, ...)

- **Gentoo Linux** (RISC-V port): main contributors & core developers (PLCT Lab@ISCAS, ...)

- openEuler (RISC-V): key contributors & maintainers (PLCT Lab@ISCAS, ...)

## **Research & Education**

- MOST and NSFC are inviting proposals for RISC-V related research

- More and more universities use RISC-V for teaching

Textbook @ NJU

#### One-Student-One-Chip @UCAS

## Part III

## **Progress in Building OSCE**

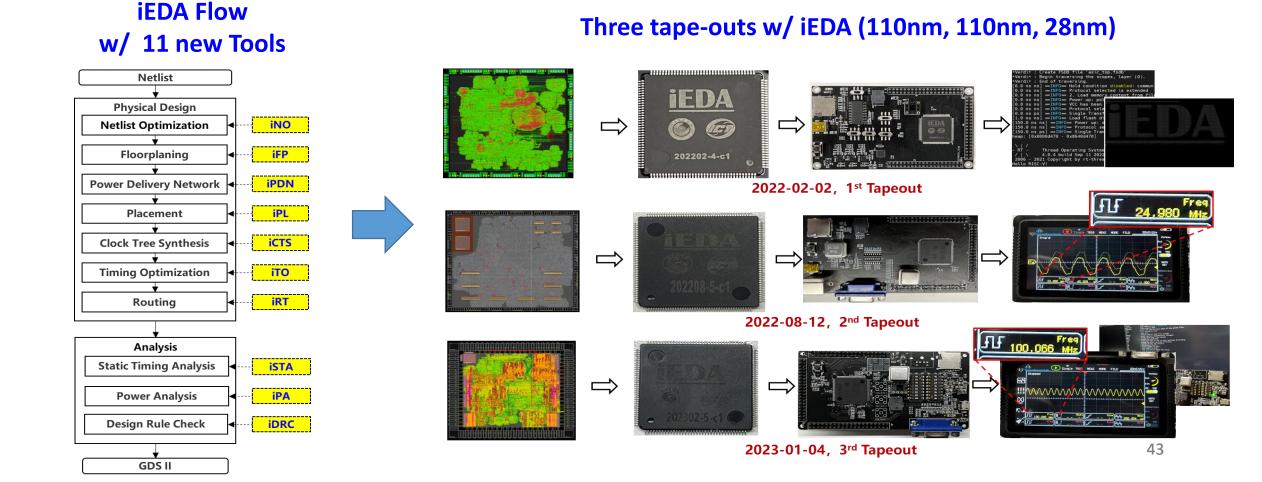

## The "3-Step Plan" towards OSCE (by 2030)

- When China RISC-V Alliance (CRVA) was founded in 2018, we also put forward the "3-Step Plan":

- <u>Step 1</u>: Provide silicon-proven opensource RISC-V IPs & SoCs (3-5 years)

- <u>Step 2</u>: Develop open-source SoCs by open-source EDA tools (5-7 years)

- <u>Step 3</u>: Build open-source hardware automatically by open-source EDA tools (10-15 years)

#### 2030"三步走"规划

- 第一步:开源SoC——用3-5年为社区提供经过流片验 证的高质量RISC-V开源核、开源SoC设计

- RISC-V处理器核IP、外围IP等

- 第二步:用开源工具链构建开源SoC——用5-7年逐步 构建一套基于开源EDA工具链、开源IP、开源工艺库的 开源SoC芯片设计流程

- 将商业版工具、IP逐渐替换为开源版

- 实现本科生用全开源工具开发开源芯片,带着自己芯片毕业

- 第三步:用开源工具链自动化构建开源硬件——用10-15年开发更智能、更自动化的开源工具,提高设计验证 效率

- 形成开源芯片生态,降低芯片开发门槛

## **An overview of Work-in-Progress**

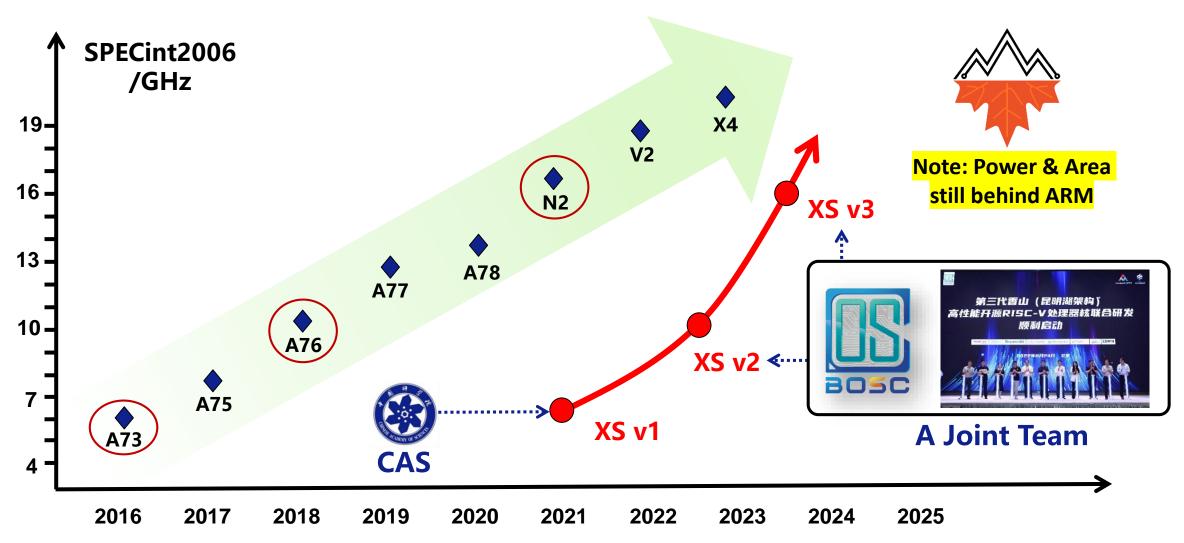

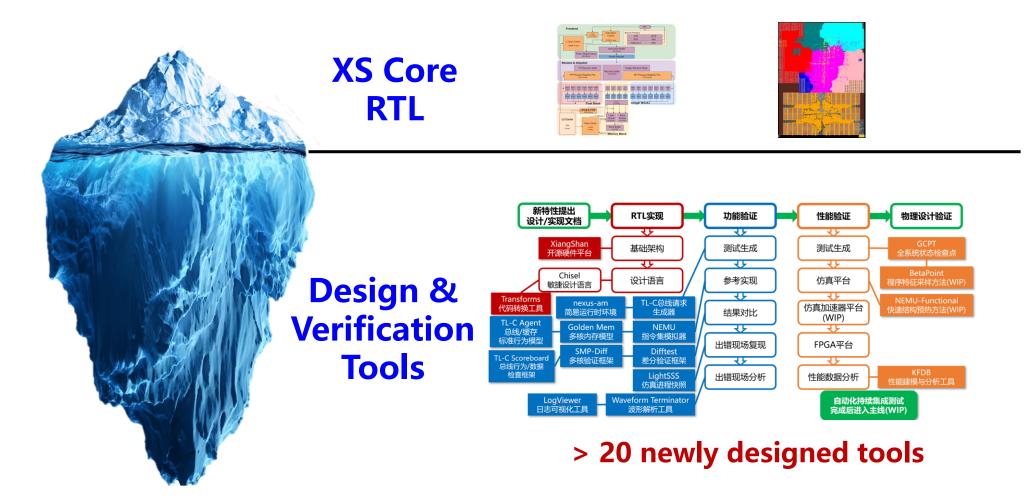

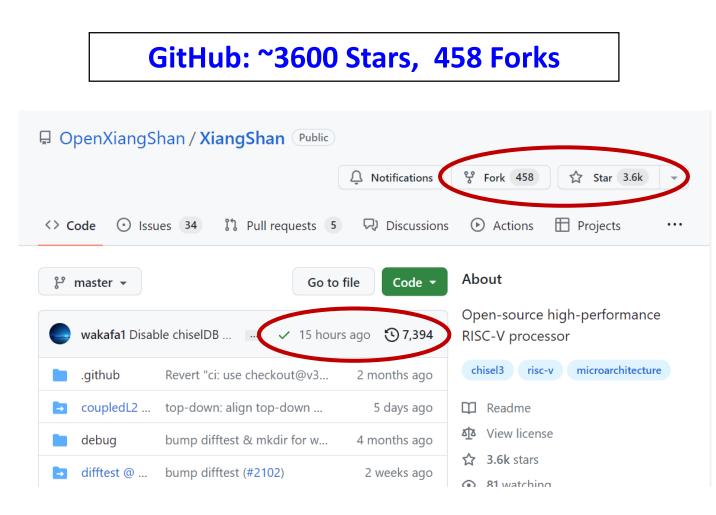

## XiangShan (XS): Open-Source High Performance RISC-V Core

## XiangShan v1 (Yanqihu)

- RV64GC, 11-stage, 6-issue, out-of-order

- The real chip was back in January 2022

- SoC: CPU, SPI Flash, UART, SD card, Ethernet, DIMM

- Correctly running Debian with SD card and ethernet

#### SPECint 2006: 7.03@1GHz SPECfp 2006: 7.00@1GHz

| SPECint 2006   | @ 1GHz | SPECfp 2006 @ 1GHz |       |  |

|----------------|--------|--------------------|-------|--|

| 400.perlbench  | 6.14   | 410.bwaves         | 9.28  |  |

| 401.bzip2      | 4.37   | 416.gamess         | 6.59  |  |

| 403.gcc        | 6.71   | 433.milc           | 8.41  |  |

| 429.mcf        | 6.83   | 434.zeusmp         | 7.65  |  |

| 445.gobmk      | 7.92   | 435.gromacs        | 4.99  |  |

| 456.hmmer      | 5.24   | 436.cactusADM      | 3.97  |  |

| 458.sjeng      | 6.85   | 437.leslie3d       | 6.93  |  |

| 462.libquantum | 17.71  | 444.namd           | 8.00  |  |

| 464.h264ref    | 10.91  | 447.dealII         | 10.17 |  |

| 471.omnetpp    | 5.65   | 450.soplex         | 7.03  |  |

| 473.astar      | 5.16   | 453.povray         | 7.14  |  |

| 483.xalancbmk  | 7.35   | 454.Calculix       | 2.86  |  |

|                |        | 459.GemsFDTD       | 8.35  |  |

|                |        | 465.tonto          | 6.42  |  |

|                |        | 470.lbm            | 10.39 |  |

|                |        | 481.wrf            | 7.26  |  |

482.sphinx3

9.07

#### SSH into the Debian on XiangShan, and run a GUI program via X11 forwarding

#### wanghuizhe@open02:~\$ ssh -X xs@172.28.2.246 xs@172.28.2.246's password: Linux open02 4.20.0-44668-ge9c195ab0c63-dirty #109 Thu Feb 17 17:41:13 CST 2022 circle The programs included with the Debian GNU/Linux system are free software; the exact distribution terms for each program are described in the individual files in /usr/share/doc/\*/copyright. Debian GNU/Linux comes with ABSOLUTELY NO WARRANTY, to the extent permitted by applicable law. You have no mail. Last login: Thu Feb 17 11:10:31 2022 from 172.28.9.102 xs@open02:~\$ xclock Warning: locale not supported by C library, locale unchanged

Х

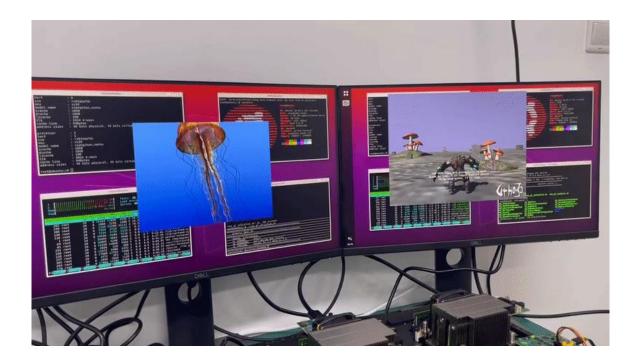

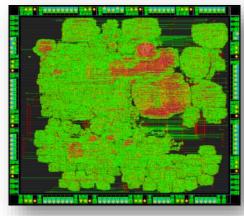

## XiangShan v2 (Nanhu)

• Target performance: 2GHz@14nm, SPEC CPU2006 10/GHz (> ARM Cortex-76), 40% improvement over XS v1

18.049

• Note: power and area are still poorer than Cortex-A76

#### **SPECint 2006: 9.55/GHz** SPECfp 2006: 11.09/GHz

SPE

| ********SPECINT2006 | *****  | ********SPECFP2006******** |       |  |

|---------------------|--------|----------------------------|-------|--|

| 400.perlbench       | 19.291 | 410.bwaves                 | 18.04 |  |

| 401.bzip2           | 11.348 | 416.gamess                 | 23.82 |  |

| 403.gcc             | 21.971 | 433.milc                   | 18.32 |  |

| 429.mcf             | 20.509 | 434.zeusmp                 | 28.1  |  |

| 445.gobmk           | 15.981 | 435.gromacs                | 17.53 |  |

| 456.hmmer           | 19.222 | 436.cactusADM              | 24.22 |  |

| 458.sjeng           | 17.203 | 437.leslie3d               | 20.27 |  |

| 462.libquantum      | 36.989 | 444.namd                   | 23.83 |  |

| 464.h264ref         | 28.542 | 447.dealll                 | 33.50 |  |

| 471.omnetpp         | 14.009 | 450.soplex                 | 25.6  |  |

| 473.astar           | 14.196 | 453.povray                 | 27.05 |  |

| 483.xalancbmk       | 21.522 | 454.Calculix               | 9.18  |  |

| SPECint2006@2GHz    | 19.099 | 459.GemsFDTD               | 24.63 |  |

| SPECint2006/GHz     | 9.549  | 465.tonto                  | 17.66 |  |

| 3FEC///12000/8/12   | 9.549  | <u>470.lbm</u>             | 32.05 |  |

|                     |        | 481.wrf                    | 19.72 |  |

| *Evaluation On F    | PGA    | 482.sphinx3                | 28.35 |  |

|                     |        | SPECfp2006@2GHz            | 22.17 |  |

|                     |        |                            |       |  |

#### \*Evaluation On FPGA

| Silutoo      | 10.010 |

|--------------|--------|

| gamess       | 23.822 |

| .milc        | 18.328 |

| zeusmp       | 28.14  |

| gromacs      | 17.532 |

| .cactusADM   | 24.223 |

| leslie3d     | 20.272 |

| namd         | 23.837 |

| dealli       | 33.505 |

| soplex       | 25.64  |

| povray       | 27.055 |

| Calculix     | 9.185  |

| GemsFDTD     | 24.637 |

| tonto        | 17.669 |

| lbm          | 32.056 |

| wrf          | 19.728 |

| sphinx3      | 28.353 |

| Cfp2006@2GHz | 22.175 |

| Cfp2006/GHz  | 11.088 |

|              |        |

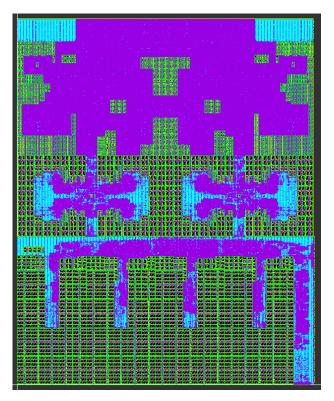

#### Layout of dual-core SoC

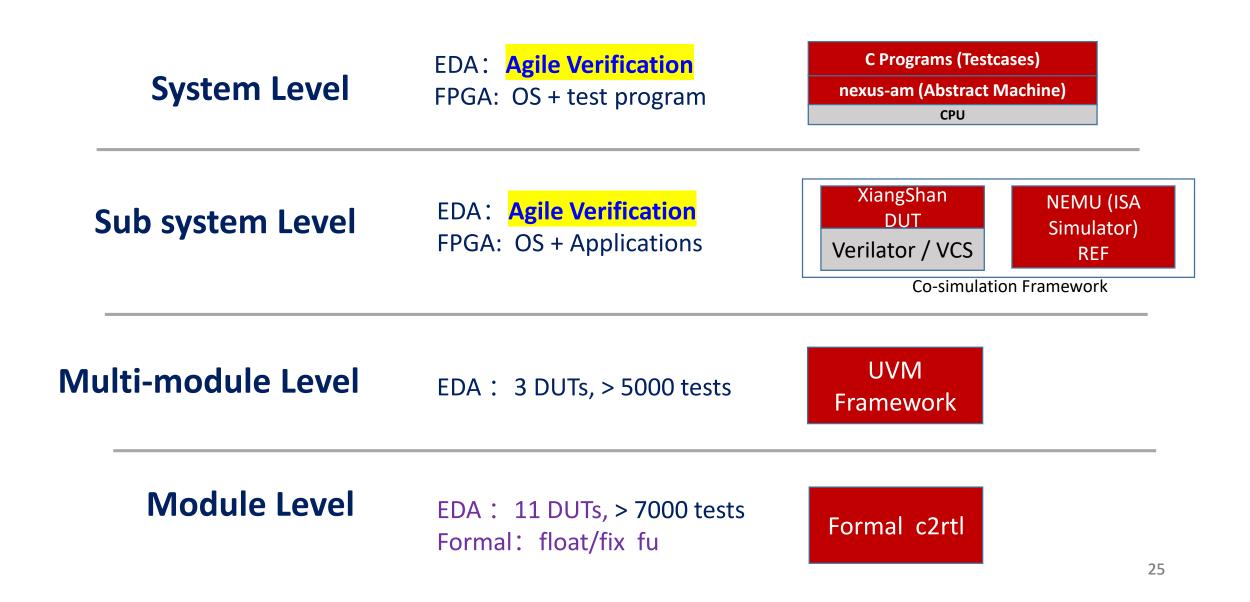

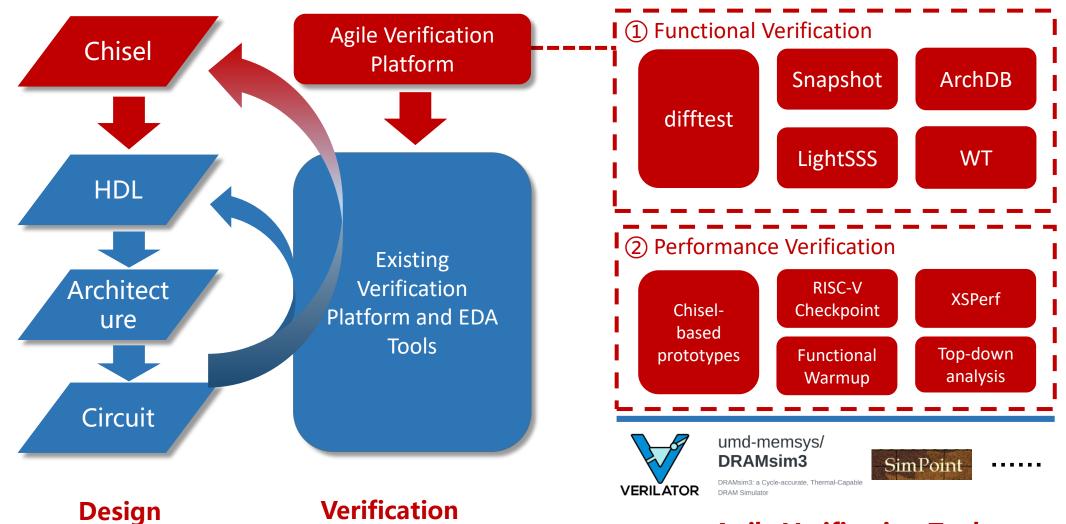

## Four Levels of Verification for XiangShan

## **Agile Verification Flow and Tools**

#### **Agile Verification Tools** 26

## **All Are Open-Sourced**

Published on MICRO'2022, selected as IEEE Micro Top Picks

## All Are Open-Sourced (cont.)

#### Nanhu Core Spec for Integration and Programming Guide

#### Contents

| 1 | Abou | t This D | اب                               |   |  |  |  |  |  |

|---|------|----------|----------------------------------|---|--|--|--|--|--|

|   | 1.1  | Revisio  | on History                       |   |  |  |  |  |  |

|   | 1.2  | Refere   | nces                             |   |  |  |  |  |  |

|   | 1.3  | Websit   | tes and Links                    |   |  |  |  |  |  |

|   | 1.4  | Termir   | nology                           |   |  |  |  |  |  |

| 2 | Nanh | u Core.  | Core                             |   |  |  |  |  |  |

|   | 2.1  | Nanhu    | CPU subsystem                    |   |  |  |  |  |  |

|   | 2.2  | Core F   | eature                           |   |  |  |  |  |  |

|   | 2.3  | Instruc  | ction set                        |   |  |  |  |  |  |

|   | 2.4  | Suppo    | rted privilege mode              |   |  |  |  |  |  |

|   | 2.5  | Manag    | ement Signals                    |   |  |  |  |  |  |

|   | 2.6  | CPU M    | icro Architecture                |   |  |  |  |  |  |

|   |      | 2.6.1    | CPU Execution Pipeline           |   |  |  |  |  |  |

|   |      | 2.6.2    | Load Store Unit                  |   |  |  |  |  |  |

|   |      | 2.6.3    | L1, L2 cache                     |   |  |  |  |  |  |

|   |      | 2.6.4    | L3 Cache                         |   |  |  |  |  |  |

|   |      | 2.6.5    | Atom operation                   |   |  |  |  |  |  |

|   |      | 2.6.6    | Hardware performance monitor     |   |  |  |  |  |  |

|   |      | 2.6.7    | Virtual memory support 21+       |   |  |  |  |  |  |

|   |      | 2.6.8    | Physical memory protection       |   |  |  |  |  |  |

| 3 | Nanh | u Integ  | ration Guide                     |   |  |  |  |  |  |

|   | 3.1  | AXI In   | AXI Interface                    |   |  |  |  |  |  |

|   |      | 3.1.1    | CPU Core Interfaces 31+          |   |  |  |  |  |  |

|   | 3.2  | Memor    | ry map                           |   |  |  |  |  |  |

|   | 3.3  | Clock a  | and Reset                        |   |  |  |  |  |  |

|   |      | 3.3.1    | clock and reset timing explained |   |  |  |  |  |  |

|   |      | 3.3.2    | Clock guidelines                 |   |  |  |  |  |  |

|   |      | 3.3.3    | SDC File                         |   |  |  |  |  |  |

|   | 3.4  | Memor    | ry & RF                          |   |  |  |  |  |  |

|   |      | 3.4.1    | Memory and RF description        |   |  |  |  |  |  |

|   |      | 3.4.2    | SRAM List                        |   |  |  |  |  |  |

|   |      | 3.4.3    | SRAM Multi-Cycle Clock Setup     |   |  |  |  |  |  |

|   | 3.5  | Clock I  | Description                      |   |  |  |  |  |  |

|   |      | 3.5.1    | Synchronizer instantiation       |   |  |  |  |  |  |

|   | 3.6  | Interru  | upt                              |   |  |  |  |  |  |

|   |      | 3.6.1    | Functional description 40+       | - |  |  |  |  |  |

|   |      |          |                                  |   |  |  |  |  |  |

## XiangShan is recognized and adopted by companies

## Already used (2022)

- 7nm SoC Testchip, tapeout

- 5nm Al Chip

## • Will use (2023)

- 28nm SoC Chip

- 16nm Testchip

- 12nm AI video chip

- 12nm Server CPU

- 7nm GPU

- 7nm DPU

- 7nm Server CPU

A startup (Xinchen Technology) took only two weeks to integrate dual XS cores into an SoC and run on FPGAs

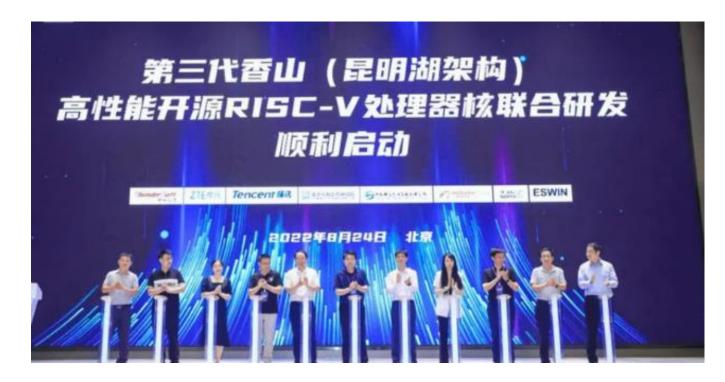

## A Joint Team for XiangShan v3

- About 10 companies

- Target ARM Neoverse N2

- SPECCPU2006: 45 @ 3GHz (15/GHz)

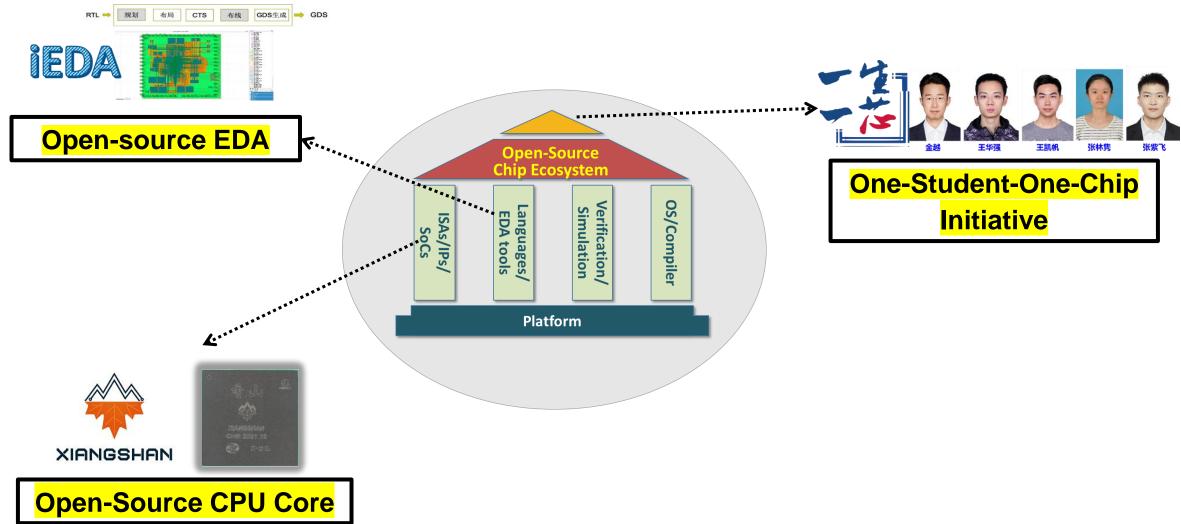

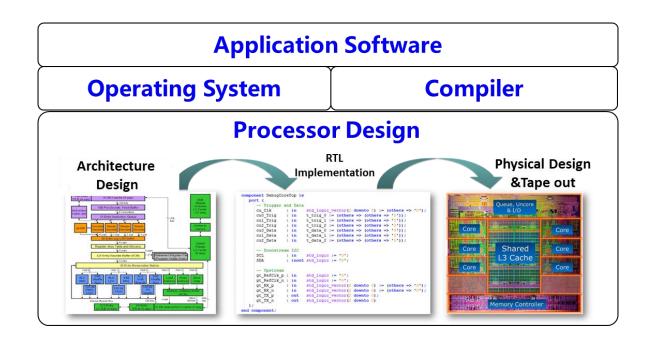

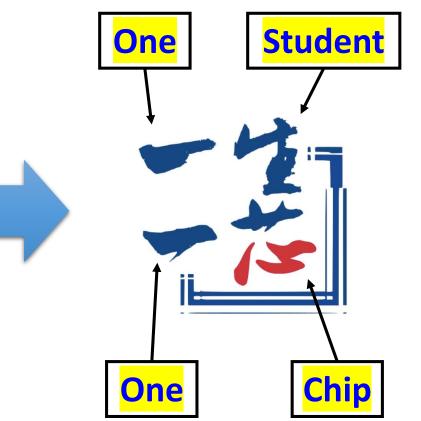

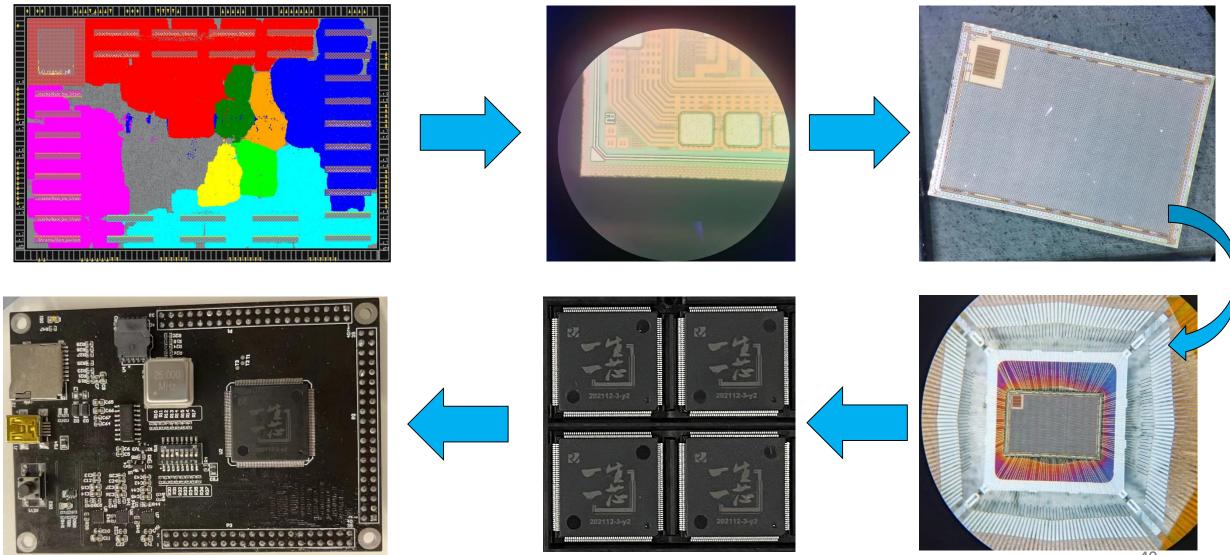

## The One Student One Chip (OSOC) Initiative

- Learning-by-Doing: Teach undergraduates to build real chips

- Launched the OSOC Initiative in 2019

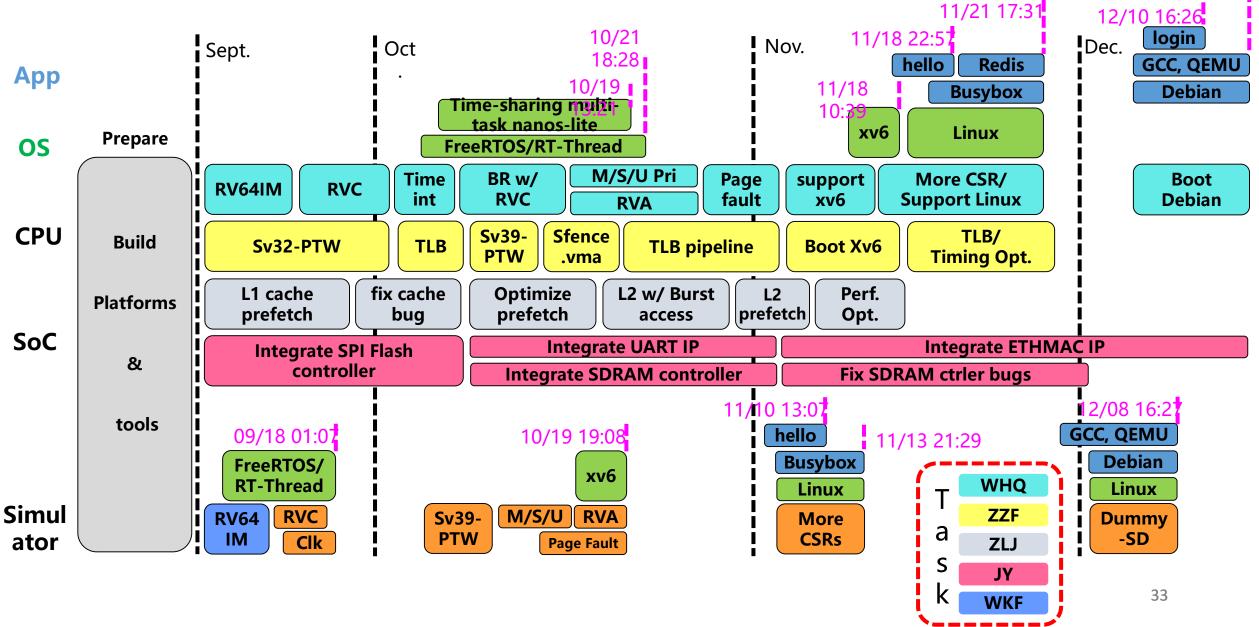

## The 1st OSOC (2019)

- Five senior undergraduates participated

- Completed the design of a 64-bit RISC-V processor in four months

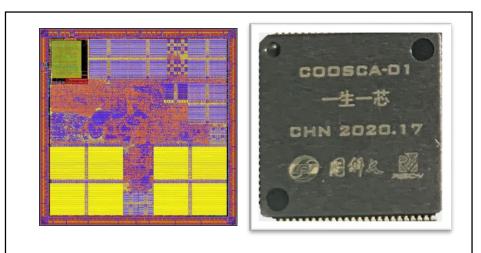

- The chip was taped out with 110nm and ran Linux and a self-built UCAScore OS

Yue Jin

Huangqiang Wang

**Kaifan Wang**

**Linjuan Zhang**

Zifei Zhang

## **4-month Development**

12/13 14:26

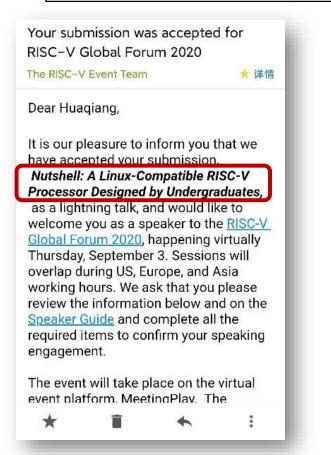

# NutShell: A Linux-Compatible RISC-V Processor Designed by Undergraduates

## A 64-bit RISC-V Processor

- Single-issue, 9-stage, in-order

- RV64IMAC, support M/S/U

- 2-bit BPU, 512 BTB, 16 RAS

- Sv39, hardware TLB refill

- 32K L1I & L1D

- Read consistency for L1I & L1D

- 128K L2 cache, next line prefetch

- Use Chisel

- SDRAM, SPI flash, UART

- Support Linux 4.18.0 kernel

- Support Busybox

- Can run Debian 11 on Emulator & FPGA

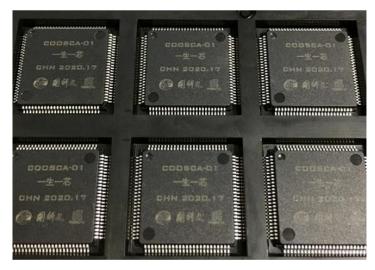

## Tape-out w/ 110nm-node

- 110nm

- 10mm<sup>2</sup>

- 200mw@350MHz Typical

- TQFP100 package

## **Real Chips**

#### Chips

#

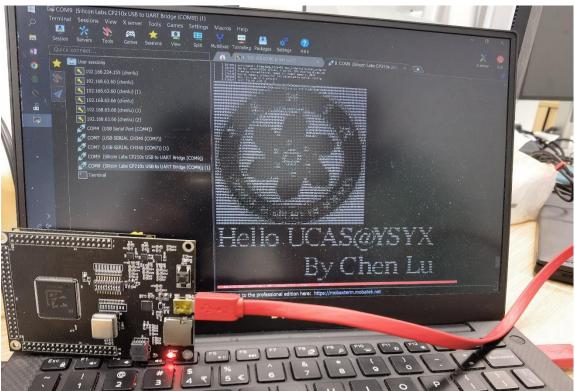

#### Run Linux Display CAS logo

#### Frequency: 350MHz

| 配置开关 | 倍率   | 50MHz晶振  | 100MHz晶振 |

|------|------|----------|----------|

| 000  | 1    | 50MHz    | 100MHz   |

| 001  | 1.5  | 75MHz    | 150MHz   |

| 010  | 2    | 100MHz   | 200MHz   |

| 011  | 2.5  | 125MHz   | 250MHz   |

| 100  | 2.75 | 137.5MHz | 275MHz   |

| 101  | 3    | 150MHz   | 300MHz   |

| 110  | 3.5  | 175MHz   | 350MHz   |

| 111  | 4    | 200MHz   | 400MHz   |

#### Demo

## Theis Defense 2020.6.2

## Accepted to RISC-V Global Forum 2020

## NutShell: A Linux-Compatible RISC-V Processor Designed by Undergraduates

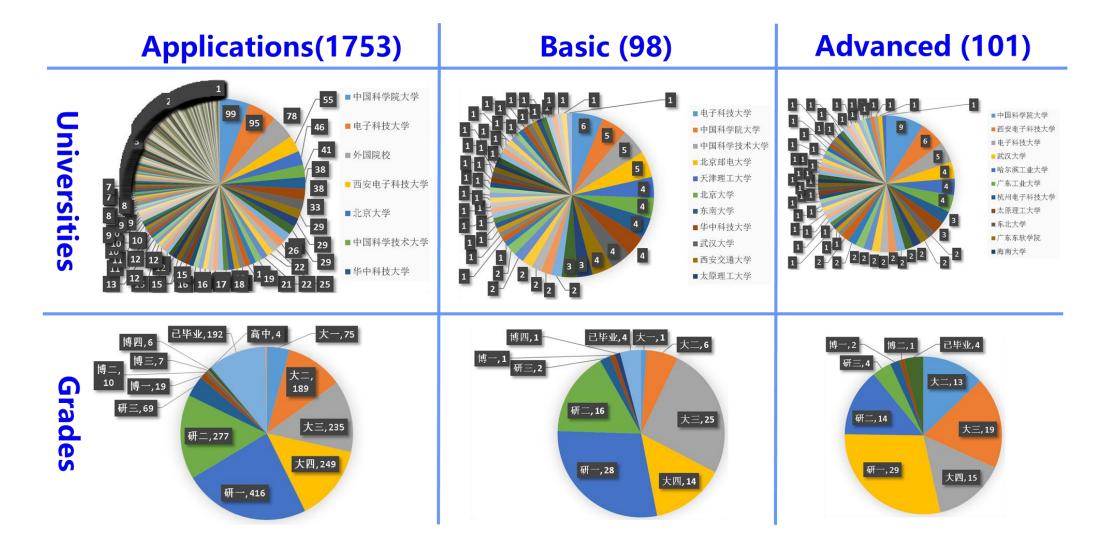

#### > 4000 students participated in the OSOC Initiative

| No.             | Start                    | End of<br>Enrollment | #Enrollment | #School    | #Stu. Learning<br>> 10% | #Stu.<br>Finish |

|-----------------|--------------------------|----------------------|-------------|------------|-------------------------|-----------------|

| 1 <sup>st</sup> | Aug, 2019                | -                    | 5           | 1          | 5                       | 5               |

| 2 <sup>nd</sup> | Aug, 2020                | -                    | 11          | 5          | 11                      | 11              |

| 3 <sup>rd</sup> | Jul, 2021                | Sep, 2021            | 760         | <b>168</b> | 215                     | 51              |

| 4 <sup>th</sup> | Feb, 2022                | Aug, 2022            | 1753        | 328        | 215                     | 16              |

| 5 <sup>th</sup> | Aug, 2022                | In progress          | 1689        | 335        | 148                     | 6               |

| 6 <sup>th</sup> | Will start in July, 2023 |                      |             |            |                         |                 |

Updated: Jun 6<sup>th</sup>, 2023

#### **Track how students are learning**

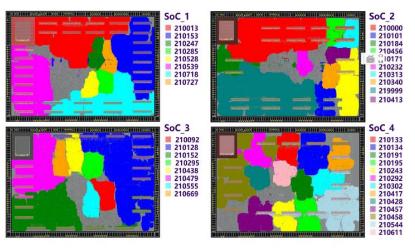

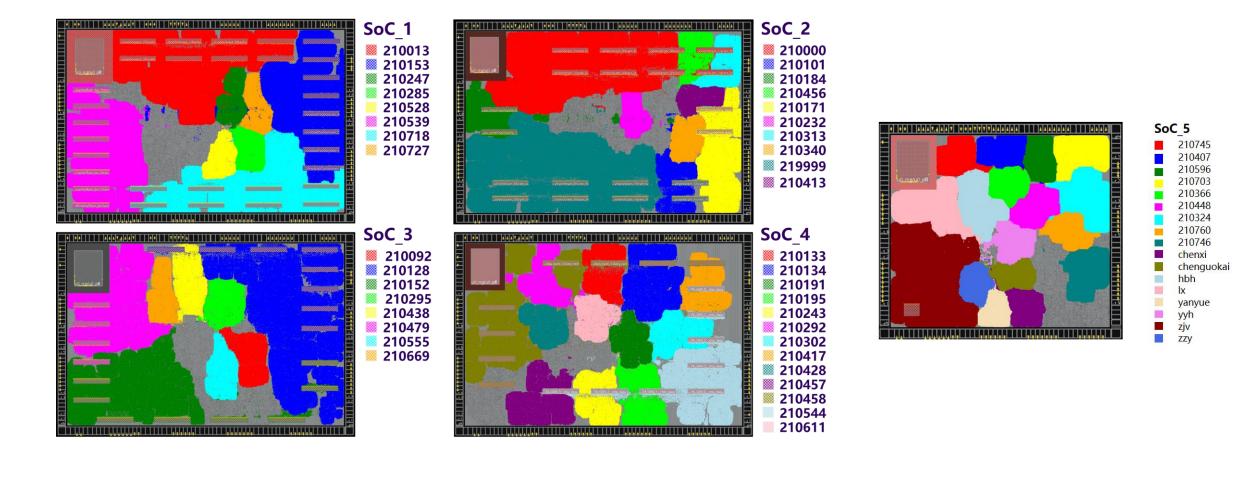

#### **GDSII Layouts of Chips Designed by 50 Students**

#### **Real Chips were Back**

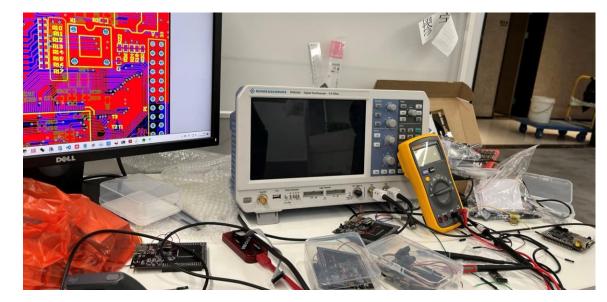

#### **Testing Chips**

## **Contributors to RVI Certification Course**

#### • Translate Courses into Chinese

- RISC-V Overview

- RISC-V Instruction Set Architecture

- Assembly Language for RISC-V

- High Level Languages for RISC-V C Programming

- RISC-V Operating Systems & Tools

Faker Miao

Zhenwei Duan

Frank Liu

Asher Cao

Haifan Yang

Caosy

Rentao Ni

Ren Wei

Lu Chen

Jinlun Su

Jia⁄bîn Wu

| Name         | University                                    |  |  |

|--------------|-----------------------------------------------|--|--|

| Faker Miao   | University of Science and Technology of China |  |  |

| Zhenwei Duan | University of Science and Technology of China |  |  |

| Frank Liu    | Taiyuan University of Technology              |  |  |

| Asher Cao    | University of Science and Technology of China |  |  |

| Haifan Yang  | Zhejiang Gongshang University                 |  |  |

| Caosy        | University of Science and Technology of China |  |  |

| Rentao Ni    | Northeastern University, China                |  |  |

| Ren Wei      | Lanzhou University                            |  |  |

| Jiabin Wu    | ShanghaiTech University                       |  |  |

| Lu Chen      | University of Chinese Academy of Sciences     |  |  |

| Jinlun Su    | Taiyuan University of Technology              |  |  |

#### What's Next?

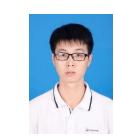

- Have developed an open-source EDA tools (iEDA) and completed three tape-outs

- Will let students use open-source EDA tools to build open-source Chips

#### **Towards Three levels of OSCE**

### **Summary**

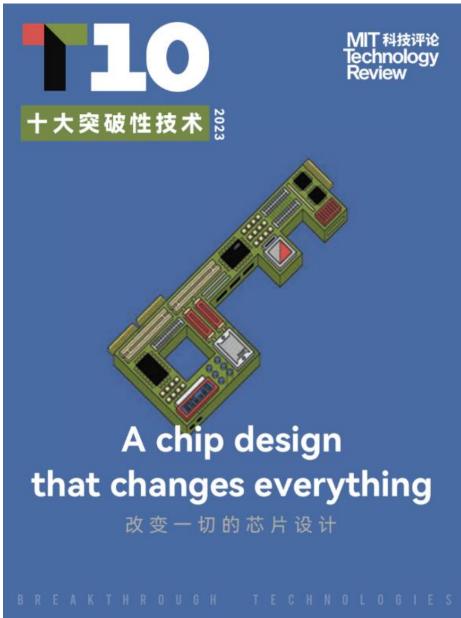

- RISC-V: A chip design that changes everything

- 10 breakthrough of MIT TR 2023

- It is the best time for us to build a globally shared open-source chip ecosystem

- The Chinese community has been contributing and will contribute more to OSCE

#### Welcome to RISC-V Summit China 2023 in Beijing

#### Shangri-La Beijing

#### How to participate in RISC-V Summit China 2023

# **Sponsors**

DDL: 30<sup>th</sup> June email: anxu@bosc.ac.cn

For Non-sponsors DDL: 15<sup>th</sup> July Exhibition display booths

## **Speakers**

DDL: 5<sup>th</sup> July

Call for Speakers:

https://riscv-summit-

china.com/submit-my-talk.html

**Notification to Authors** : 20<sup>th</sup> July **Agenda Published :** 10<sup>th</sup> Aug

### **On-site attendance**

website: <u>https://riscv-</u> <u>summit-china.com</u> Registration will open at the end of June - beginning of July

# Thanks!

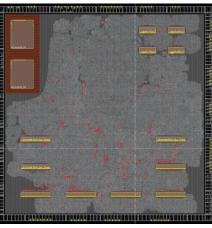

#### **iEDA-Tapeout**

- 1<sup>st</sup> Tapeout

- 2022-02-02, 110nm node, 0.7M gates, Freq: 25MHz, Core Density: 30%

- 2<sup>nd</sup> Tapeout

- 2022-08-12, 110nm node, 1.5M gates, Freq: 25MHz, Core Density: 35%

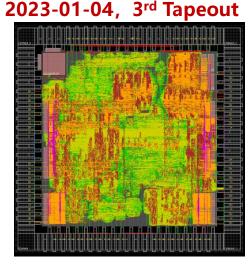

- 3<sup>rd</sup> Tapeout

- 2023-01-04, 28nm node, 1.5M gates, Freq: 200MHz, Core Density: 40%

#### 2022-02-02, 1<sup>st</sup> Tapeout

110nm node, 0.7M gates, 25MHz (5-level pipeline, IP:Chiplink, UART, SPI)

#### 2022-08-12, 2<sup>nd</sup> Tapeout

**110nm node**, **1.5M gates** (11-level pipeline with cache、IP: UART、VGA、PS/2、SPI、SDRAM, Two PLL on SoC, Support Linux)

| 110nm | - > | 28nm |

|-------|-----|------|

|       |     |      |

|       |     |      |

28nm node, 1.5M gates (11-level pipeline with cache、IP: UART、VGA、PS/2、SPI、SDRAM, Two PLL on SoC, Support<sup>4</sup>Pinux)