# Software-driven evolution of a uniquely modular ISA

**Dr. Philipp Tomsich** Chief Technologist & Founder, VRULL GmbH

# Delivering silicon that isn't supported by software is a bug. — Pat Gelsinger, CEO, Intel

# Delivering silicon that fails to optimise for its workloads is a missed opportunity.

### Foster adoption and innovation

Foster a workload-driven evolution of the RISC-V ISA Enable the coexistence with vendor-specific extensions

### Enable differentiation, manage fragmentation

Standardise the basic platforms Enable vendors to gracefully transition from existing non-standard solutions

### Deliver optimised software support

Foster Open-Source Projects, early-adopters, and academia Guide the community towards optimisations for RISC-V

Modularity RISC-V allows implementors to leave off unneeded features from their designs to "scale-to-fit".

> How can we leverage a common software without holding everyone back?

### Extensability RISC-V enables implementors to add their domain-specific "secret sauce" to designs.

How can we innovate and roll out adoption of new features?

| Incre<br>comp |

|---------------|

|               |

| Microarchitectural enhancements | Incre          |

|---------------------------------|----------------|

| Fusion patterns                 | Dimii<br>inter |

nsumes opcode space

reased maintenance burden and nplexity for toolchains

eased complexity for toolchains

ninishing gains due to software roperability requirements

Increased maintenance burden and complexity for toolchains

Ind nd Quan uantita charac tive erisation nethods

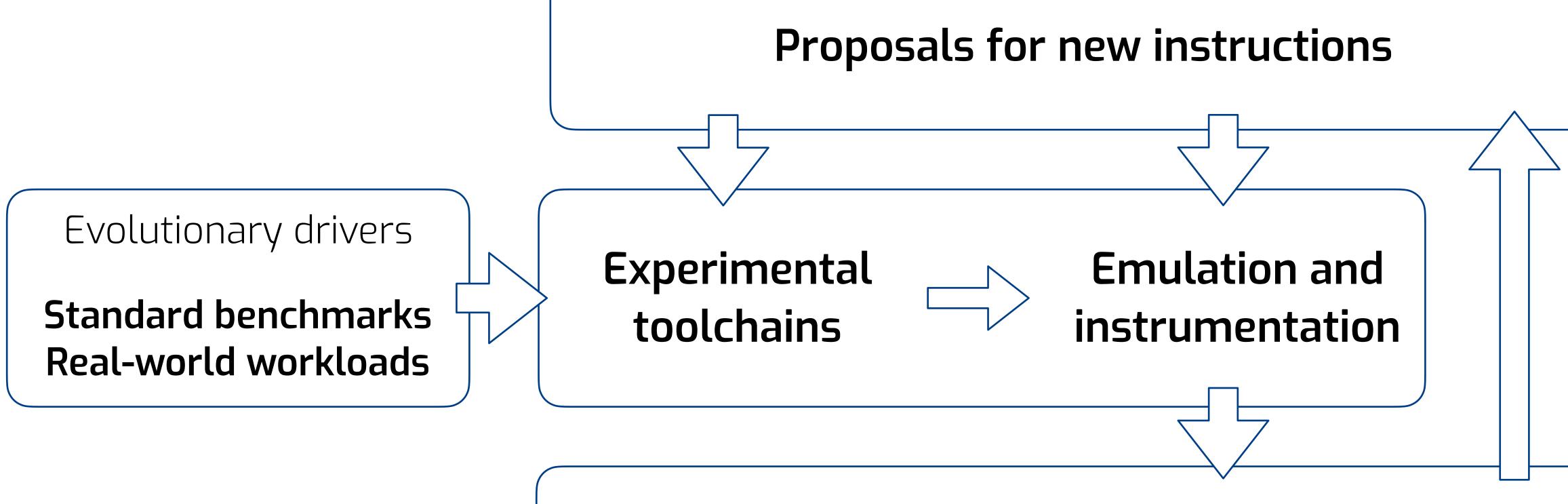

### **Rooting new instructions in fact-based decisions**

### **Performance metrics**

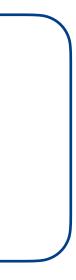

- Derived from quantitative analysis of 'imagick'

- Reduces the dynamic instruction count by 9 to 19% (depending on whether both floor and ceil are calculated before the first branch)

- "Load FP immediate" is based on analysis of SPEC FP

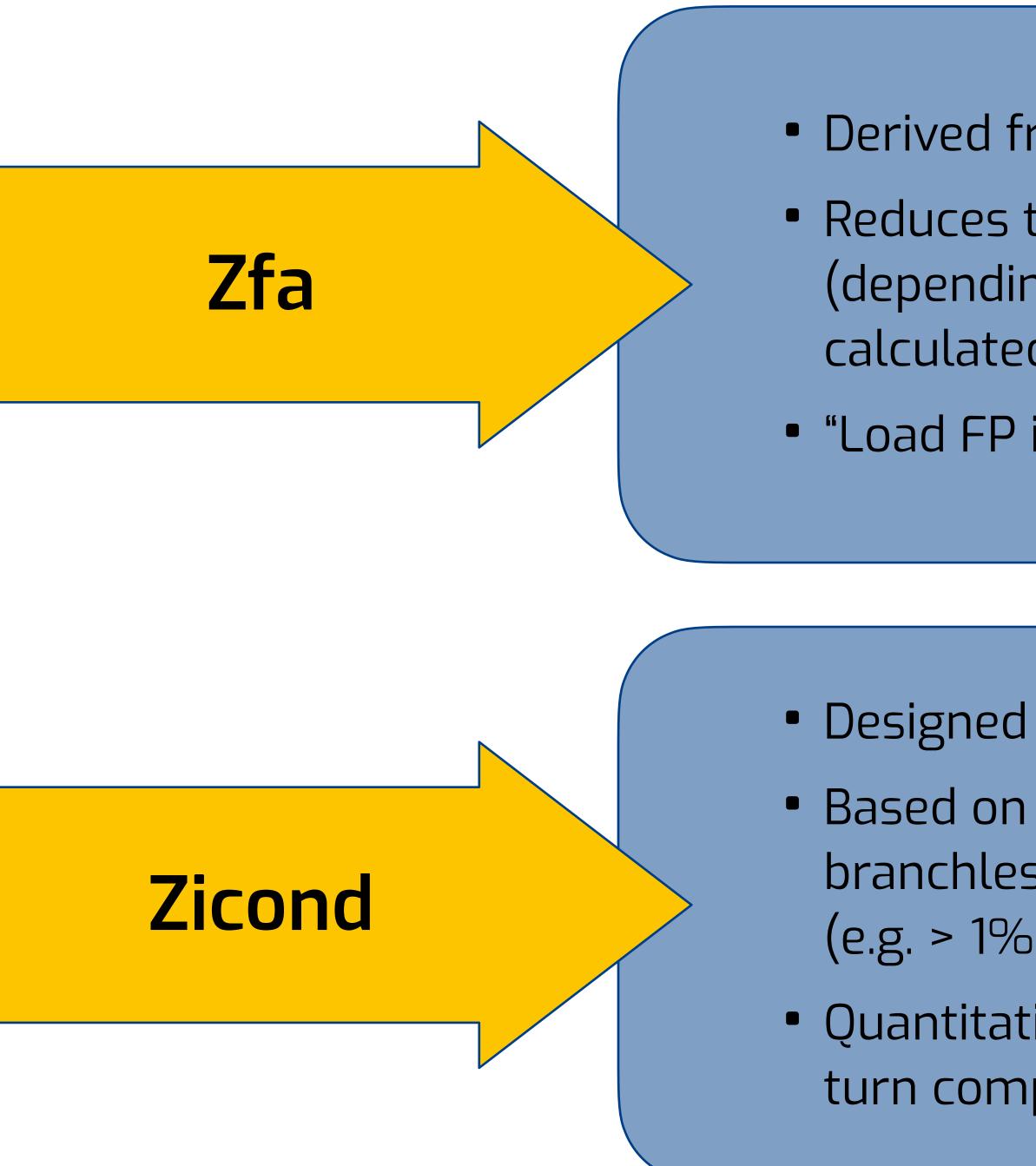

- Designed to follow the RISC-V philosophy

- Based on extensive analysis to confirm that

- branchless sequences also reduce instruction counts (e.g. > 1% on some SPEC benchmarks)

- Quantitative analysis confirms that many branches turn compressible as an add-on benefit

Extensions originating from software applications tend to be small and lightweight.

### Applications & Tools HC

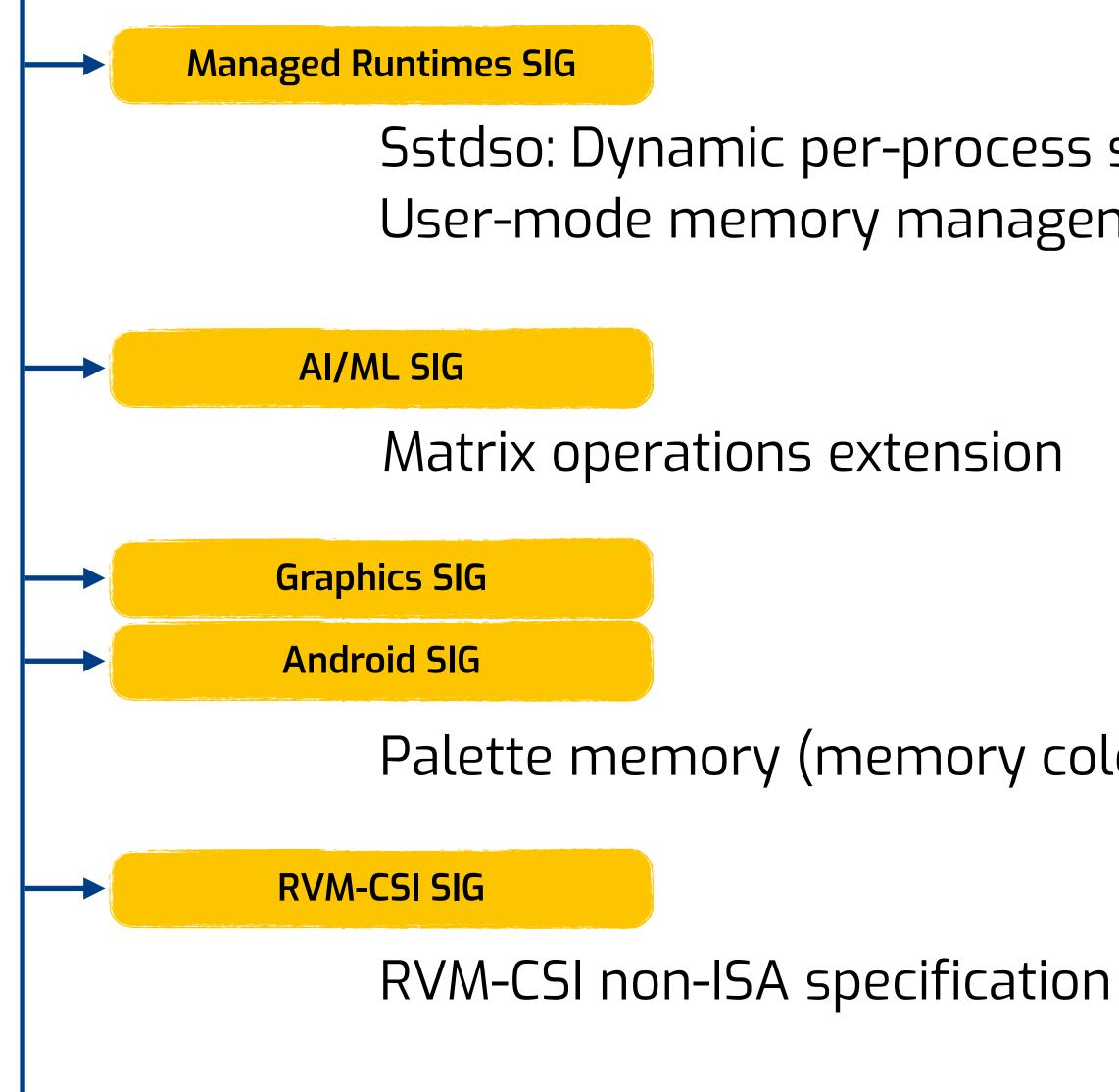

### Sstdso: Dynamic per-process switching of Zits <u>fast-track</u> proposal User-mode memory management <u>fast-track</u> proposal

Palette memory (memory colouring) <u>fast-track</u> proposal

## To successfully evolve the RISC-V we need everyone to drive the discussion based on workload-observations and quantitative data

## Thank you!

www.vrull.eu

philipp.tomsich@vrull.eu