## GreenRio: A Linux-Compatible RISC-V Processor Designed for Open-Source EDA Implementations

Yifei Zhu, Xinze Wang, Guohua Yin, Yihai Zhang, Zhengxuan Luan, Mingzi Wang, Peichen Guo, Xinlai Wan, Shenwei Hu, Dongyu Zhang, Qiaowen Yang and Zhangxi Tan\* **RISC-V International open-source Laboratory**

## Outline

- **Background and Motivation**

- <u>GreenRio Development History</u>

- User Experience of Open Toolchains

- Design Space Exploration in RISC-V Chips and OpenEDA

Over 20 years ago..

Designing a 3GHz, 130nm, Intel ® Pentium® 4 Processor Daniel Deleganes, Jonathan Douglas, Badari Kommandur, Marek Patyra Intel Architecture Group 2501 NW 229th Ave. M/S RA2-401. Hillsboro, OR 97124 USA (503)-613-9278(ph), (503)-712-2776(fax), daniel.j.deleganes@intel.com

- Increasing complexity of IC design leads to high demand on EDA flow

- Traditional fabrication methods Vs Open source toolchains and open PDKs

- Open source projects prevent EDA licenses' limitations

## Motivation

RIOS

GreenRio

ore by the RIOS Lab (r

slab.org) is a 64-bit

GreenRio on Twitter

out-of-order RISC-V processor designed in

- Few designs are developed with open fabrication flow

- Existing open chips are too simple to push the boundary of open EDA toolchains

Current RISC-V cores serving as example designs in the OpenEDA repository:

| Design         | EH1    | IBEX   | Count  | biriscv       | GreenRio1.0     | GreenRio2.0      |

|----------------|--------|--------|--------|---------------|-----------------|------------------|

| Properties     | RV32   | RV32   | RV32   | RV32          | RV64            | RV64             |

| Pipeline stage | 6      | 2 or 3 | 2 or 3 | 6 or 7        | <mark>7</mark>  | 7                |

| Issue Width    | single | single | single | dual          | dual            | dual             |

| Out-of-Order   | ✓      | ×      | ×      | ×             | <mark>√</mark>  | <b>v</b> 2       |

| Gate count (K) | 17     | 10     | 20     | 67            | <mark>60</mark> | 250              |

| nost complay d |        |        |        | la secte at a | <br>← Tweet     | Linux compatible |

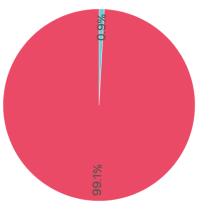

The most complex design among 600+ OpenMPW submissions

**Joodle**

## Motivation

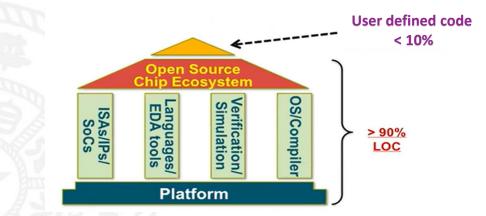

### Optimize the OpenEDA along with the RISC-V CPU together & Put explorations in the flow at various stages

### **GreenRio:**

- 1. Build a RISC-V processor from scratch that is fully compatible with the Open flow

- 2. Drive the growth of both chips and EDA tools through a real and reasonable design

- 3. Conduct researches in Open-Chip field through a meaningful and non-toy-like design instance

- 4. Facilitate chiplets and multi-physics through innovation in both fabrication flow and models

OpenEDA's iteration RISC-V chip's development

Continued Semiconductor Innovation

back

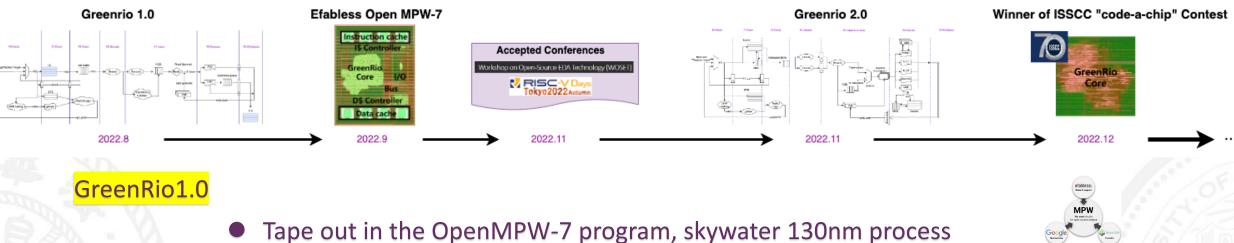

## GreenRio Development History

RIOS

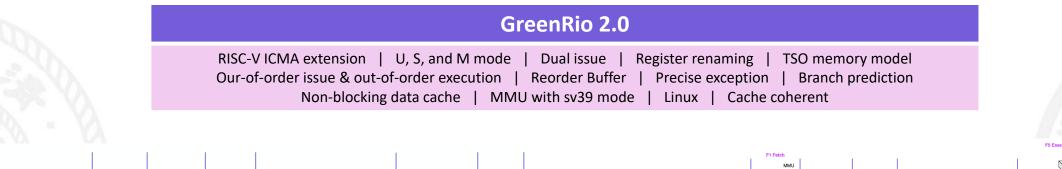

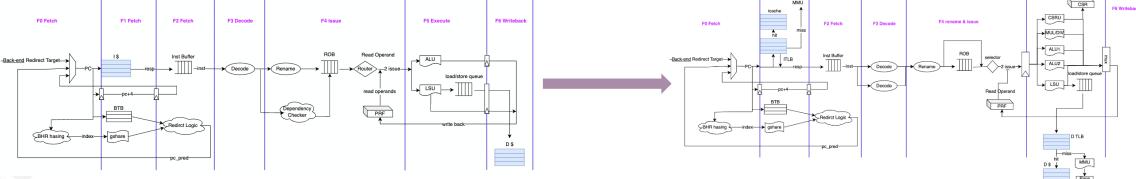

### • With modern processors characteristics

| GreenRio 1.0                                                                                                             |  |

|--------------------------------------------------------------------------------------------------------------------------|--|

| RISC-V I extension   M mode   Dual issue   Register renaming  <br>Reorder Buffer   Precise exception   Branch prediction |  |

## GreenRio Development History

### RIOS

### • Milestone of Greenrio

- Tape out in the OpeniviPW-7 program, skywater 150h

- Related works are accepted by WOSET

- WOSET 2022 Schedule November 3, 2022 Papers 1 Article Author(s) Duration Viierethne I Karunarathne Mitra, Peh Xu. Xiao, Luo Liang 8:40 20 Euphrosine 9:00 20 Zhu Yin Wand e EDA Elo 9:20 Liang, Edwards RSIM: A Switch-Leve ulator and Dynai alvsis Tool

Share the experience in RISC-V Days Tokyo 2022 Autumn

RIOS and Google OpenEDA Team @ Yokohama Japan, 11/2022

7

## GreenRio Development History

### RIOS

### GreenRio2.0

- Benchmark in the OpenEDA domain

- Inspire the RISC-V community and drive growth for opensource semiconductor fabrication

- **GreenRio1:** https://github.com/b224hisl/rioschip **GreenRio2:** https://github.com/0616ygh/GreenRio2

- Future Work:

Enhance the performance and scalability of GreenRio while further optimizing EDA tools

### IEEE SSCS Open-Source Ecosystem "Code-a-Chip" Travel Grant Awards at ISSCC'23

List of Accepted Notebooks:

| Name                   | Affiliation                                                        | Notebook Title                                                                                 |

|------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Yihai Zhang            | Tsinghua-Berkeley Shenzhen<br>Institute, Tsinghua University China | GreenRio 2: A Linux-compatible RISC-V Processor<br>Developed with A Fully Open-Source EDA Flow |

| Anawin<br>Opasatian    | University of Tokyo (Japan)                                        | Bernstein-Yang Modular Inversion with XLS/OpenLane                                             |

| Mauricio<br>Montanares | University of Concepción (Chile)                                   | Sonar On Chip Project                                                                          |

| Nealson Li             | Georgia Institute of Technology<br>(USA)                           | Coordinate Rotation Digital Computer (CORDIC) with OpenLane                                    |

| HyungJoo Park          | Hanyang University (South Korea)                                   | Scan Register layout generation using laygo2                                                   |

| Ali Hammoud            | University of Michigan (USA)                                       | OpenFASoC: Digital LDO Generator                                                               |

| Nimish Shah            | KU Leuven (Belgium)                                                | DPU: DAG Processing Unit for probabilistic ML and sparse matrix algebra                        |

Note: Many thanks everyone for your participation! We recommend to resubmit your Notebooks to the next code-a-chip Notebook competition with revisions. Stay tuned!

The International Solid-State Circuits Conference (ISSCC) 2023 Code-a-Chip Travel Grant Award is created to:

- 1. Promote *reproducible* chip design using *open-source* tools and *notebook-driven* design flows and

- 2. Enable up-and-coming *talents* as well as seasoned *open-source enthusiasts* to travel to the Conference and interact with the leading-edge chip design community.

back

**Focus:** the gap between open and proprietary EDA tools in terms of quality of results (QoR)

### Open-source backend EDA tools

- <u>OpenLane</u>: An automated flow performing full ASIC implementation

- <u>OpenRoad</u>: Enable no-human-in-loop, 24-hour design to remove the barrier to hardware innovation

- Open-source PDK

- Skywater 130nm (Sky130A & Sky130B)

- Open-source external IP

- SRAM blocks compiled by OpenRAM

- Open-source silicon production

- Open Multi Project Wafer (OpenMPW)

- Efabless Chipignite

### RIOS

### What is missing?

### About the open PDK

#### 1. Sky130A techlef lack cut layer

| sky130A techlef lack cut layer               |   |                        |

|----------------------------------------------|---|------------------------|

| LAYER poly<br>TYPE MASTERSLICE ;<br>END poly |   |                        |

| LAYER licon1<br>TYPE CUT ;                   |   |                        |

| WIDTH 0.17 ;                                 | # | Licon 1                |

| SPACING 0.17 ;                               | # | Licon 2                |

| ENCLOSURE BELOW 0 0 ;                        | # | Licon 4                |

| ENCLOSURE ABOVE 0.08 0.08 ;                  | # | Poly / Met1 4 / Met1 5 |

| END licon1                                   |   |                        |

|                                              |   |                        |

#### 2. Open lib is not complete enough

#### lib in 40C has the richest cases:

#### (base) [yzhu@server1 lib]\$ls sky130\_fd\_sc\_hd\_\*\_n40C\*

sky130\_fd\_sc\_hd\_\_ff\_n40C\_1v56.lib

sky130\_fd\_sc\_hd\_\_ff\_n40C\_1v95.lib

sky130\_fd\_sc\_hd\_\_ss\_n40C\_1v44.lib

sky130\_fd\_sc\_hd\_\_ff\_n40C\_1v65.lib

sky130\_fd\_sc\_hd\_\_ss\_n40C\_1v28.lib

sky130\_fd\_sc\_hd\_\_ss\_n40C\_1v60\_ccsnoise.lib

sky130\_fd\_sc\_hd\_ff\_n40C\_1v76.lib

sky130\_fd\_sc\_hd\_\_ss\_n40C\_1v25.lib

sky130\_fd\_sc\_hd\_\_ss\_n40C\_1v26.lib

sky130\_fd\_sc\_hd\_ff\_n40C\_1v76.lib

sky130\_fd\_sc\_hd\_ss\_n40C\_1v35.lib

sky130\_fd\_sc\_hd\_ss\_n40C\_1v60.lib

sky130\_fd\_sc\_hd\_ff\_n40C\_1v95 ccsnoise.lib

sky130\_fd\_sc\_hd\_ss\_n40C\_1v40.lib

sky130\_fd\_sc\_hd\_ss\_n40C\_1v76.lib

#### lib in 25C only has one case

(base) [yzhu@server1 lib]\$ls \*25C\*

sky130\_fd\_sc\_hd\_\_tt\_025C\_1v80.lib

- slow lib set for setup time analysis

- fast lib set for hold time analysis

3. Lack capacitance table and qrctech file

- RC scaling factor

- ICT file for em\_module

Corresponning to Innovus/ICC's MMMC file:

simultaneously analyzes and optimizes the time sequence of all views, and selectively optimizes the area and power consumption

#### 4. Missing 'pg\_pin' on level shifter cells

#### RIOS What is missing? 1. Complete support for System Verilog RTL Design: **Other Files ASIC EDA Flow** Input lib.lef.etc. src/\*sv.v Commercial Tool 2. Logic equivalence check (LEC) & Error checking OpenLane Don't do checking at the last stage **RTL Logic Synthesis** Genus Vetlist and PPA of reference to 'rvj1 caravel soc' in 'top'. (LINK-3) Comparison and Analysis Static Timing Analysis Tempus rror: Width mismatch on port 'meip' of reference to 'core\_empty' in 'top'. (LINK-3) Information: Building the design 'llicache\_32' instantiated from design 'top' with Design for Test Modus DFT \* Smart LEC 3. Engineering Change Order (ECO) Placement and Routing Innvus Adjust the netlist after the RTL is freezing Cross-validation Samrt LEC **RC Extraction** RCX • Only routing stage can use multiple cores Static Timing Analysis Tempus **GDSII** Streaming

Output

Verification

### 5. Optimation algorithms

4. Multi-thread acceleration

About the toolchain itself

Information: Building the design 'core\_empty'. (HDL-193)

the parameters "VIRTUAL\_ADDR\_LEN=32,WB\_DATA\_LEN=32". (HDL-193)

Presto compilation completed successfully. (core\_empty)

Prevent extensive ip usage

Advanced algorithm integration into OpenEDA better timing/area, higher density,...

fined pa pin is not use

### 6. Online user guide

TECHLIB-702(20.15) TECHLIB-702 (error) No pg\_pin with name '%s' has been read in the cell '%s'. The attribute specified for the %s '%s' is being ignored RIPTION message is issued when the pg\_pin specified related\_power\_pin/related\_ground\_pin/related\_bias\_pin does not exist at cell level. These attributes will be ignored. To fix the issue, recharacterize the library with appropriate settings, such that the u

TECHLIB-702(20.15)

11

Comparison and Analysis

GDSII, LEF, Netlist,etc

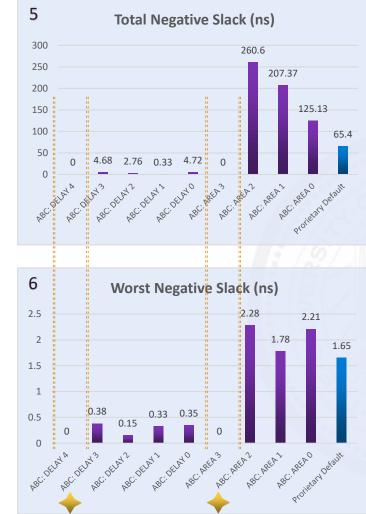

We utilized the proprietary tools and OpenLane/OpenRoad in the sign-off flow of GreenRio

QoR and Runtime

|               | ogic Synt     | hesis            | Compar                                    | ison: Ope      | n vs                                       | Proprietary                                                                                                                                       | ,                                 |                 |                                                             |                    |                                    |

|---------------|---------------|------------------|-------------------------------------------|----------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------|-------------------------------------------------------------|--------------------|------------------------------------|

|               |               |                  | m/YosysHQ/yosys<br>m/berkeley-abc/abc     |                | E OF ENGTAL 5 HERE<br>NUS<br>esis Solution | Green                                                                                                                                             | Rio 1.0:                          | Sram            | ater 130nm, 80MI<br>n Macro: sky130_s<br>nout mult-core acc | sram_1kbyte_1r     | w1r_32x256_8                       |

|               |               |                  |                                           | SYNTH_STRATEGY | 1                                          | Strategies for abc logic synt<br>Possible values are DELAY/A<br>optimization target of the sy<br>the second one is an index.<br>(Default: AREA 0) | REA 0-4/0-3; t<br>nthesis strateg | he first part r | refers to the                                               |                    |                                    |

|               | Tool/Features | Runtime(s)       | Synthesis Strategy                        | Gate Count     | Gap                                        | Cell Area (mm <sup>2</sup> )                                                                                                                      | TNS                               | WNS             | Leakage Power (nW)                                          | Internal Power (W) | Clock Gating Optimization          |

|               |               | 435              | ABC: DELAY 4                              | 50226          | 1.69                                       | 0.57                                                                                                                                              | 0.00                              | 0.00            | 215.00                                                      | 0.04               | 1: 1.27                            |

|               |               | 611              | ABC: DELAY 3                              | 53136          | 1.79                                       | 0.60                                                                                                                                              | -4.68                             | -0.38           | 217.00                                                      | 0.05               |                                    |

|               |               | 529              | ABC: DELAY 2                              | 53982          | 1.82                                       | 0.61                                                                                                                                              | -2.76                             | -0.15           | 219.00                                                      | 0.04               |                                    |

|               |               | 544              | ABC: DELAY 1                              | 54379          | 1.83                                       | 0.61                                                                                                                                              | -0.33                             | -0.33           | 219.00                                                      | 0.04               |                                    |

|               | Open          | 202              | ABC: DELAY 0                              | 52421          | 1.77                                       | 0.60                                                                                                                                              | -4.72                             | -0.35           | 217.00                                                      | 0.04               | Null                               |

|               |               | 219              | ABC: AREA 3                               | 61749          | 2.08                                       | 0.63                                                                                                                                              | 0.00                              | 0.00            | 239.00                                                      | 0.04               |                                    |

|               |               | 910              | ABC: AREA 2                               | 50626          | 1.70                                       | 0.56                                                                                                                                              | -260.60                           | -2.28           | 208.00                                                      | 0.04               |                                    |

|               |               | 685              | ABC: AREA 1                               | 50904          | 1.71                                       | 0.56                                                                                                                                              | -207.37                           | -1.78           | 210.00                                                      | 0.04               |                                    |

| fa <u>ult</u> |               | → <sup>334</sup> | ABC: AREA 0                               | 48496          | 1.64                                       | 0.54                                                                                                                                              | -125.13                           | -2.21           | 208.00                                                      | 0.04               |                                    |

|               | Proprietary   | 543              | SYN_EFF low<br>MAP_EFF low<br>OPT_EFF low | 29657          | 1.00                                       | 0.30                                                                                                                                              | -65.40                            | -1.65           | 130.82                                                      | 0.03               | Yes<br>(sky130_fd_sc_hd_sdlclkp_1) |

### RIOS

### QoR and Runtime

### **Logic Synthesis**

3 Leakage Power (nW) 300 250 200 150 100 50 0 ABC.DEAYO ABC. AREA 3 ABC: DELAY2 ABC.DELAYA ABCAREA2 ABC. DELAVA ABC. DEAN 3 ABCIAREA ABC.AREAO atam Defait

#### open > proprietary

RIOS

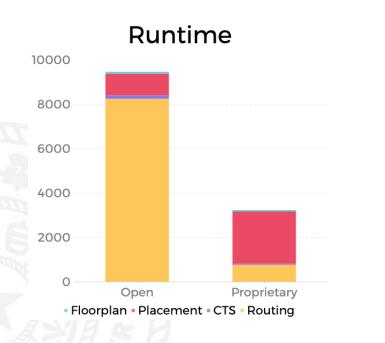

We utilized the proprietary tools and OpenLane/OpenRoad in the sign-off flow of GreenRio

QoR and Runtime

Project/OpenROAD

### Comparison: Open vs Proprietary

GreenRio 1.0: Netlist generated by Yosys

clean gds withou drc/lvs

cādence INNOVUS Technology IMPLEMENTATION SYSTEN (BLOCK) CERTIFIED

• Harden the design with 1 core

|   | Stages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Features         | Open    | Proprietary | [INFO G                         |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------|-------------|---------------------------------|

|   | Nec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Core Utiliation  | 0.35    | 0.35        | [INFO GF<br>ERROR O<br>Given ta |

| 4 | Floorplan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Area (mm2)       | 5.94    | 5.97        | Suggeste<br>Error: g            |

| 9 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Run Time (s)     | 93      | 64          |                                 |

|   | Placement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Density          | 0.6     | 0.6         |                                 |

|   | Flacement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Run Time (s)     | 385     | 2365        |                                 |

| 5 | Clock Tree Synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Run Time (s)     | 149     | 48          |                                 |

| 6 | Routing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Wire Length (um) | 3432810 | 2601926     | Gap: 0.75                       |

| 2 | in the second se | Run time (s)     | 8253    | 763         |                                 |

| > | Total Runtir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ne (h:min:s)     | 2:41:40 | 1:37:07     | - Hig                           |

#### • Route with 8 cores

| ١                | Open        | Proprietary          | K                              |

|------------------|-------------|----------------------|--------------------------------|

| Routing Time (s) | 983 (x0.12) | 127(x0.17)           |                                |

|                  |             | OpenRoad has potenti | al in mult-thread acceleration |

### - Do floorplan with higher utilation → can't fit all the cells

|                                                                                                                    |                                                               | 0                                 |                     |                 |            |  |

|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------|---------------------|-----------------|------------|--|

| [INFO GPL-0020]<br>[INFO GPL-0021]<br>[ERROR GPL-0302]<br>Given target den<br>Suggested target<br>Error: global_pl | MacroInstsArea<br>Use a higher<br>sity: 0.60<br>density: 0.70 | a: 1528626000<br>-density or<br>0 | 000<br>re-floorplan | with a larger o | core area. |  |

|                                                                                                                    |                                                               |                                   |                     |                 |            |  |

| λ                  | Proprietary      |

|--------------------|------------------|

| Core Utiliation    | <mark>0.5</mark> |

| Area (mm²)         | 4.18             |

| Placement Time (s) | 3195             |

| Routing Time (s)   | 1558             |

- Higher density will easily lead to routing congestion

[INFO GRT-0111] Final number of vias: 214085 [INFO GRT-0112] Final usage 3D: 1023424 [ERROR GRT-0118] Routing congestion too high. Error: groute.tcl, 69 GRT-0118

### RIOS

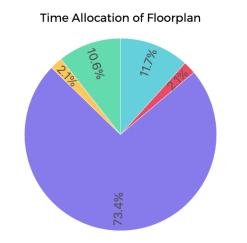

#### From proprietary tools:

A scientific placement may lead to easiler routing convergence

Check Step • IO Planning • Macro Placement • Tap/Well Cells • PDN

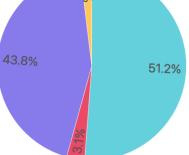

Time Allocation of Routing

Runtime

Global Placement • IO Placement • Resizing & Buffering

Detail Placement

#### For open tools:

- Routing is the most time-consuming task

#### - Spend a lot of time on detail routing (TritonRoute)

| The-OpenROAD-Project / TritonRoute  Code O Issues 11 Pull requests O Act |                                                                                                                          | ⊙ Wate |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------|

|                                                                          |                                                                                                                          |        |

|                                                                          | P master -                                                                                                               |        |

|                                                                          | Commits on Nov 24, 2020 Merge pull request #5 from The-OpenROAD-Project-private/ispd-pipeline                            |        |

|                                                                          | Weige puin request ≪ nonini me-operino/ou-v-loject-private/rspd-pipeline Immi<br>⊗ wbandeira committed on Nov 24, 2020 ✓ |        |

- Determining the location of macro also costs much

## RIOS

### Other Comparisons

- Netlists don't contain module's hierarchical information

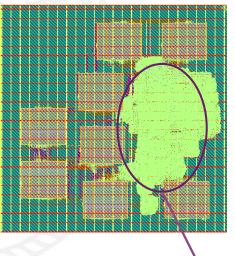

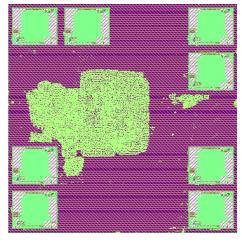

### - Different macro placement

#### GDS generated by Innovus

### GDS generated by OpenRoad

what happens here?

- Design brower use the netlist generated by Compiler

(with hierarchical modules)

Nonblocking cache CPU\_backend CPU\_frontend CSR SOC

back

## Design Space Exploration in RISC-V Chips and OpenEDA

• The design complexity of GreenRio has revealed the **convergence difficulty** in the Open-Chip flow

### For Better area and timing and shorter wirelength

### Integrate Flowtune<sup>[1]</sup> into OpenRoad

8.26.2. Analyzing design hierarchy..

8.27. Printing statistics.

8.28. Executing CHECK pass (checking for obvious problems).

ENTERING FLOWTUNE PROCESS

9. Executing BLIF backend.

10. Executing BLIF frontend.

- 11. Executing OPT pass (performing simple optimizations).

- 11.1. Executing OPT\_EXPR pass (perform const folding).

## Through this process, we also found the ASAP-7nm PDK is not complete enough

abc 01> read /workspace/0penROAD-flow

scripts/flow/results/asap7/gcd/base/output.blif

Line 10: Cannot find gate "DFFHQNx1\_ASAP7\_75t\_R" in

the library. Reading network from file has failed.

### For better user experience, especially for beginners:

Bulid a solution-inspiring error log system

#### - Eg1 : fail in detail placement

[INFO DPL-0035] 399 [ERROR DPL-0035] Detailed placement failed.Maybe increasing the diea area or placement density,or changing placement strategy can solve this problem. Error: detail\_place.tcl, 10 DPL-0036 Command exited with non-zero status 1 Elapsed time: 0:09.70[h:]min:sec. CPU time: user 9.67 sys 0.02 (99%). Peak memory: 101656KB.

#### - Eg2 : fail in global routing

[INFO GRT-0101] Running extra iterations to remove overflow. [INFO GRT-0103] Extra Run for hard benchmark. [INFO GRT-0197] Via related to pin nodes: 1080 [INFO GRT-0198] Via related Steiner nodes: 57 [INFO GRT-0199] Via filling finished. [INFO GRT-0111] Final number of vias: 2425 [INFO GRT-0112] Final usage 30: 13527 [ERROR GRT-0118] Routing congestion too high. Decrease placement density or reduce bus widths maybe work. For more infomation, check the congestion heatmap ;RT-0118

Excellent Efford Award in OpenRoad 7nm Contest

## Design Space Exploration in RISC-V Chips and OpenEDA

• Optimize OpenEDA along with RISC-V Chips together

Complex Design ----> Boundary of tools

More advanced toolchain ----> Designs with more features

- Accelerate the customized chip development

- Leverage the power of open-source community

- Push the frontiers of hardware innovation

## In future...

OpenEDA RISC

- Keep iterating GreenRio; Keep narrowing the gap between open and properitary backend softwares

- AI based ASIC

- advanced algorithms

- open-source data-set for RISC-V VLSI CAD

# Thank you