# Falcon: A Dual-Core Lockstep Microprocessor Based on RISC-V ISA

Jingzhou Li, Huaiyu Chen, Wenbin Zhang and Hu He

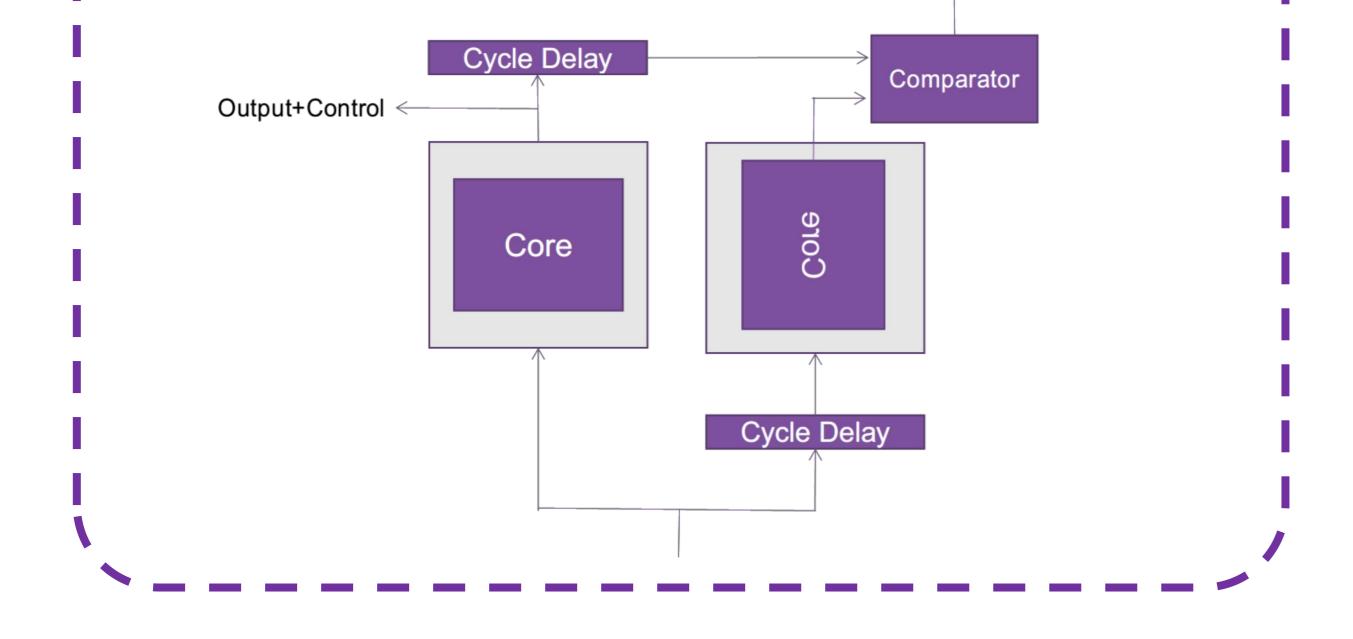

## **Dual-Core Lockstep Basic**

To meet the requirements of high reliability and safety in the automotive industry  $\rightarrow$  Dual-Core Lockstep

Run two identical processor cores in parallel and comparing their outputs

- Reduced software overhead

- Avoided common-mode failures in space and time

• High error coverage

Compare Error

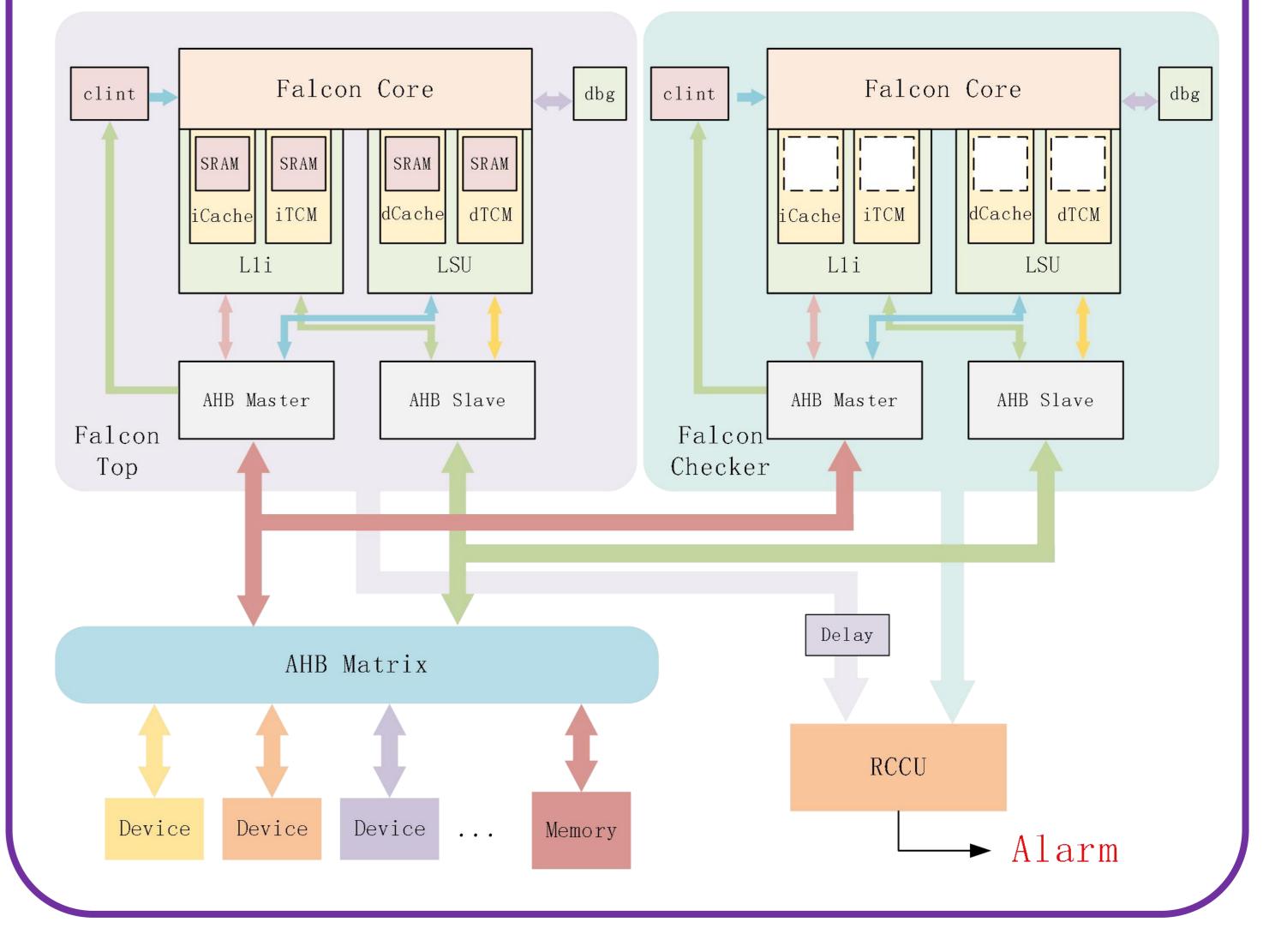

### **Dual-Core Microarchitecture**

- Building on the single-core microarchitecture

- Adds 16KB Instruction TCM(ITCM) and 64KB Data TCM(DTCM)

- Sphere of Replication(SoR) Level : off-core level

- Redundancy Control and Checker Unit (RCCU) for error detection, and if inconsistency occurs, it is reported to the Interrupt Controller and handled through interrupt for error rollback and recovery

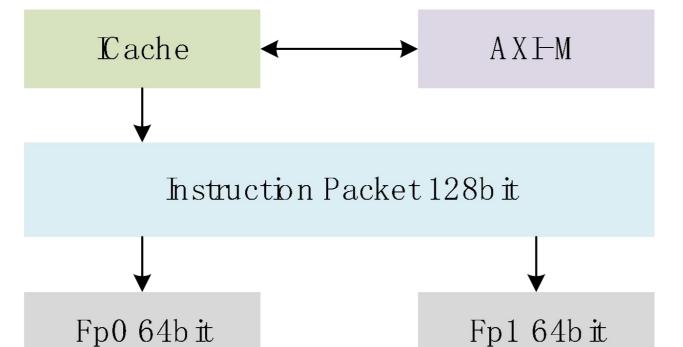

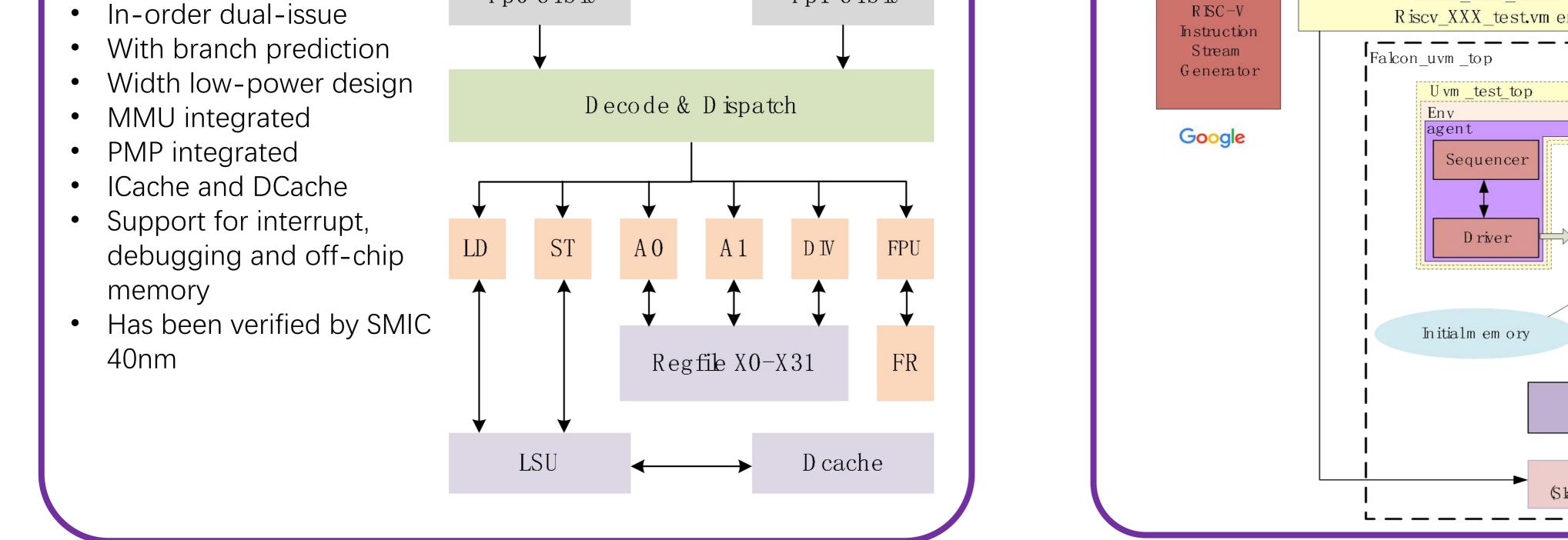

### **Single-Core Microarchitecture**

A 32-bit dual-issue in order RISC-V processor

Support RV32IMAFDC

6-stage pipeline arch

•

#### **RISC-V in Dual-Core Lockstep**

- Open-sourced ISA in Dual-core Lockstep Arch

- Performance equivalent to commercial automotive SoCs

- Software compatible with IAR(an embedded software development tools)

#### **Performance Comparison**

Performance comparison table between Falcon and mainstream lock-step cores such as Power e200z7 and ARM Cortex-R5, which proves that Falcon is comparable to market-leading products in terms of performance.

E200z7

Falcon

#### **Conclusion & Outlook**

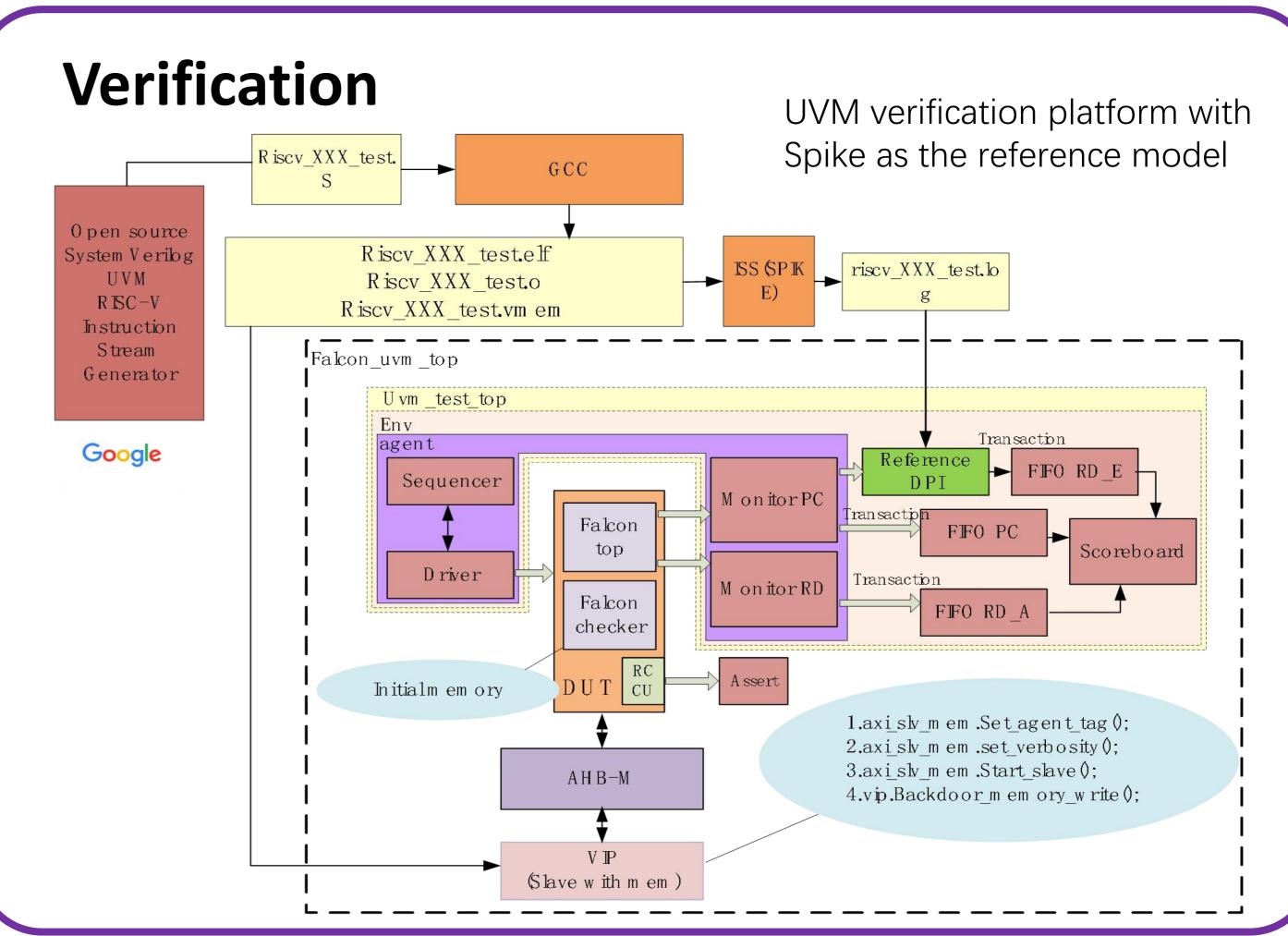

We have implemented Falcon, a RISC-V-based dual-core lockstep MCU, and completed its verification work successfully. Our work demonstrates that RISC-V can fully leverage its opensource advantages in the automotive safety MCU market and open up a market comparable to ARM and PowerPC.

We plan to complete the tape-out work of Falcon in 40nm Process by the end of this year.

| ISA            | RV32GC     | Power ISA  | ARM v7-R,     |

|----------------|------------|------------|---------------|

|                |            | Embedded   | AArch32       |

| Memory         | PMP        | MPU        | MPU           |

| Protection     |            | (optional) | (optional)    |

| FPU Integrated | Integrated | Integrated | Optional      |

|                |            |            |               |

| Issue Width    | 2          | 2          | Selected Dual |

|                |            |            | Issue         |

| Dhrystone      | 1.82       | 2.27       | 1.67          |

| (DMIPS/MHz)    |            |            |               |

| Coremark       | 2.90       | 2.00       | 3.47          |

| (Coremark/MHz) |            |            |               |