# The TETRISC SoC – A Resilient Quad-Core System **Based on PULPissimo**

Junchao Chen, Li Lu, Markus Ulbricht, Milos Krstic IHP, Frankfurt (Oder), Germany

### GOALS

- **Develop an adaptable and resilient** multiprocessor system for reliabilitycritical applications.

- Implement on-demand reconfigurable redundant system allocations under harsh conditions.

- **Develop strategies to balance system** reliability, power consumption, and performance in real-time.

### MOTIVATIONS

- **Growing need for real-time data** processing in aviation and aerospace

- **Overcoming traditional static fault** lacksquaremitigation methods.

- **Requirements for real-time reliability** monitoring network.

- Addresses the dynamic reliability needs of systems that provide optimal operation under normal and severe conditions.

## PLATFORM

- Using the open-source PULP platform and RI5CY core

- **HiRel Framework Controller** (HFC) for dynamic tuning of operating modes with corelevel NMR and clock gating. **ResiliCells enable fast** switching of operating modes.

### OUTLOOK

- Intended to further optimize **ResiliCells to reduce hardware** overhead and improve fault tolerance.

- **Radiation testing and** evaluation of the target chip

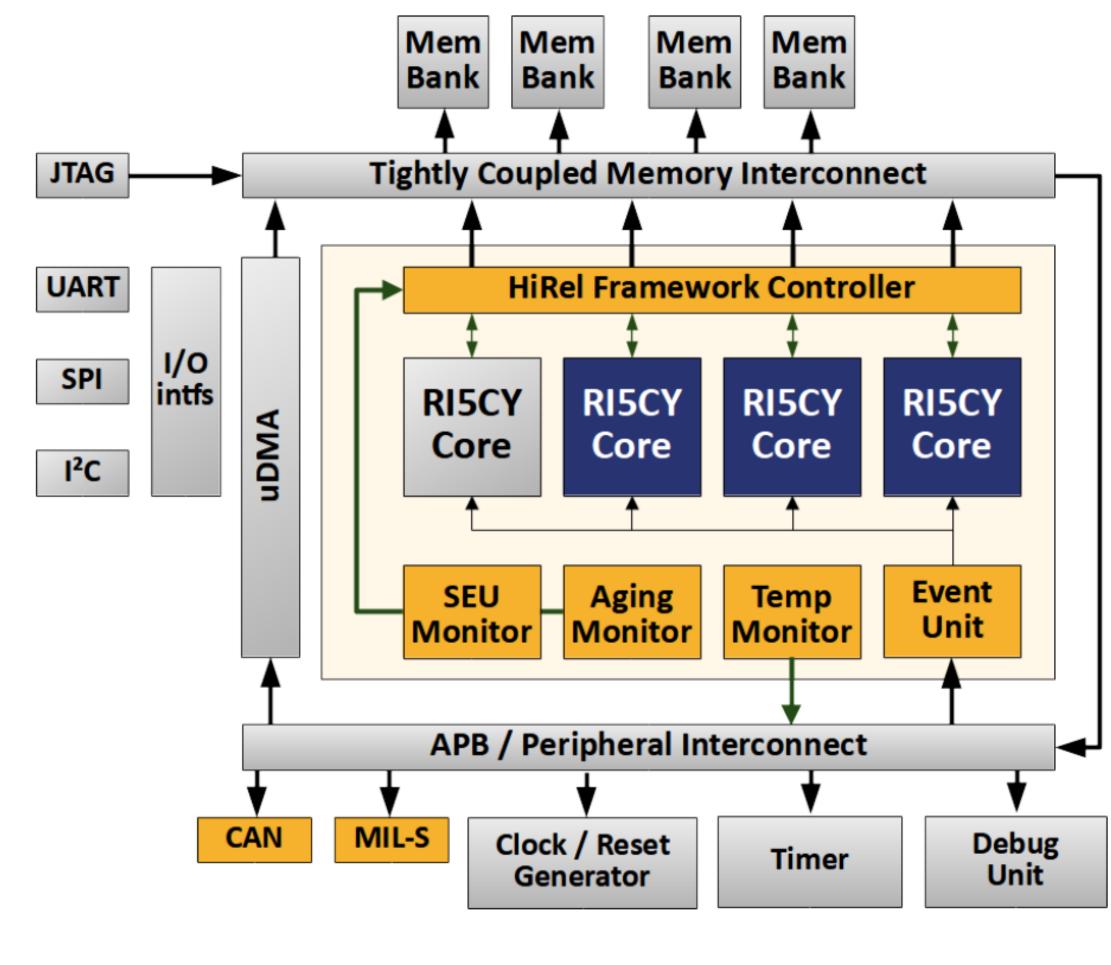

#### **TETRISC SoC Overview**

Fig. 1 The system architecture of the TETRISC SoC.

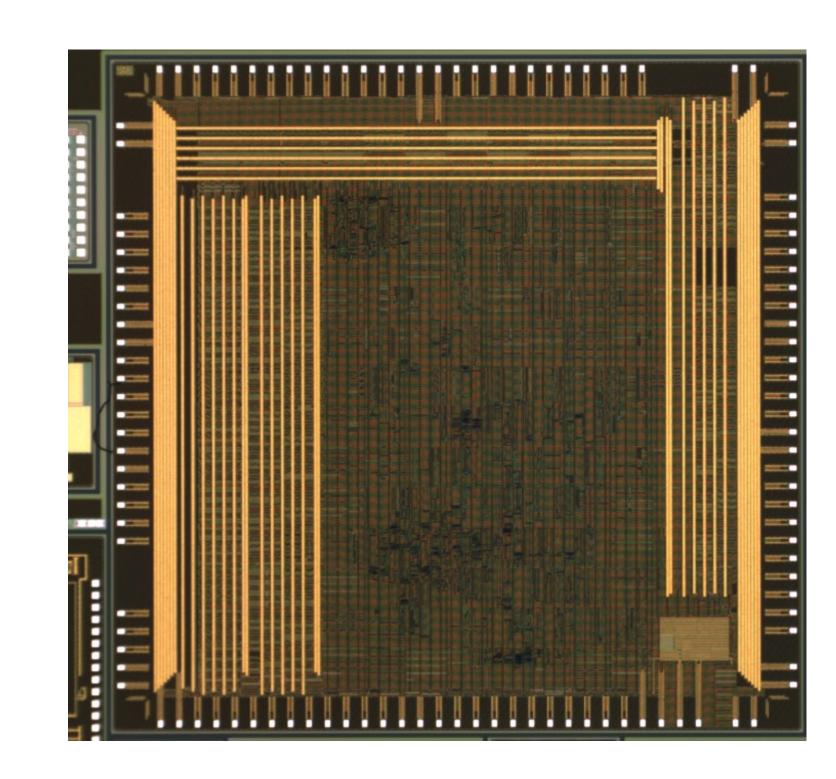

Fig. 2 The die photo of the chip.

- Reconfigurable RISC-V-based quad-core SoC based on the open-source single-core microcontroller architecture PULPissimo.

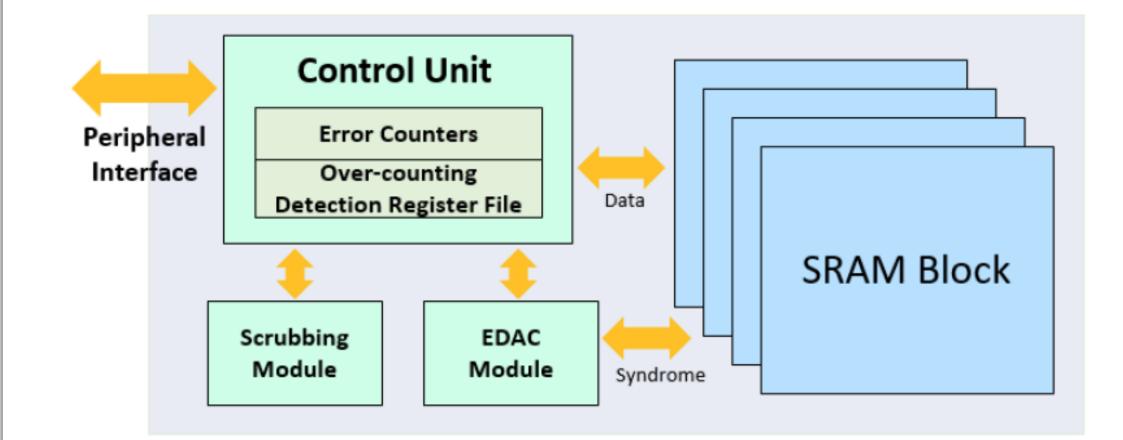

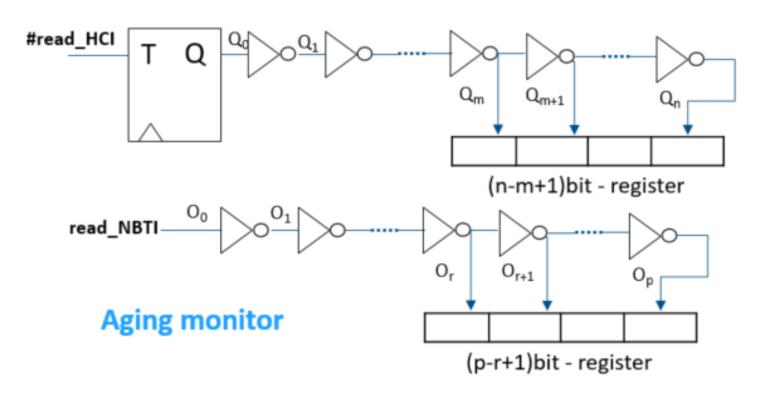

- Multiple on-chip monitors: SEU (radiation), core aging, and temperature monitors.

- Dynamic tradeoffs between reliability, performance and power consumption.

- Intelligent central framework controller for hybrid critical edge computing applications.

- Fabricated with 130nm IHP technology.

- ASIC and FPGA demonstrators.

| Chip area               | 43,56 <i>mm</i> <sup>2</sup> (6.6*6.6mm) |  |  |  |

|-------------------------|------------------------------------------|--|--|--|

| Nominal clock frequency | 30MHz                                    |  |  |  |

| Power consumption       | <1W (estimated)                          |  |  |  |

| Memory                  | 4*8192*40 Bit SRAM                       |  |  |  |

| Pads                    | 81 signal, 35 other                      |  |  |  |

|                         |                                          |  |  |  |

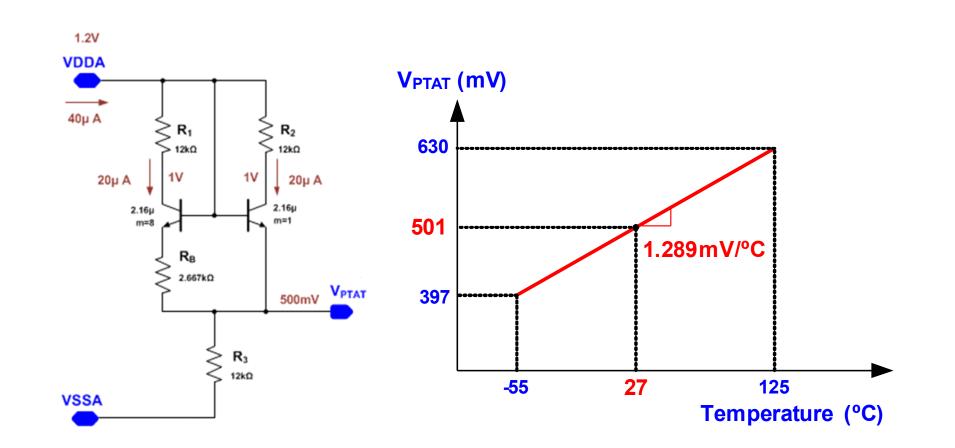

#### **Reliability Monitors**

Fig. 3 General architecture of the Single Event Upset (SEU) radiation monitor.

Fig. 4 Gate-oxide aging monitor consists of HCI and NBTI from IHP.

#### **Adaptiveness and Fault Tolerance**

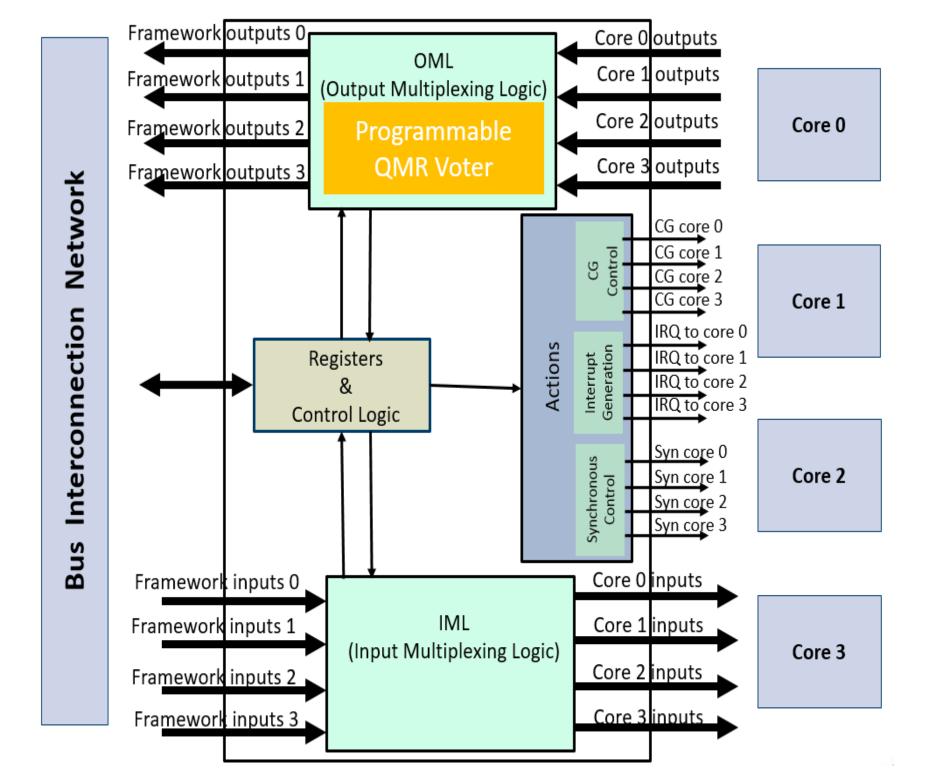

Fig. 6 Block diagram of the HiRel Framework Controller.

- Manages all core inputs and outputs, implementing various operation modes with core-level N-Modular Redundancy (NMR) and clock gating.

- Includes a binary matrix-based programmable NMR majority voter that provides dynamic selection.

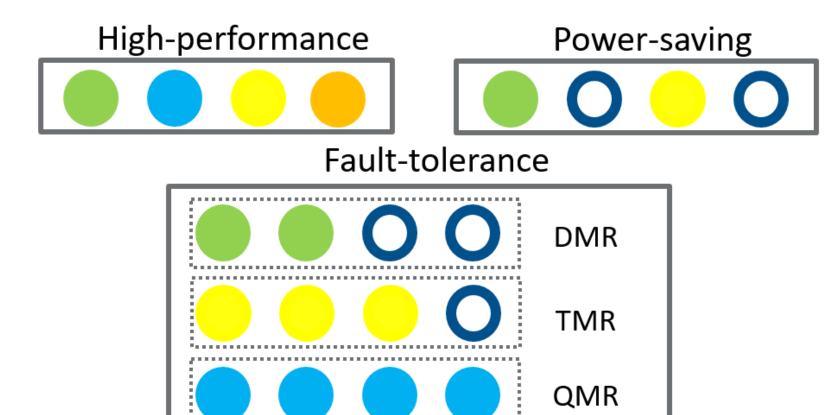

- Three operating mode groups: high performance, power saving, and fault tolerance.

Fig. 7 Example of operating modes in this quad-core multiprocessing system.

| Core 0 Outputs | Core 1 Outputs            | Core 2 Outputs          | Core 3 Outputs | 1 | Core 0 Inputs | Core 1 Inputs | Core 2 Inputs           | Core 3 Inputs |  |

|----------------|---------------------------|-------------------------|----------------|---|---------------|---------------|-------------------------|---------------|--|

|                | Programmable<br>QMR Voter |                         | inactive       |   |               |               |                         | inactive      |  |

|                | rity Output               | Framework<br>Controller |                |   |               |               | Framework<br>Controller |               |  |

| inactive       | Majorit                   | inactive                | inactive       |   | inactive      |               | inactive                | inactive      |  |

|                |                           | (0)                     |                |   | •             |               | <b></b>                 | <b>A</b>      |  |

| FC 0 to BUS    | FC 1 to BUS               | FC 2 to BUS             | FC 3 to BUS    |   | BUS to FC 0   | BUS to FC 1   | BUS to FC 2             | BUS to FC 3   |  |

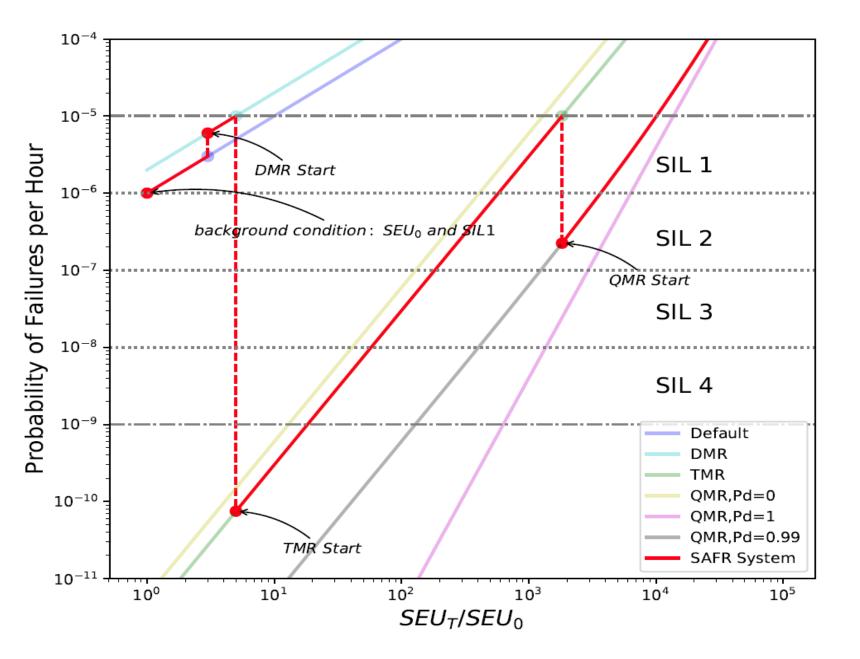

Fig. 8 Example of the HFC configuration. Core 0, 1 and 2 form the core-level TMR, and core 3 is in the clock-gating status.

Fig. 9 Example of the optimal mode selection for this chip.

- Various user-defined and self-triggered fault-tolerant modes with the reliable monitor network.

- Task synchronization between different cores can be achieved in two clock cycles.

- Protection of all components outside the core through the use of TMR flip-flops.

Federal Ministry of Education and Research

innovations for high performance microelectronics Im Technologiepark 25 | 15236 Frankfurt (Oder) | Germany | www.ihp-microelectronics.com