# Enabling Design Space Exploration of RISC-V Accelerator-rich Computing

HELLENIC REPUBLIC National and Kapodistrian University of Athens

Systems on gem5

**Dimitris Gizopoulos**

Odysseas Chatzopoulos

EST. 1837 –

s George Papadimitriou Vasileios Karakostas Computer Architecture Lab, University of Athens, Greece

http://cal.di.uoa.gr

- By doing this we minimize the manual effort required for deploying bare-metal applications and have full bare-metal C library support in the

- Need for tools that enable fast design space exploration and modeling of such designs containing RISC-V cores

- We achieve this goal by porting gem5-SALAM [MICRO'20], a cutting-edge Domain Specific Accelerator (DSA) simulator, to RISC-V

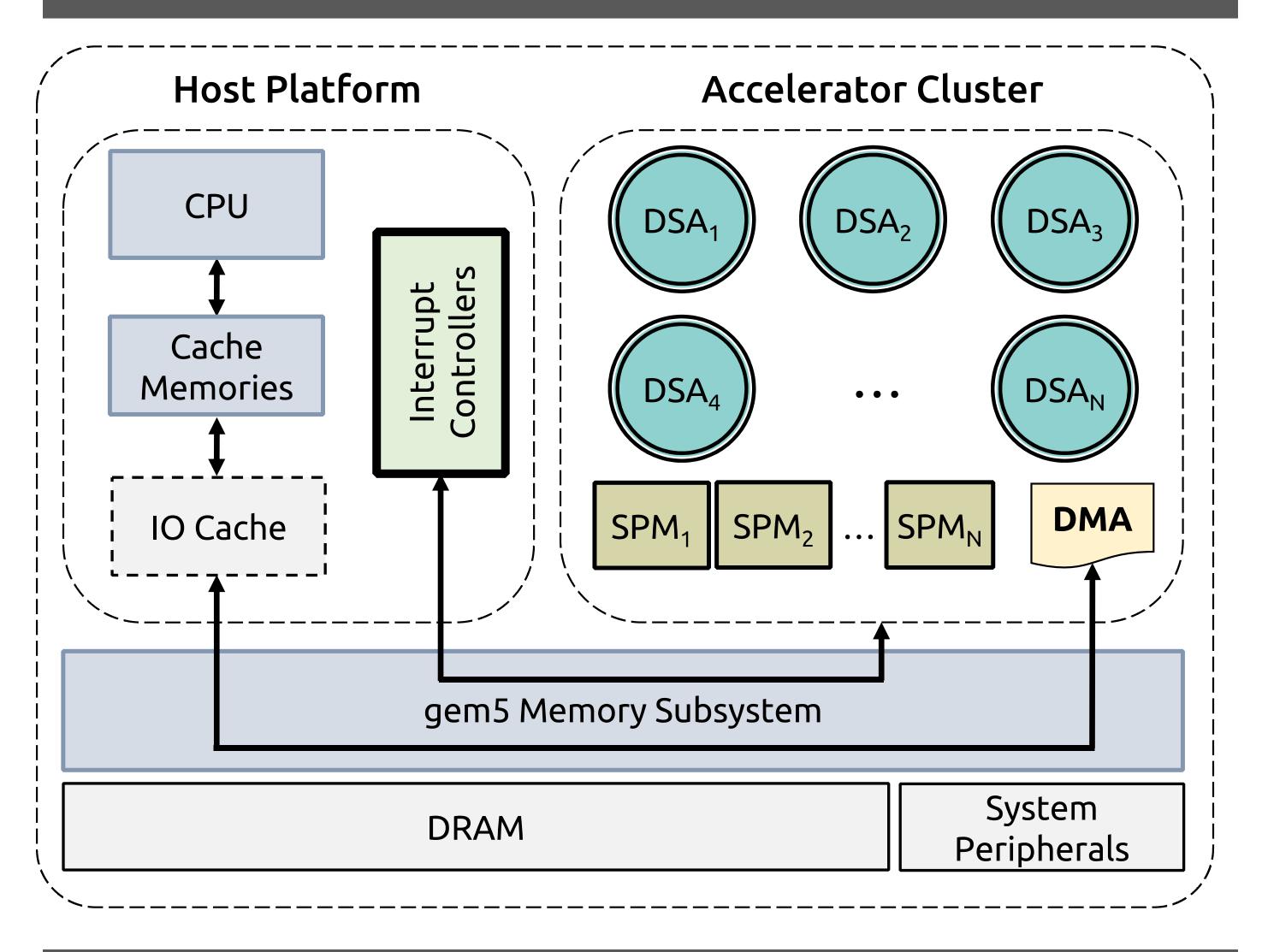

- gem5-SALAM is based on the widely-used gem5 microarchitectural simulator and works by instrumenting the LLVM of C descriptions of DSAs

#### Simulation Framework Architecture

- form of Newlib

- 3. The automatic gem5 configuration script generator used an Arm gem5 configuration script as a template

- To port the generator to RISC-V, we swapped the Arm-specific script template to an already existing RISC-V full-system configuration script

- We also made modifications to initialize the gem5-SALAM components, and added the accelerator memory mapped addresses to the address ranges of the RISC-V platform

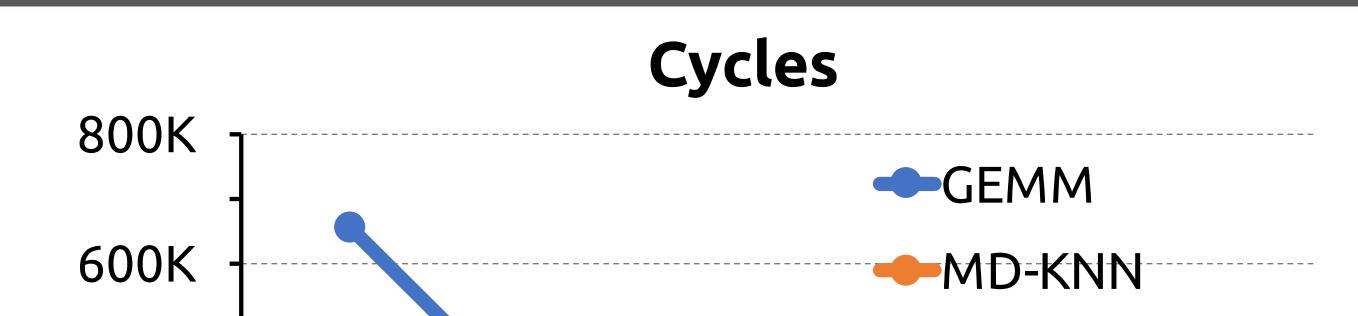

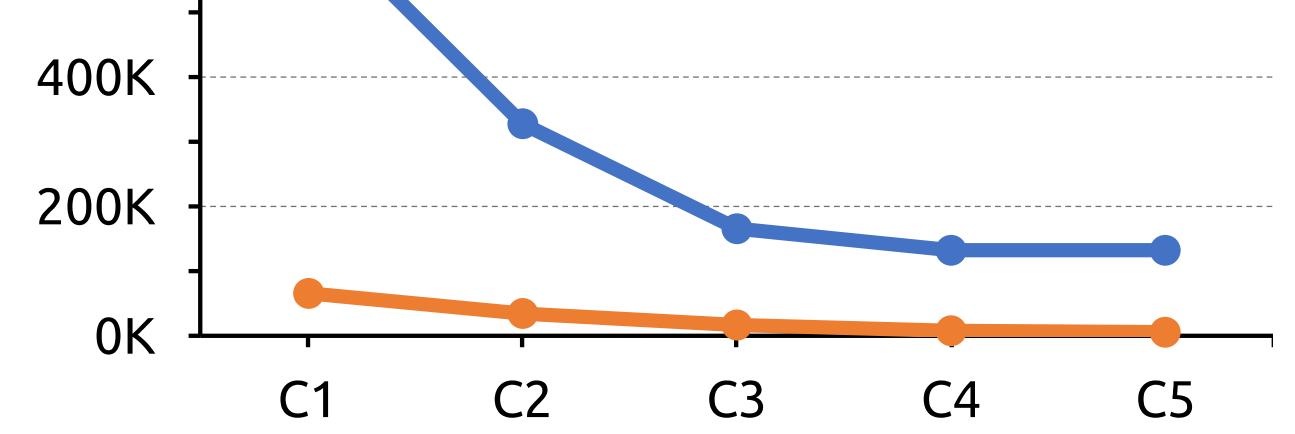

### Execution Time of Different Configurations

### Porting gem5-SALAM to RISC-V

The interrupt system used by gem5-SALAM hardware components employed the Arm General Interrupt Controller (GIC) for posting interrupts to the host CPU

• We translate the GIC functionality to the **RISC-V Platform Level Interrupt Controller (PLIC)**

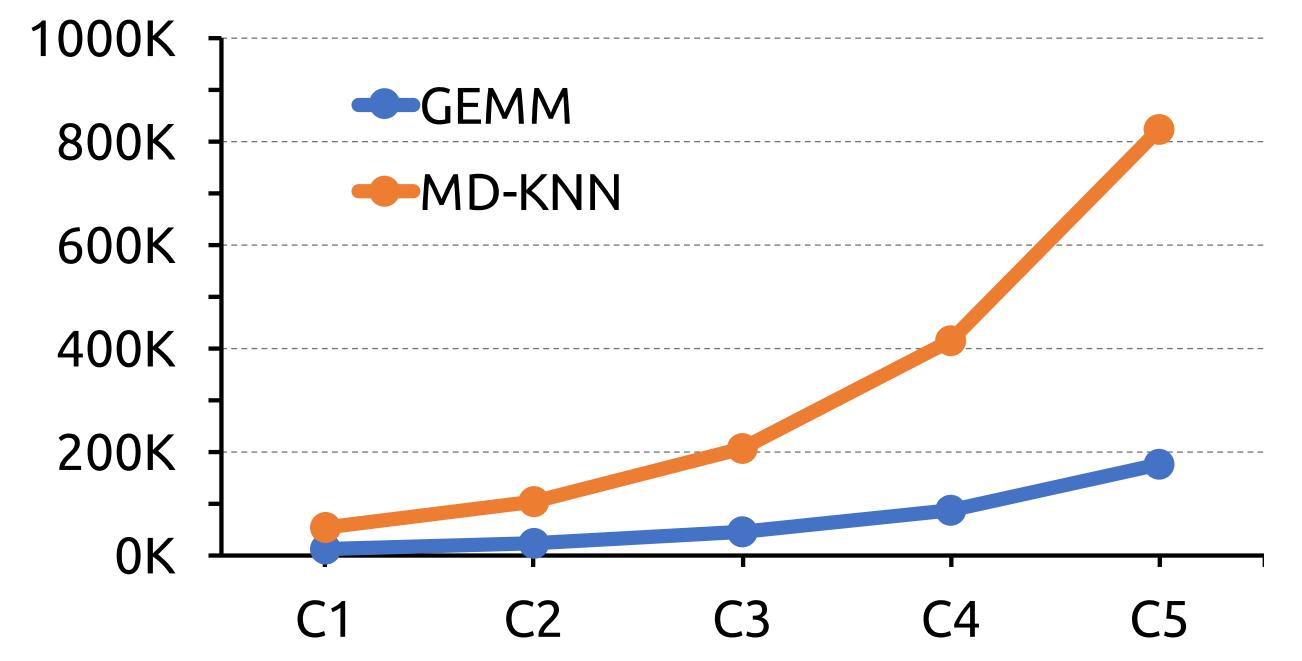

## Area Overhead of Different Configurations

Агеа

implemented in gem5

- The bare-metal software infrastructure included Arm specific boot code and interrupt handler support

- We use SiFive's Freedom-E SDK since the HiFive platform that gem5 supports is based on the SiFive U54 RISC-V SoC. The SDK provides device drivers and system calls that allow for easy configuration of interrupts, UART communication, HW timers

- In the two graphs above we can observe the inverse relationship between performance and area of two different accelerator designs. Configurations C1 - C5 contain an increasing amount of functional units

- This enhanced version of gem5-SALAM can be used to find the ideal trade-off between these metrics

This project has received funding from the European Union's Horizon Europe research and innovation programme under grant agreement No. 101070238 (NEUROPULS) and No. 101097224 (REBECCA). Views and opinions expressed are however those of the authors only and do not necessarily reflect those of the European Union. Neither the European Union nor the granting authority can be held responsible for them.