# Open Virtual Platforms (OVP) APIs Enable High Quality RISC-V Models

- Use cases and requirements for RISC-V processor models

- ImperasFPM fast processor model architecture

- OVP APIs

- Case studies

- Summary

- Use cases and requirements for RISC-V processor models

- ImperasFPM fast processor model architecture

- OVP APIs

- Case studies

- Summary

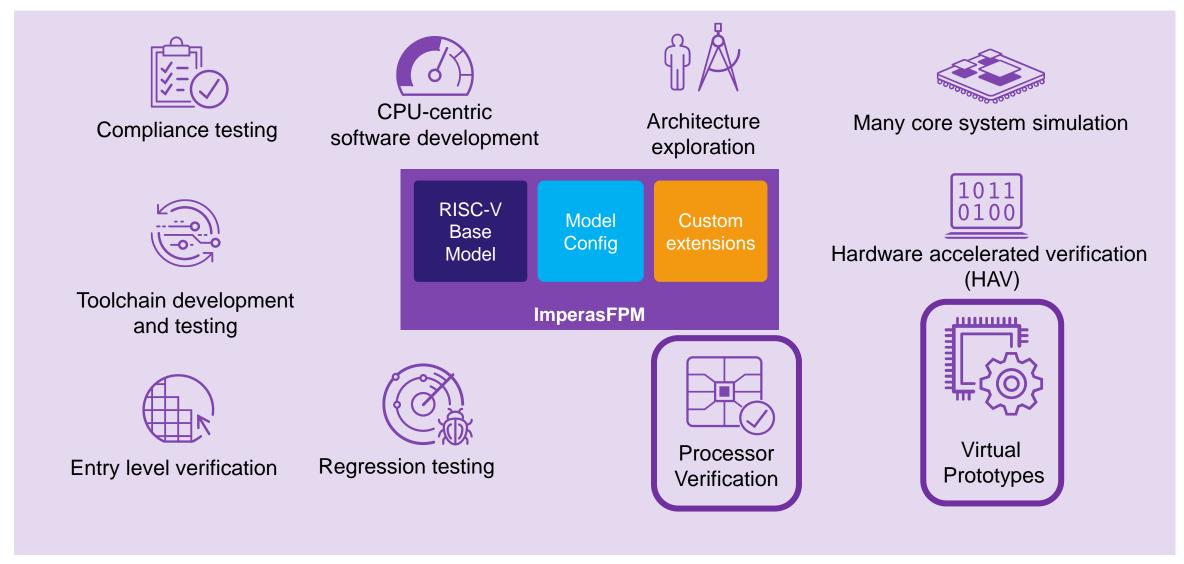

#### RISC-V Processor Model Use Cases

Architecture exploration

Many core system simulation

Toolchain development and testing

**RISC-V Processor Model**

Hardware accelerated verification (HAV)

Virtual Prototypes

Entry level verification

Regression testing

Processor Verification

### RISC-V Processor Model Requirements are Driven by the Use Cases

This is a lot more than just an Instruction Set Simulator (ISS)

- Model the ISA, including all versions of the ratified spec, and stable unratified extensions

- Easily update and configure the model for the next project model cannot be "one-off"

- User-extendable for custom instructions, registers, ...

- Model actual processor IP, e.g. Andes, SiFive, OpenHW CORE-V, MIPS, ARC-V, ...

- Well-defined test process including coverage metrics

- Interface to other simulators, e.g. SystemVerilog, SystemC, ...

- Interface to software debug tools, e.g. GDB/Eclipse, Lauterbach, GHS, ...

- Interface to software analysis tools including access to processor internal state, etc.

- Interface to architecture exploration tools including extensibility to timing estimation

- Use cases and requirements for RISC-V processor models

- ImperasFPM fast processor model architecture

- OVP APIs

- Case studies

- Summary

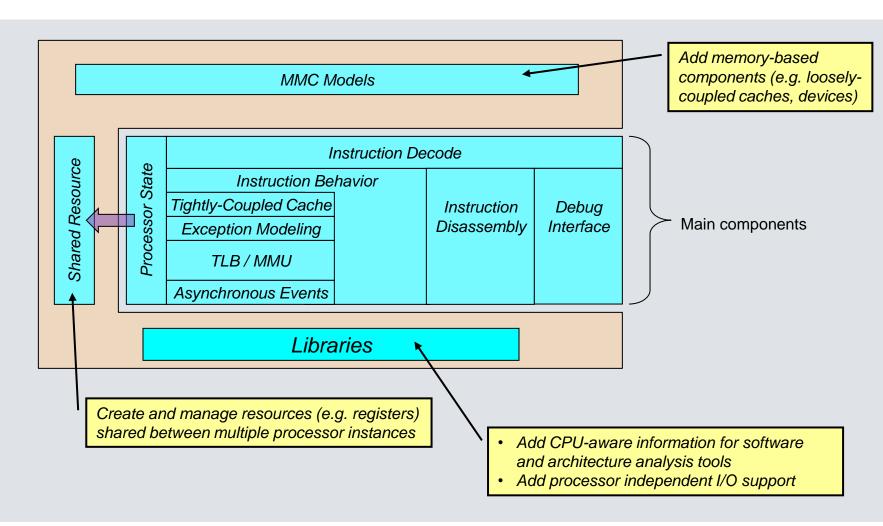

### Components of ImperasFPM RISC-V Processor Models

- Models are built in C using OVP APIs

- APIs are supported by a simulator engine

- All models have both C and SystemC/TLM2 native interfaces

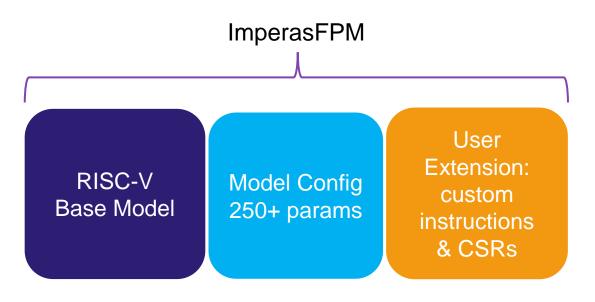

### ImperasFPMs (Fast Processor Models) for RISC-V

- Base Model implements RISC-V specification in full

- Fully user configurable to select ISA extensions and versions

- Pre-defined configurations and custom instructions for processor IP vendors

- User extensions built in a separate library do not perturb the verified Base Model, help reduce maintenance

- Because every ImperasFPM uses the RISC-V Base Model, and including users of both commercial and free tools, over 150 companies, organizations and universities have used the ImperasFPM

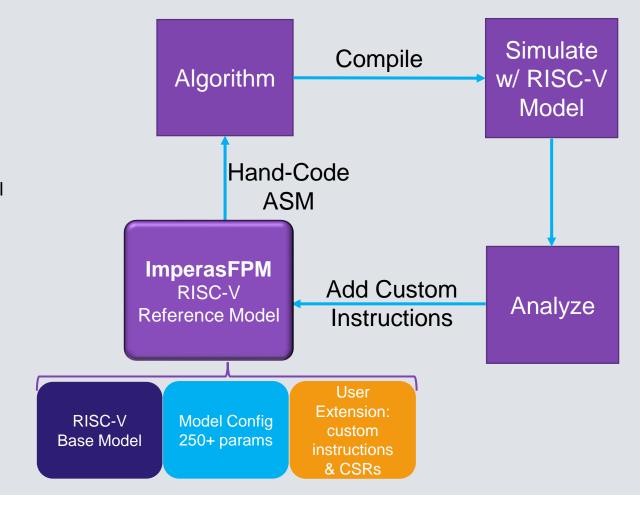

#### Models Drive Customization

- In the RISC-V world, custom instructions are added to optimize a specific application or set of applications within a domain

- "Domain-Specific Processors"

- Models let you explore custom instructions quickly

- Much faster to develop/analyze custom instructions in the model than by writing RTL

- Better profiling data and other analytical tools

- Better software debug capabilities

- Methodology

- Start by characterizing the application to be optimized

- Then add custom instructions, evaluate and iterate

- Use cases and requirements for RISC-V processor models

- ImperasFPM fast processor model architecture

- OVP APIs

- Case studies

- Summary

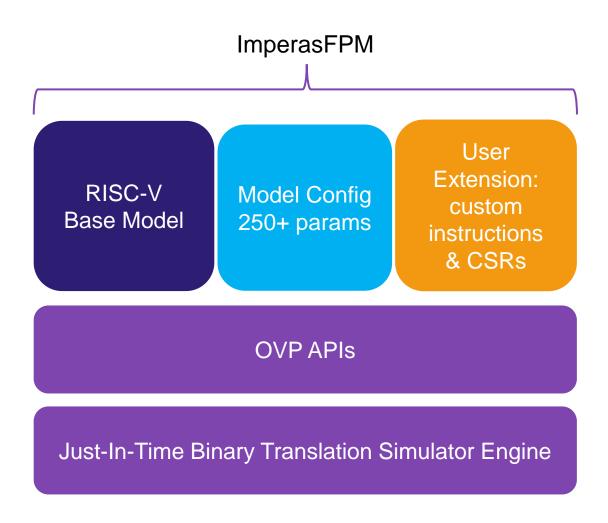

#### ImperasFPM Architecture

- OVP APIs support ...

- Model functionality

- Processor analysis tools

- APIs are supported by a Just-In-Time (JIT) binary translation simulator engine

- Translates RISC-V instructions to x86 on host PC

- Adds in analysis "instrumentation" to the simulator, so analysis is non-intrusive

- APIs are publicly available: https://github.com/OVPworld/information

- The OVP APIs have been used to develop models of 18 different instruction set architectures (ISAs), including 3 proprietary ISAs

- Matured by supporting ISAs such as Arm and MIPS before being used for RISC-V

### Why the ImperasFPM Architecture Works Well

- Performance optimization: When a specific API's performance is improved, it impacts all the models using that API

- Maintenance: When the functionality of a specific API is fixed, it flows to all the models using that API

- Documentation: Having APIs leveraged over a range of models enables better documentation of the APIs (and of the models)

- Tool interfaces: When a new model is built, existing tools automatically work with the new model

- As a result, many fewer engineers are needed to develop and maintain the ImperasFPM models

- As a result, ImperasFPM users can easily add custom features to their models

- Use cases and requirements for RISC-V processor models

- ImperasFPM fast processor model architecture

- OVP APIs

- Case studies

- Summary

### ImperasFPM Use Cases

Architecture exploration

Many core system simulation

Toolchain development and testing

Hardware accelerated verification (HAV)

Virtual Prototypes

Entry level verification

Regression testing

Processor Verification

## Using the same model for both hardware and software verification enables significant reduction in SoC bring up time

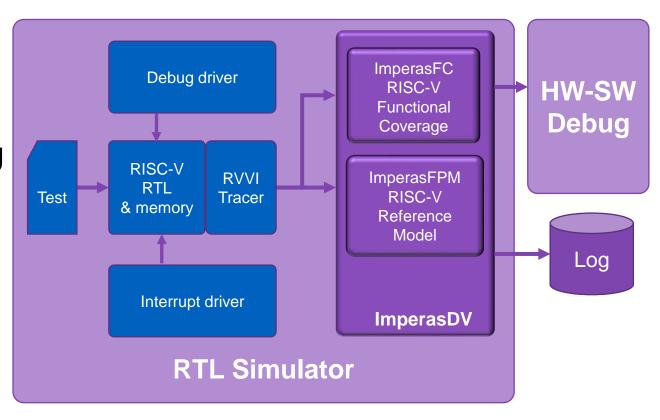

### RISC-V Processor Verification Environment Enabled by RISC-V Reference Model

- ImperasFPM is the configurable, extendable RISC-V reference model

- Continuous comparison and checking of architectural state

- Detects synchronous and asynchronous bugs

- Complete RISC-V architectural Functional Coverage model

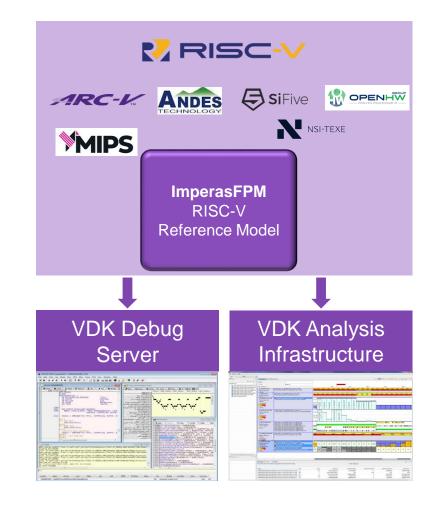

## Virtual Prototyping for Early Software Development Enabled by RISC-V Reference Model

Virtual prototypes now a mainstream technology for embedded software development/test

- Shift left software development

- Comprehensive software development environment key for AI, automotive, other industries where software optimization and certification are required

- Support for ...

- all major RISC-V processor IP vendors

- customers building their own RISC-V processor

- Enables Continuous Integration / Continuous Deployment (CI/CD) methodology

Virtual prototypes with ImperasFPM RISC-V models typically achieve 500-1,000 million instructions per second performance (e.g. boot Linux in ~6 sec on host PC)

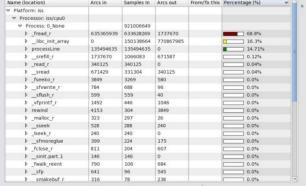

## Case Study: Adding CHACHA20 Encryption Instructions to Improve Performance of Character Stream Encoder

- Before adding custom instructions, character stream encoder software took ~1.3 billion instructions to execute

- Profiling showed "processLine" function took 21% of execution time

- Now add custom instructions to improve performance

- This instruction extension library will be used to develop four custom instructions

- Each uses the same base behavior

- Different rotation value

- When implementing new instructions, start with the decode table, including

- The fixed fields defining the instruction class

- The fields defining the source and result registers to be used

- In the RISC-V ISA these will be R-Type instructions in custom-1 decode space

|   | Bits    | Bit Value                       | Description                           |

|---|---------|---------------------------------|---------------------------------------|

|   | 6 – 0   | 00 010 00                       | Custom-1 instruction class decode     |

|   | 11 – 7  | XXXXX                           | Identify the result register          |

|   | 14 – 12 | 000<br>001<br>010<br>011<br>1xx | QR1<br>QR2<br>QR3<br>QR4<br>Undefined |

| 1 | 19 – 15 | XXXXX                           | Identify source register 1            |

|   | 24 – 20 | XXXXX                           | Identify source register 2            |

|   | 31 – 25 | 0000000                         | Instruction decode                    |

#### Instruction Decode Table

```

//

// Create the RISCV decode table

//

static vmidDecodeTableP createDecodeTable(void) {

vmidDecodeTableP table = vmidNewDecodeTable(RISCV_INSTR_BITS, RISCV_EIT_LAST);

// handle custom instruction

DECODE_ENTRY(0, CHACHA20QR1, "|0000000......000....0001011|");

DECODE_ENTRY(0, CHACHA20QR2, "|0000000......001.....0001011|");

DECODE_ENTRY(0, CHACHA20QR3, "|0000000.......010.....0001011|");

DECODE_ENTRY(0, CHACHA20QR4, "|0000000..........011.....0001011|");

return table;

```

- This decode table is then constructed in the extension library constructor

- Stored in the vmiosObject structure

### Instruction Behavior is Defined Using VMI Morph Time Functions

```

//

// Emit core implementing exchange instruction

Static void emitChaCha20(

vmiProcessorP

processor,

vmiosObjectP

object,

Uns32

instruction,

Uns32

rot1

// extract instruction fields

RD(instruction);

Uns32 rd =

Uns32 rs1 =

RS1(instruction);

Uns32 rs2 =

RS2 (instruction);

vmiReg reg rs1 = vmimtGetExtReg(processor, &object->rs1);

vmiReq req rs2 = vmimtGetExtReq(processor, &object->rs2);

vmiReg reg tmp = vmimtGetExtTemp(processor, &object->tmp);

vmimtGetR(processor, RISCV REG BITS, reg rs1, object->riscvRegs[rs1]);

vmimtGetR(processor, RISCV REG BITS, reg rs2, object->riscvRegs[rs12]);

vmimtBinopRRR(32, vmi XDR, reg tmp, reg rs1, reg rs2, 0);

vmimtBinopRC(32, vmi ROL, reg tmp, rot1, 0);

vmimtSetR(processor, RISCV REG BITS, object->riscvRegs[rd], reg tmp);

```

## Adding Custom Instructions Reduces Number of Instructions Executed, Reduces Execution Bottleneck

Model -> API -> Simulator architecture allows tools to just work automatically

Simulation performance increase from 1.1 to 1.3 billion instructions per second

CHACHA20 instructions in instruction trace

Key "processLine" function now takes <15% of execution time

CHACHA20 instructions in debugger disassembly view

- Use cases and requirements for RISC-V processor models

- ImperasFPM fast processor model architecture

- OVP APIs

- Case studies

- Summary

### OVP APIs Enable High Quality RISC-V Processor Models

- RISC-V processor models are at the heart of RISC-V processor development

- An API-based processor model architecture can more easily meets all the use case requirements

- An API-based processor model architecture can provide multiple benefits including quality, flexibility, extensibility, high performance, ease of documentation

- The OVP APIs used in the ImperasFPM RISC-V processor models provide all these benefits, while reducing the resources required for processor development and maintenance

- These benefits have been proven with results from hundreds of projects, including ~30 tape outs enabled by processor verification using ImperasFPM golden reference models

### THANK YOU

# Our Technology Your Innovation<sup>TM</sup>

Larry Lapides @synopsys.com