# Solving the RISC-V puzzle

Optimal performance with zero risk

Ron Black

RISC-V Summit Europe 2024 keynote

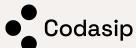

#### → This is Codasip

- Founded in 2014

- HQ in Munich

- ~250 employees

- All design teams in Europe

- **₹** RISC-Younding member

- Enabling Custom Compute

#### → What's new?

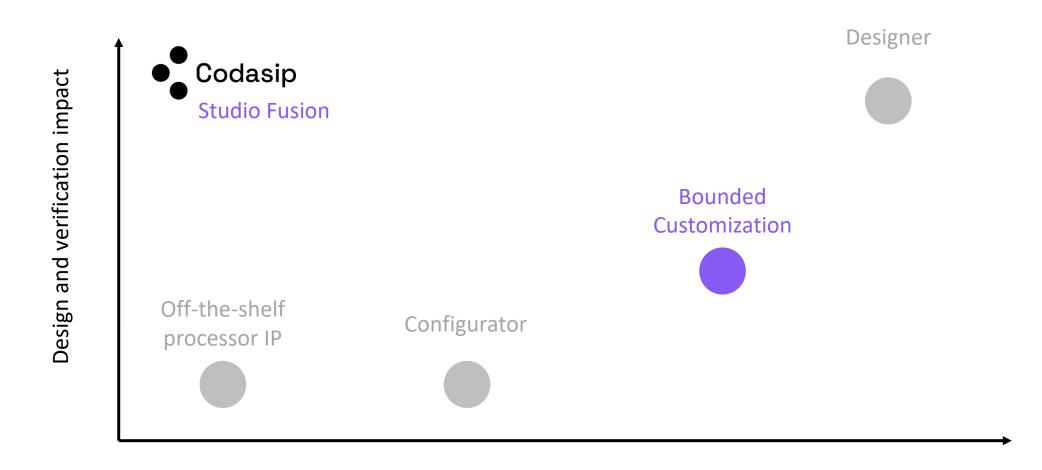

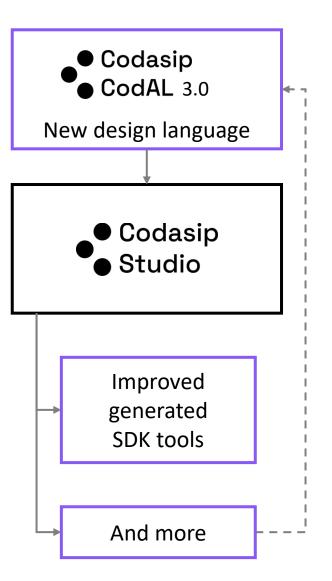

Codasip Studio Fusion introduces unique processor design and verification features for unparalleled productivity

CodasipStudio

- → Improved software development tools

- → Adds levels of customization

Codasip L110 delivers best-in-class performance for small-area and low-power applications

- → 50% higher performance per watt \*

- → 20% smaller code size\*

- → Easy and quick to customize and verify

CodasipRISC-V Processors

<sup>\*</sup>compared to similar cores on the market

Codasip's "tools first" business model has proven to have legs, and, arguably, the company is more attractive today than other RISC-V IP rivals(...)

The ability to customize within boundaries should both de-

The ability to customize within boundaries should both derisk and speed up core development.

Jon Peddie Research, June 2024

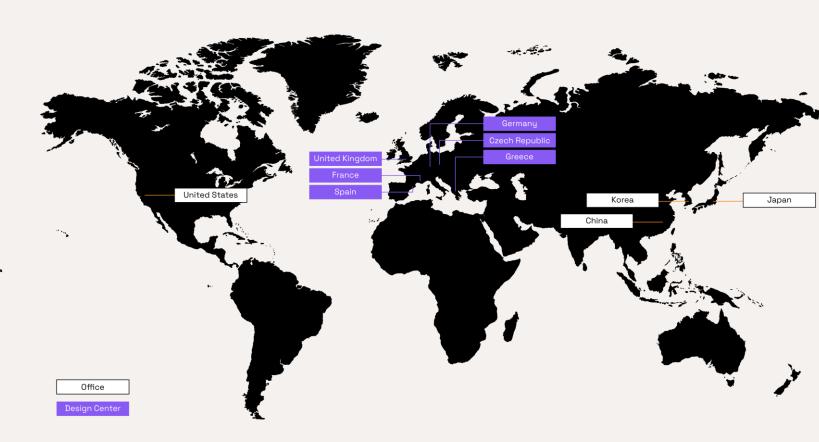

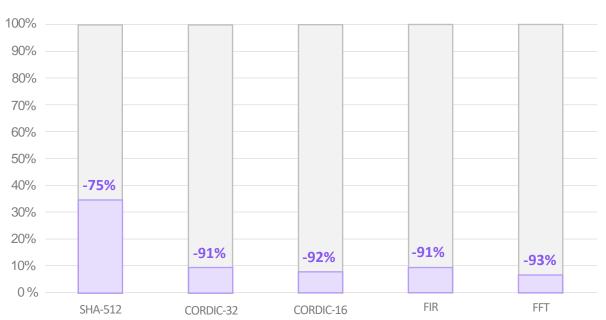

#### → The power of RISC-V

#### Omdia May 2024:

- 17 billion RISC-V processors shipped in 2030

- RISC-V processors in automotive applications

to increase in volume by

66% annually

SDH Group: 2024 RISC-V Market Analysis Report

# → RISC-V weak points ...up until now

#### Performance

HW/SW co-optimization raises the bar for application-specific performance

#### Number of designs

Custom Compute makes up for the gap through rapid creation of application-specific designs

#### Quality

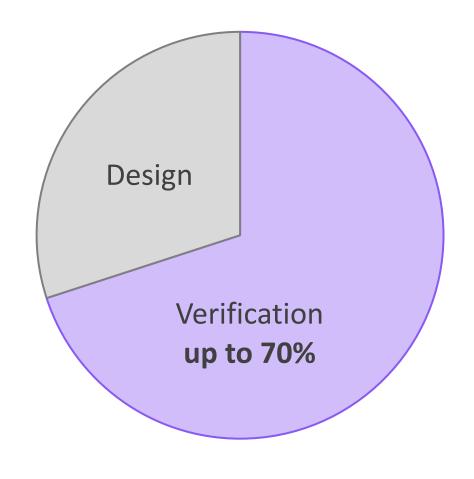

Bounded Customization shortens time-to-market for fully verified custom cores

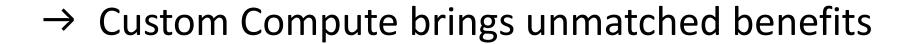

#### Performance Density Increase

#### **Energy Consumption Reduction**

Baseline RISC-V processor

**Customized RISC-V processor**

Which is why automation (edA) is so important

## → Introducing bounded customization

**Customization freedom**

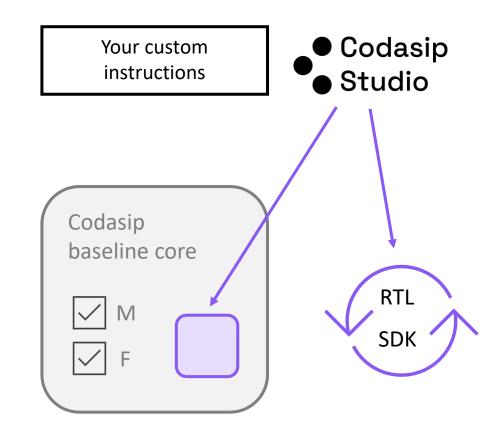

#### → Verification and Custom Bounded Instructions

- Custom instructions on top of the core configuration space

- Instruction within bounds cannot harm the baseline core – no re-verification!

- Easy-to-use verification framework to verify custom instructions

© 2024 Codasip. All rights reserved.  $\triangle$  Confidential – Under NDA

### → New generation - Codasip Studio Fusion

So elegantly simple even software developers can create a Custom Bounded Instruction core with Fusion.

© 2024 Codasip. All rights reserved.  $\triangle$  Confidential – Under NDA

### We have solved the puzzle

Flexible

High performance

High quality

Safe and secure

Completeness that will not cost you an arm and a leg

$\rightarrow$

Thank you!