# The Silicon Commons Build Together, Build Well & Build Securely

Dr. Gavin Ferris, CEO @ lowRISC CIC

### Open ISA to Open Source Silicon

## Commercial-Grade Open Source Silicon Is Here

"Nuvoton Technology

Corporation [...] announced

today that Google's ChromeOS

plans to use the first

commercial chip built on the

OpenTitan open source secure

silicon design as an evolution of

its security chip for

Chromebooks."

Nuvoton, May 2024

"Hardware security is something we don't compromise on. We are excited to partner with the dream team of Nuvoton, a valued, historic, strategic partner, and lowRISC, a leader in secure silicon, to maintain this high bar of quality."

Prajakta Gudadhe Sr Director, ChromeOS Platform Engineering

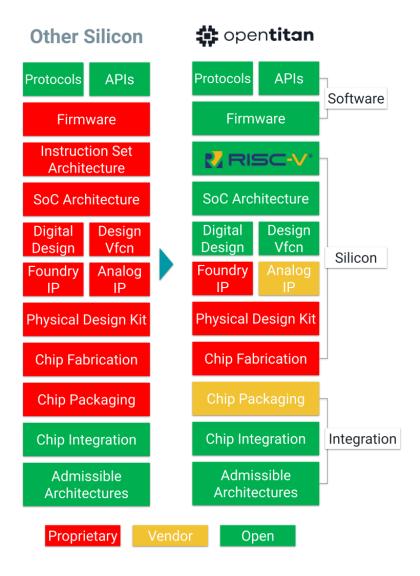

# The Silicon Commons® Approach

Code review and approval process

Open development with clear IP provenance

Governance structure

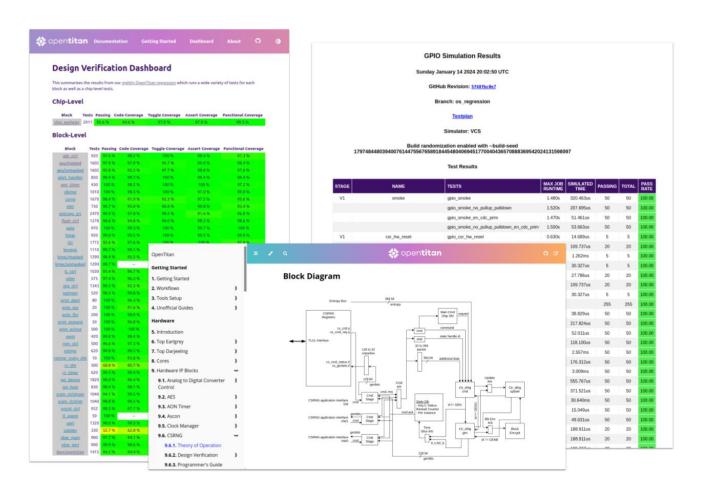

**Continuous Integration testing**

Training for contributors

Accessible verification collateral

Extensive documentation

Permissive licensing to encourage re-use

## World's Most Active Open Silicon Project

RTL · design verification collateral · documentation · low-level firmware · tests

25,000+

total commits

(Ibex + OpenTitan)

250+

contributors

(lbex + OpenTitan)

7,200+

GitHub issues

(Ibex + OpenTitan)

3,700+

GitHub stars

(lbex + OpenTitan)

440,000+

lines of SystemVerilog (Digital Design and Verification for Ibex + OpenTitan) 40,000+

regressions

(run multiple times per week)

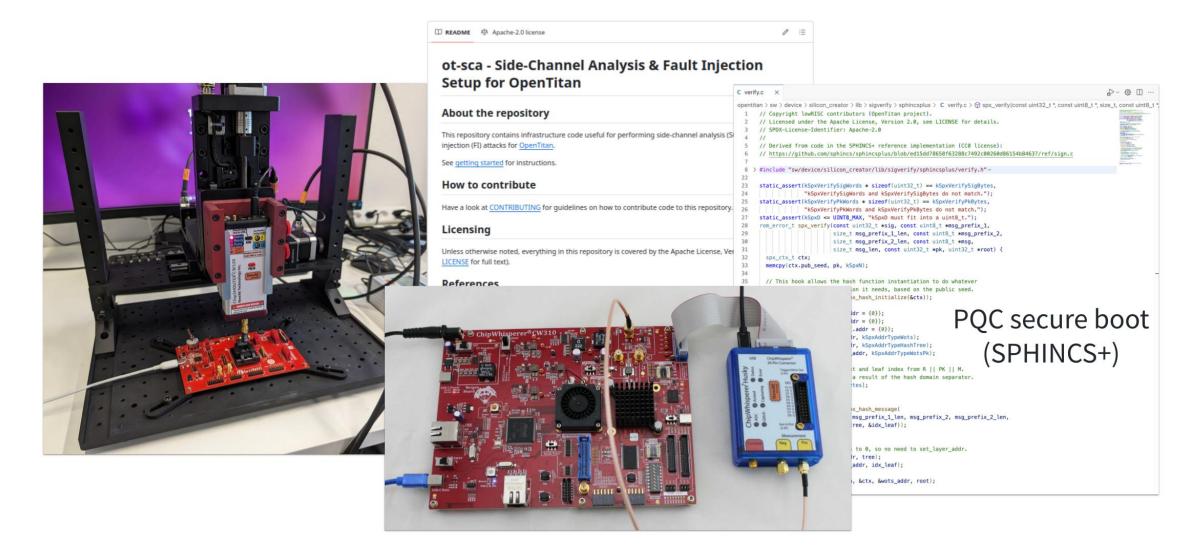

## **Build Securely**

### Timeline

#### 2019

Public launch

Founding partners: Google, G+D, Western Digital, ETH, Nuvoton & lowRISC

#### 2021

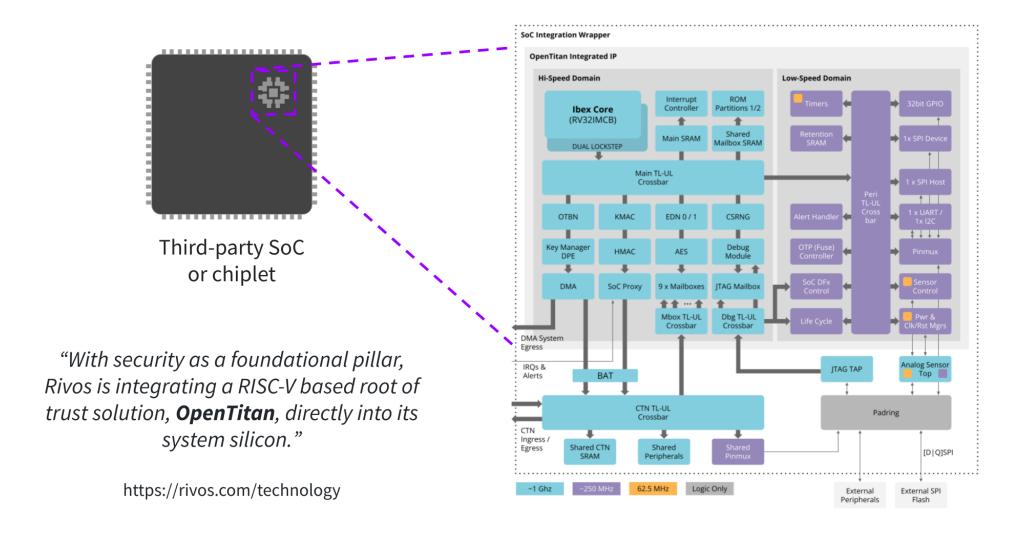

Rivos joins partnership Planning for integrated variants begins

#### 2023

zeroRISC joins partnership Earl Grey ES tapeout Darjeeling public release

#### 2025

Earl Grey volume availability

Chromebook integration

Development of next-gen designs

#### 2018

Project starts (STWG)

ETH donates zero-riscy

Google joins the lowRISC board

#### 2020

Seagate joins partnership NewAE CW310 support is added

#### 2022

Winbond joins partnership

Earl Grey feature freeze

NewAE acquisition by lowRISC completes

#### 2024

Earl Grey ES silicon validation and security evaluation

Rivos integrating OpenTitan into its system silicon

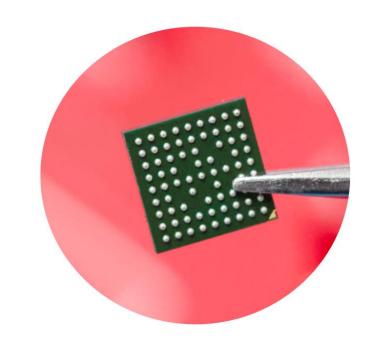

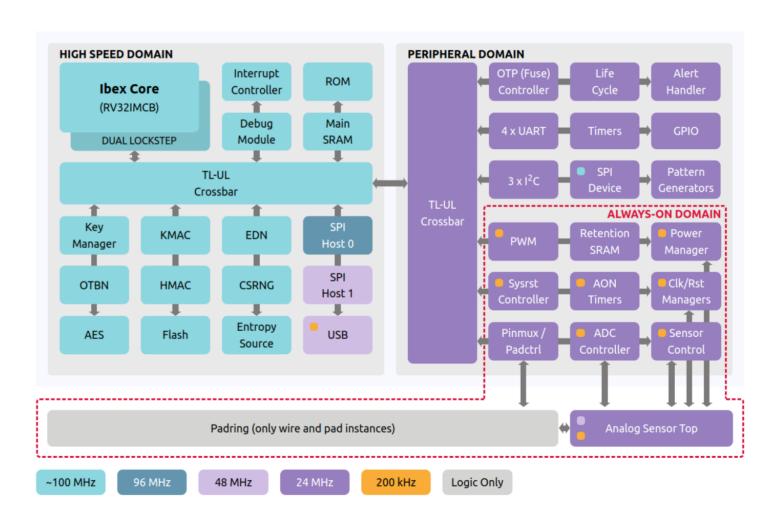

## The First OpenTitan® Chip Design: Earl Grey

# Integrating OpenTitan®: Darjeeling and Beyond

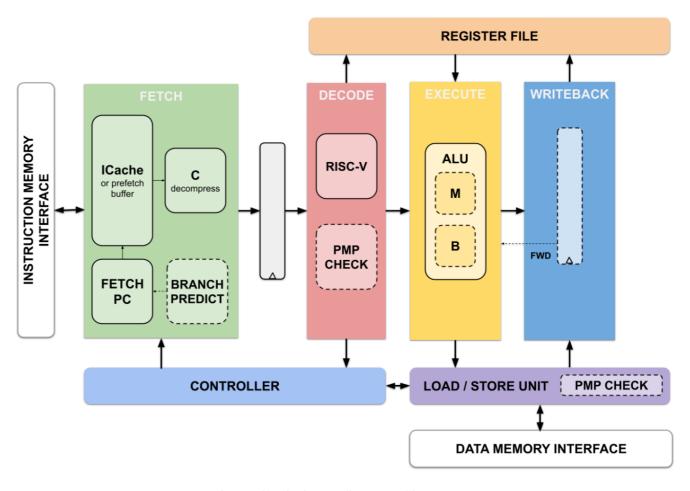

### RISC-V at the Core: Ibex®

Highly configurable **open source** RV32IMCB core with security features that include:

- → Instruction cache memory scrambling

- → Dual-core lockstep

- → Data independent timing

- → Dummy instruction insertion

- → Bus and register file integrity

- → Hardened PC

https://github.com/lowRISC/ibex

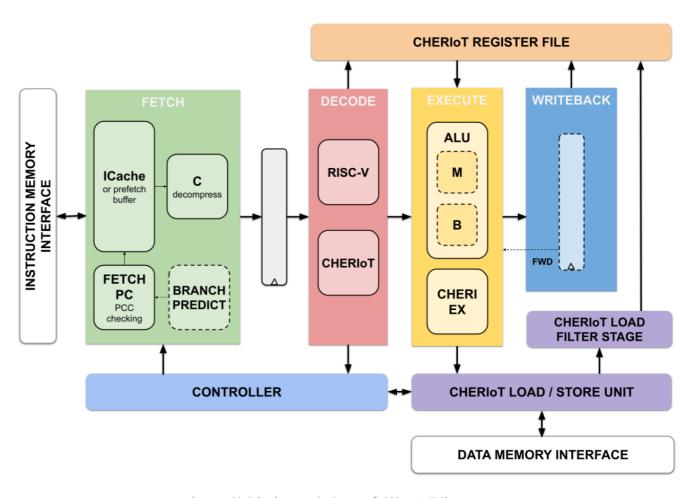

## Evolving Ibex®: Memory Safety with CHERIoT

"This is truly important foundational work, as it will help make CHERIoT-Ibex the world's first production grade, open-source CHERI-enabled microcontroller core. We're looking forward to seeing it broadly leveraged in commercial designs, bringing much-needed hardware security — in an efficient manner — to a broad swathe of critical applications."

> Tony Chen Partner Security Architect, Microsoft

https://github.com/microsoft/CherIoT-ibex

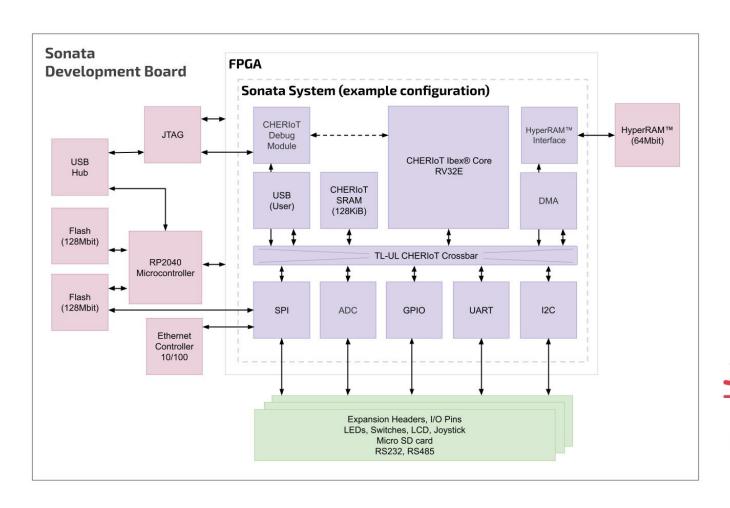

# Securing Operational Technology: Sonata

### sunburst-project.org

DSbD/UKRI Project Grant Number: 107540

### Build Together, Build Well & Build Securely

lowRISC's full-stack engineering team can help develop and integrate open source silicon IP in **your** products!

Contact us at info@lowrisc.org to find out more