### Impact of the four French RISC-V Contests on Education and Research

J. Quévremont<sup>1</sup>, N. Ventroux<sup>1</sup>, J.-M. Philippe<sup>1</sup>, S. Jacq<sup>1</sup>, P. Benoit<sup>2</sup>, A. Pinna<sup>3</sup>, S. Pillement<sup>4</sup>

<sup>1</sup> Thales Research & Technology, F-91120 Palaiseau, France

<sup>2</sup> Université de Montpellier, CNRS, LIRMM UMR 5506, CNFM, F-34090 Montpellier, France

<sup>3</sup> Sorbonne Université, CNRS, LIP6, GDR SoC2, F-75005 Paris, France

<sup>4</sup> Nantes Univ, CNRS, IETR UMR 6164, GDR SoC2, F-44000 Nantes, France

## WHY A RISC-V STUDENT CONTEST IN FRANCE?

Encourage students working on processor architecture Promote RISC-V and OpenHW in academic laboratories Expand RISC-V and OpenHW communities in France Strengthen RISC-V cooperation between academics and industry

Ease access to RISC-V educational resources

#### THE CONTEST AT A GLANCE

Based on CVA6, an open-source RISC-V application core, curated by members of the OpenHW Group, targeting industrial-grade quality

Open-source technical kit available from Thales in November

Teams of 2-4 students registered by their universities and supervised by a professor

6 months to design a solution to address a specific challenge Prize and award for the 2 best ranked teams

Some universities include the contest in the curriculum time. Other teams work in their leisure.

| Year          | CVA6 Challenge                                         | Teams |

|---------------|--------------------------------------------------------|-------|

| 2020-<br>2021 | Optimize CVA6<br>performance and<br>area               | 12 •  |

| 2021-         | Optimize CVA6<br>energy efficiency                     | 12 •  |

| 2022-<br>2023 | Defeat cyber-<br>attacks under<br>Zephyr OS            | 19 •  |

| 2023-<br>2024 | Accelerate digit recognition (CNN) with ISA extensions | 13 •  |

#### LESSONS LEARNED

- Main difficulty: set up the complete framework to use CVA6 with the required tools

- Reuse same tools and FPGA board every year

- Make setup as easy as possible (e.g. Docker containers)

- Get a partnership to provision EDA and FPGA board

- Careful selection of every year's topic to motivate students and focus on computer architecture, not applications

- Choose a duration as long as possible (e.g. 6 months) to accommodate diverse academic calendars

- Evaluate results according to a single KPI (e.g. acceleration factor) to keep focus and avoid subjectivity

- Replay students' results in a reference environment to compensate for local variations (tool versions...)

#### A POPULAR CONTEST

20 universities

180 students

56 teams

50 supervisors

over 4 years

#### **IMPACT SURVEY**

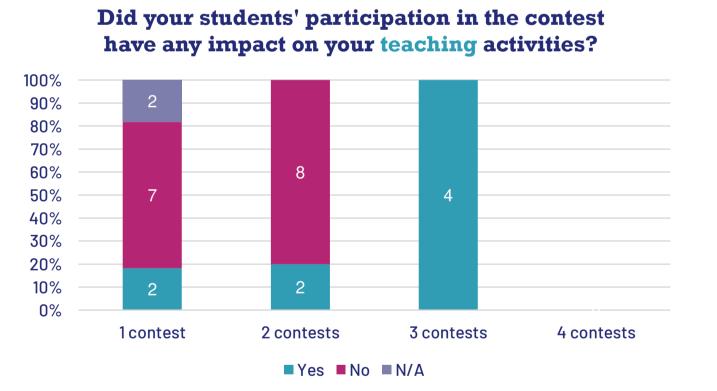

Did your students' participation in the contest have any impact on your teaching activities?

Yes, 32%

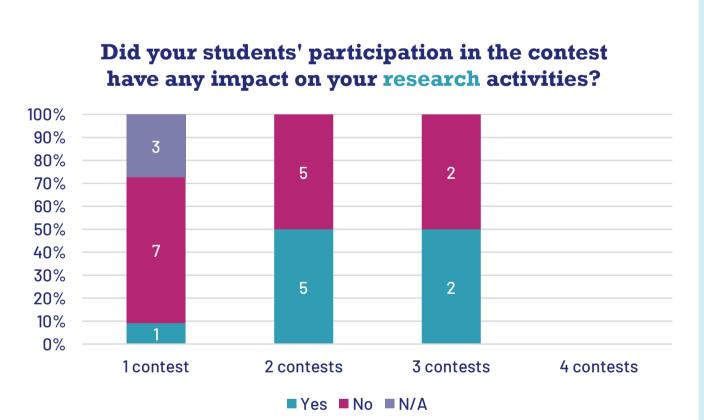

Did your students'

participation in the contest

have any impact on your

research activities?

Yes, 32%

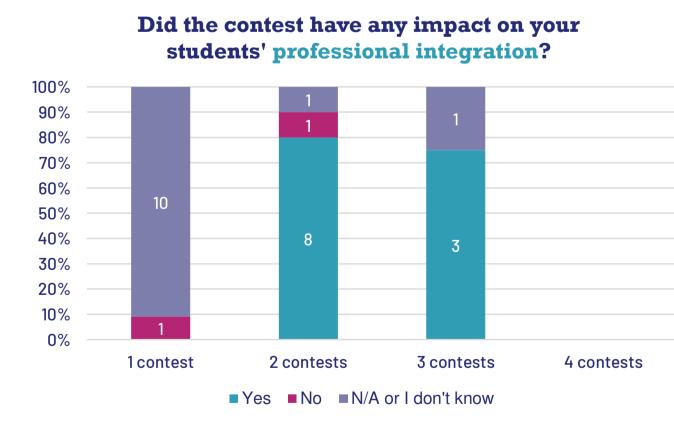

Did the contest have any impact on your students' professional integration (job, internship, PhD thesis...)?

Yes, 44%

# IMPACT INCREASES WITH #PARTICIPATIONS

#### MOTIVATIONS TO ATTEND

RISC-V

Processor architecture

Year's specific challenge

Competitive spirit

Real-life complex industrial project