# One Student One Chip

## Start From Scratch Create Your Own

Website

PPT

E-mail: ysyx@bosc.ac.cn

- Open Source and Free of Charge

- Sign Up Beyond 7000+ Covering 350+ Universities

- SW-HW Co-design and Full Design Flow For

- No Requisites For Enrollment, Everyone is Welcome

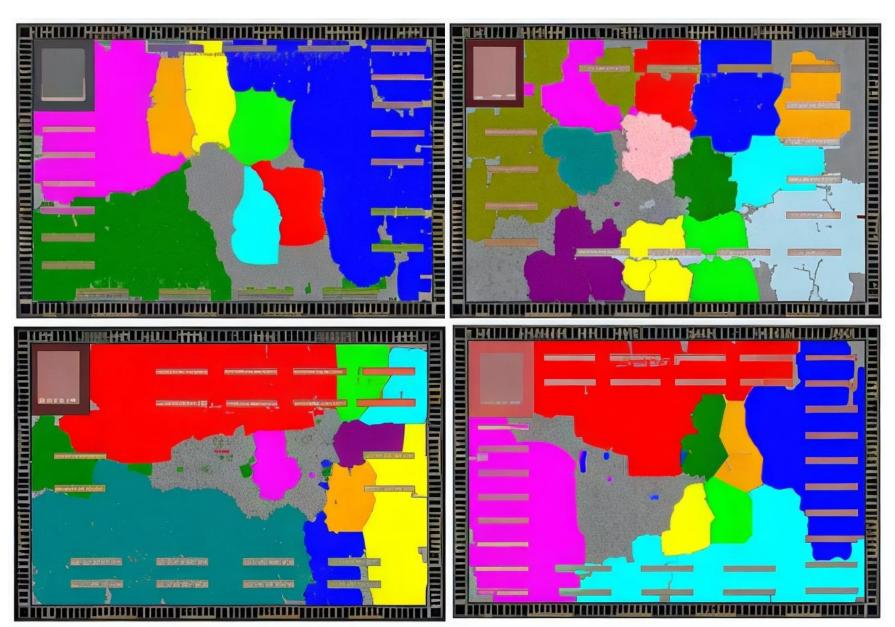

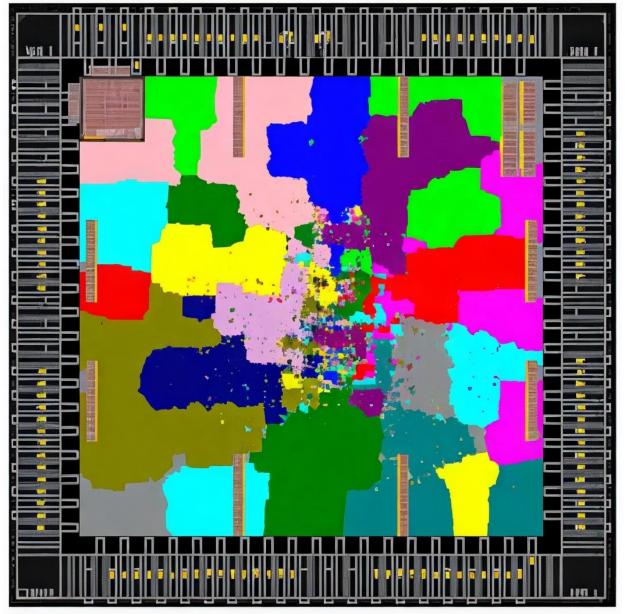

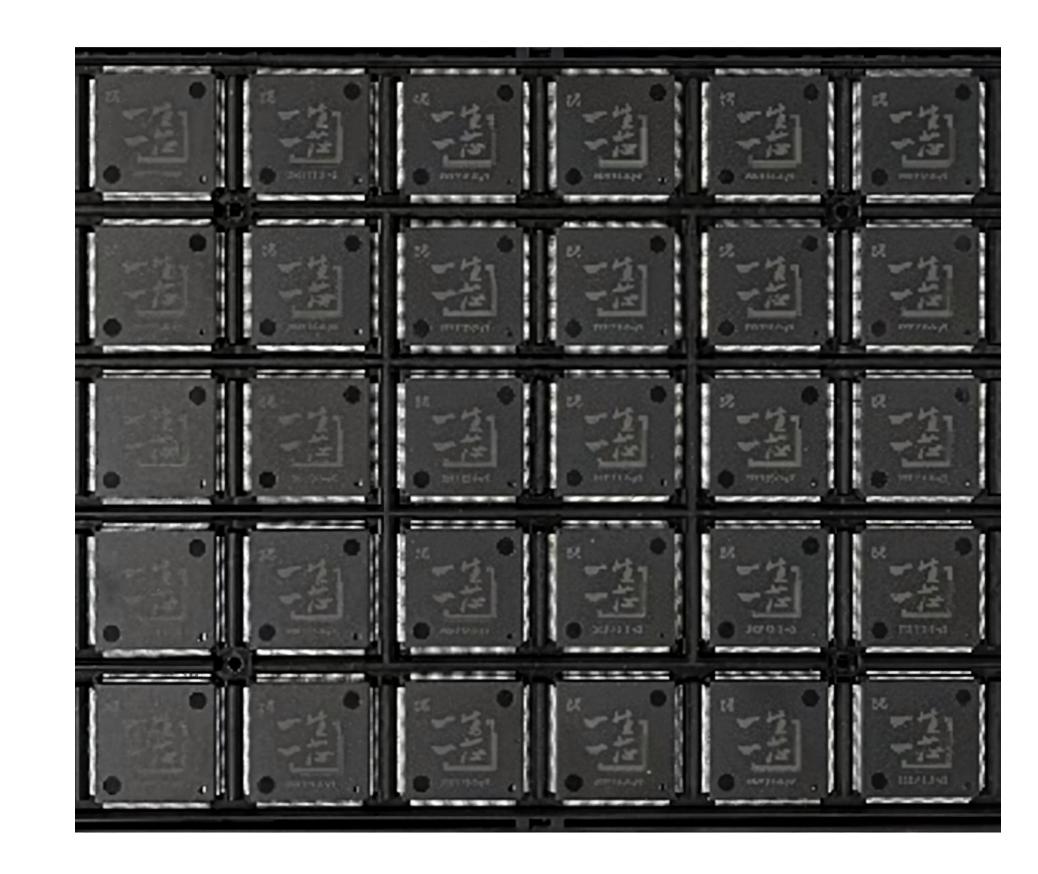

The 3<sup>rd</sup> Session of OSOC (1st Batch, 39 cores)

The 3<sup>rd</sup> Session of OSOC (2<sup>nd</sup> Batch, 9 cores)

The 4<sup>th</sup> Session of OSOC (1<sup>st</sup> Batch, 13 cores)

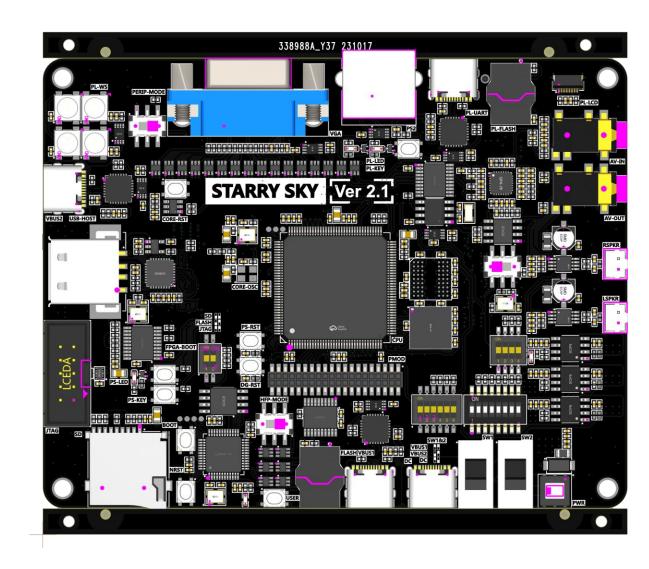

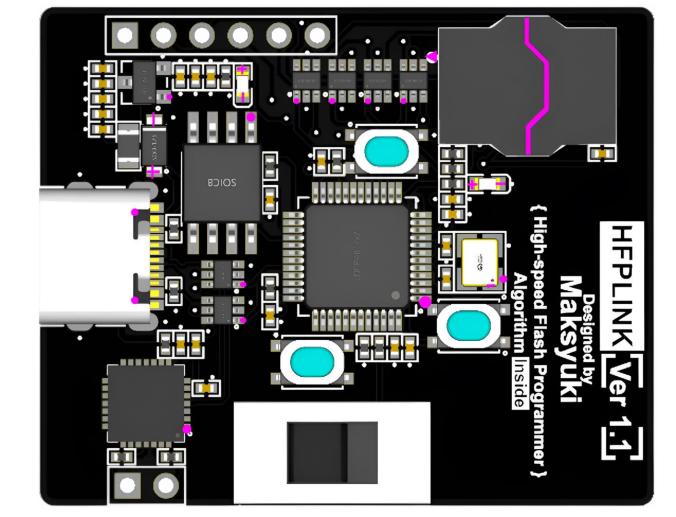

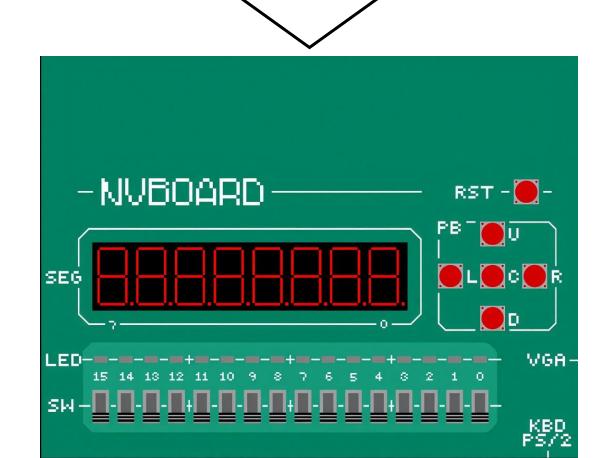

PCB Board Design&& Testing

### Preliminary Stage

- GNU/Linux

- MakeFile

- Digital Circuit

- Verilog/Chisel

- Verilator

- **□** C/C++

- **■** Simulator

#### Basic Stage

- Simulator

- Library Funcs Trace/DiffTest

- Single CPU

- Devices

- RT-Thread

- Benchmarks

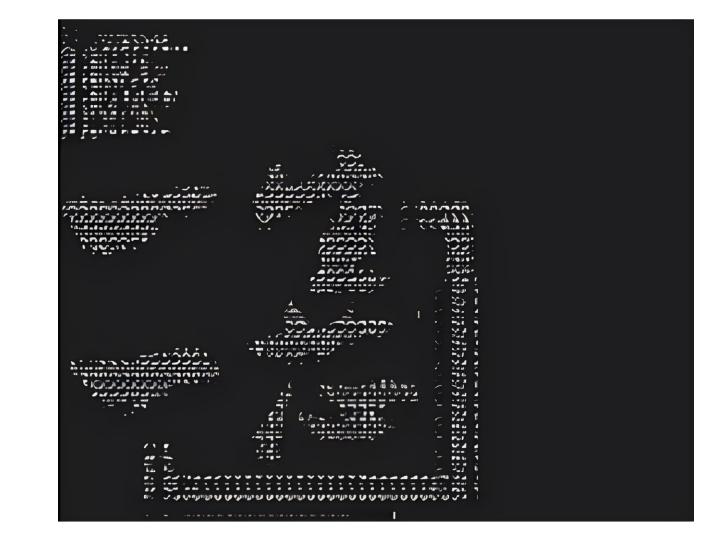

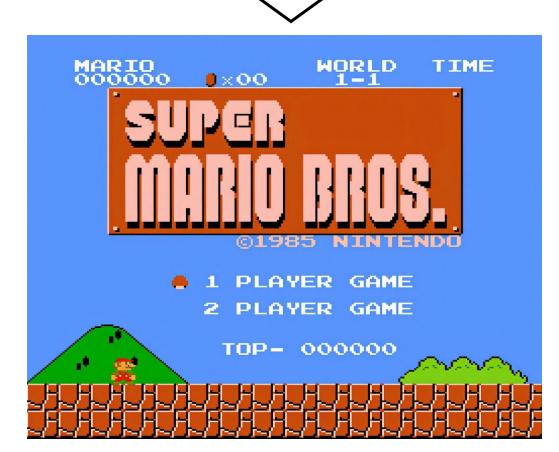

- FC Games

#### Advanced Stage

- CSR

- Simple OS

- AXI4 Bus

- SoC

- Cache

- Multiplier

- Pipeline CPU

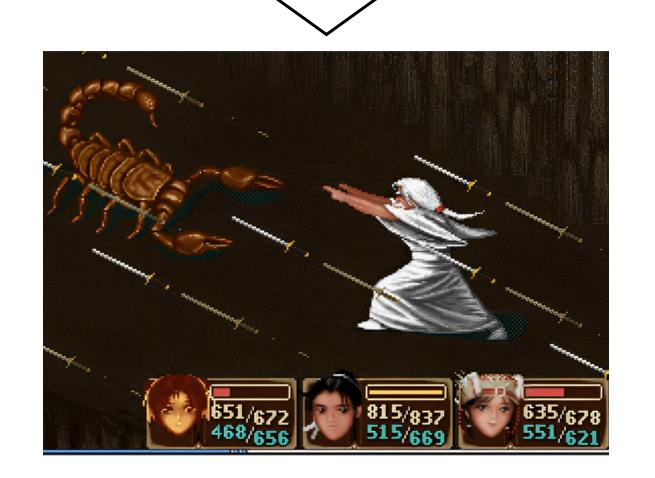

- OS Games

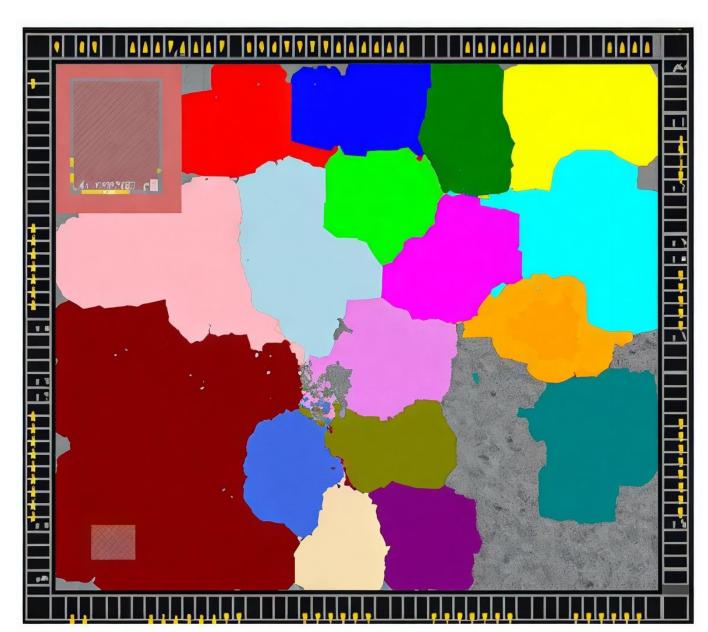

Chips of OSOC