# Formal Verification of Security-Properties on RISC-V Processors

Czea Sie Chuah, Christian Appold, and Tim Leinmüller

## Motivation

- High security demands of upcoming applications, e.g. autonomous driving

- In past years several famous bugs and security-vulnerabilities in processors found

- Design flaws can be exploited by attackers

- RISC-V security verification guidance needed

- Our work increases RISC-V security by:

- 1. Comprehensive identification of security-critical functionality

- 2. Derivation of properties for security-critical functionality correctness

- 3. Formal verification of the properties

Collaboration with TUM Chair of Security in Information Technology

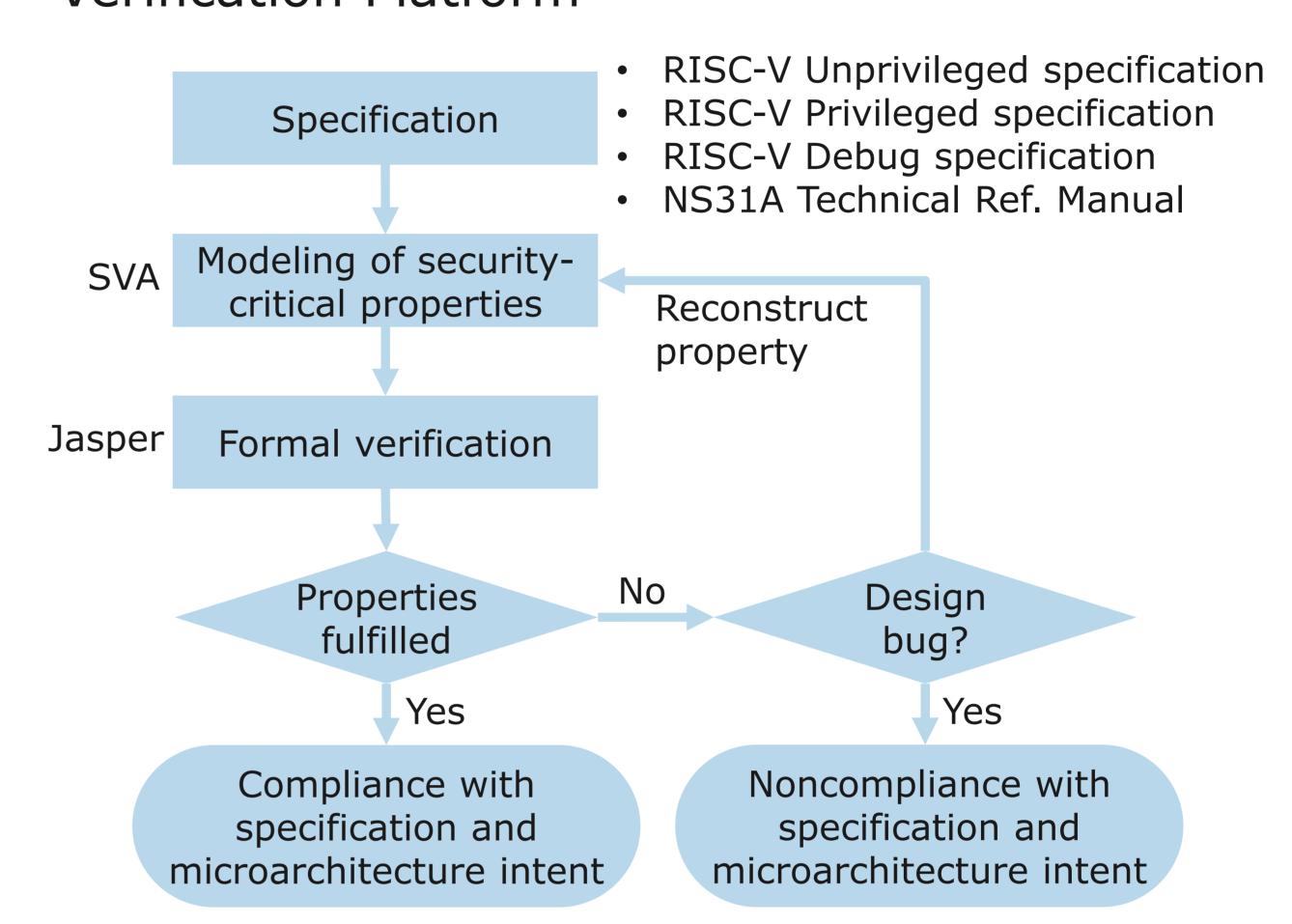

## Methodology

- Akaria NS31A commercial RISC-V processor verified

- 32-bit, 4 pipeline stages, 3 privilege modes

- Verification using Cadence Jasper Formal Verification Platform

## Work presents comprehensive set of securityproperties for RISC-V security hardening

## Security-Properties

• Identified security-critical functionality:

| Instruction<br>Execution                | CSRs                                    | <b>Debug Operation</b>                                       |  |

|-----------------------------------------|-----------------------------------------|--------------------------------------------------------------|--|

| Check instruction flow through pipeline | Comply with CSR access rules            | Comply with Debug<br>CSR access rules                        |  |

| Exception and Interrupt                 | <b>Mode Transition</b>                  | PMP                                                          |  |

| Proper handling required                | Mode transition rules<br>need to be met | Access control rules<br>for memory regions<br>need to be met |  |

| Control Flow                            | Register Update                         | Memory Access                                                |  |

| Correct setting of program counter      | Correct target register is updated      | Value and address of memory transfers as intended            |  |

Example mode transition SVA properties:

#### Results

- Used Jasper settings:

- Jasper contains formal verification engines for full-proofs and bug-hunting

- engines use different model checking techniques, e.g. BDD or SAT-based

- verified all properties of a category in parallel

- use of several Jasper engines in parallel

- automatic choosing of most suitable engine

- We identified 1146 properties and grouped them under 9 categories

- Achieved full-proof for passing properties

- Runtime: Control Flow < 24h, others < 4000s

|                         | Properties |      |          |  |

|-------------------------|------------|------|----------|--|

| Categories              | Assertion  | Pass | Fail     |  |

| Instruction Execution   | 10         | 10   | 0        |  |

| CSR                     | 394        | 280  | 114      |  |

| Debug Operation         | 14         | 14   | 0        |  |

| Exception and Interrupt | 87         | 87   | o 3 bugs |  |

| Mode Transition         | 13         | 13   | o found  |  |

| PMP                     | 574        | 574  | 0        |  |

| Control Flow            | 9          | 8    | 1        |  |

| Register Update         | 33         | 33   | 0        |  |

| Memory Access           | 12         | 12   | 0        |  |

| Total                   | 1146       | 1031 | 115      |  |

SVA: System Verilog Assertions, CSR: Control and Status Register, PMP: Physical Memory Protection