# Application Specific ISA Extensions in RFID Edge Processing

Sammy Johnatan Carbajal Ipenza, Tiberio Fanti

#### **NXP Semiconductors Austria GmbH & Co KG**

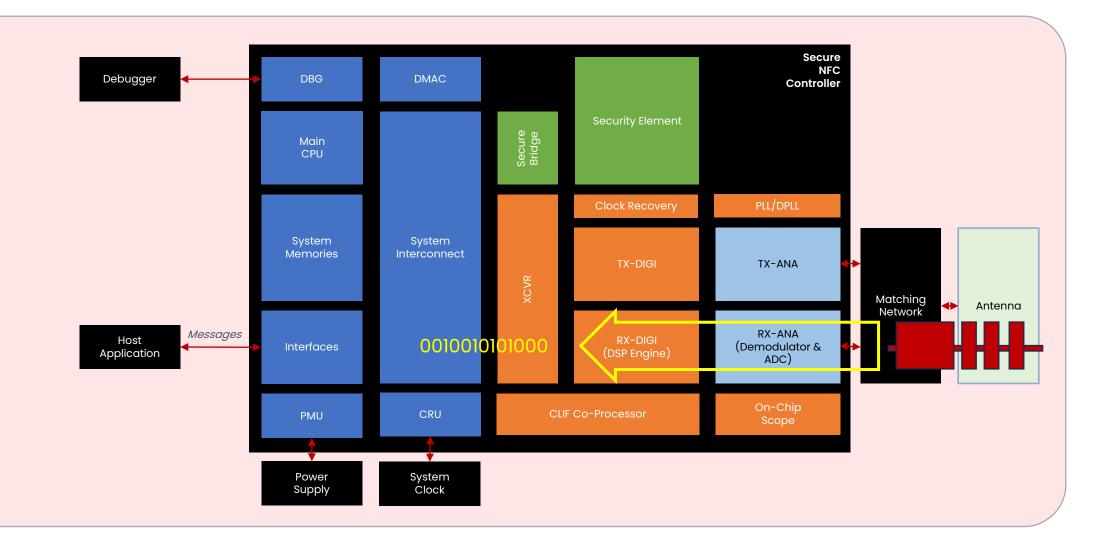

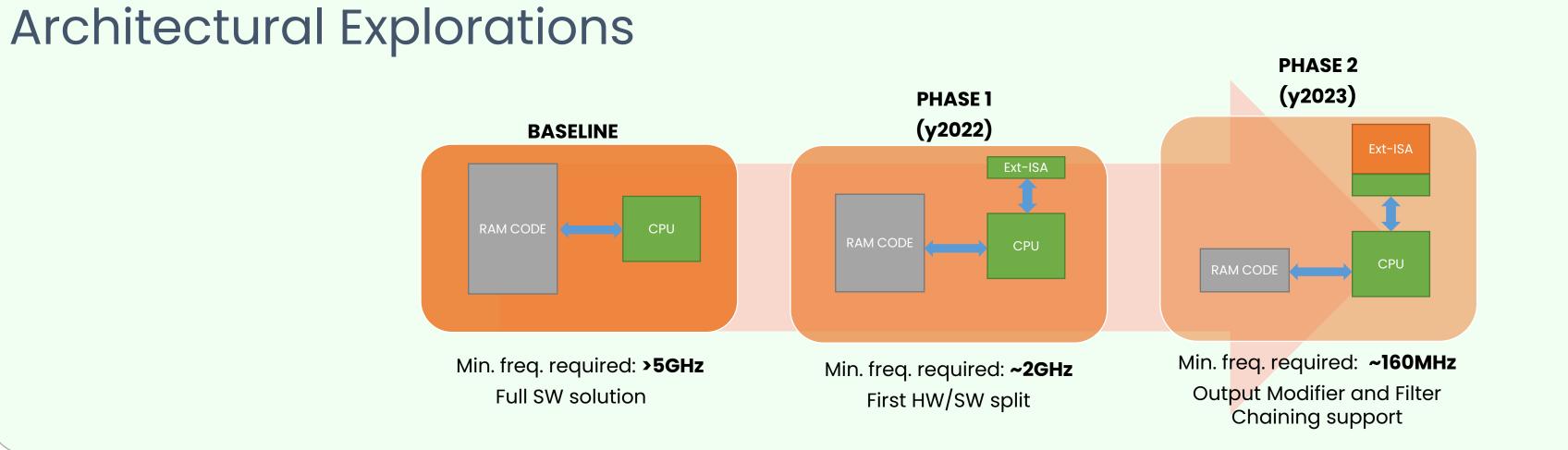

### State of Art in NFC Modems Architectures

- Full custom digital logic solutions

- Massive use of DSP structures, configuration registry and debug infrastructure

- High functional density per silicon area

- Highly performing

- Hard-coded functionality

- Reader and Card-Emulation modes

- WLC

- Runtime automatic gain, phase and DCO control loops

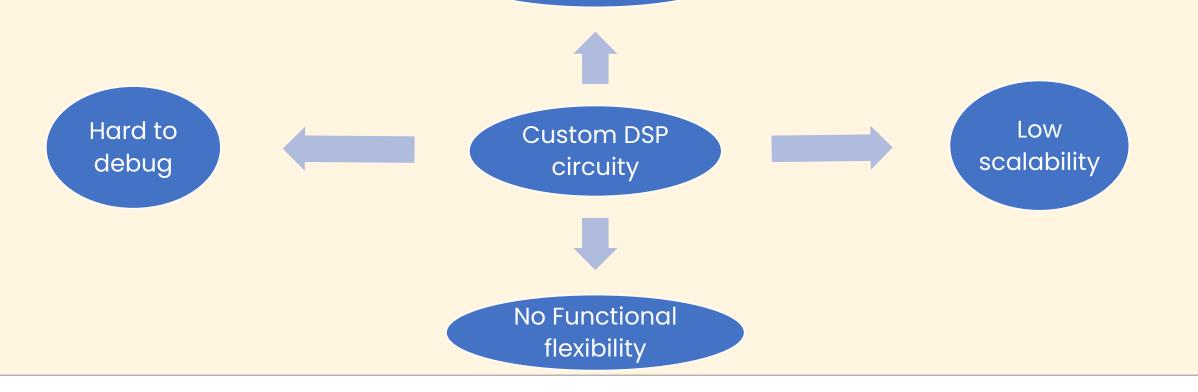

#### A novel architectural

Any functional improvement or problem fix not solved by FW requires a silicon respin!

customizable

#### approach is necessary, that aims at:

- Scalability

- In-field reconfiguration

- Testability

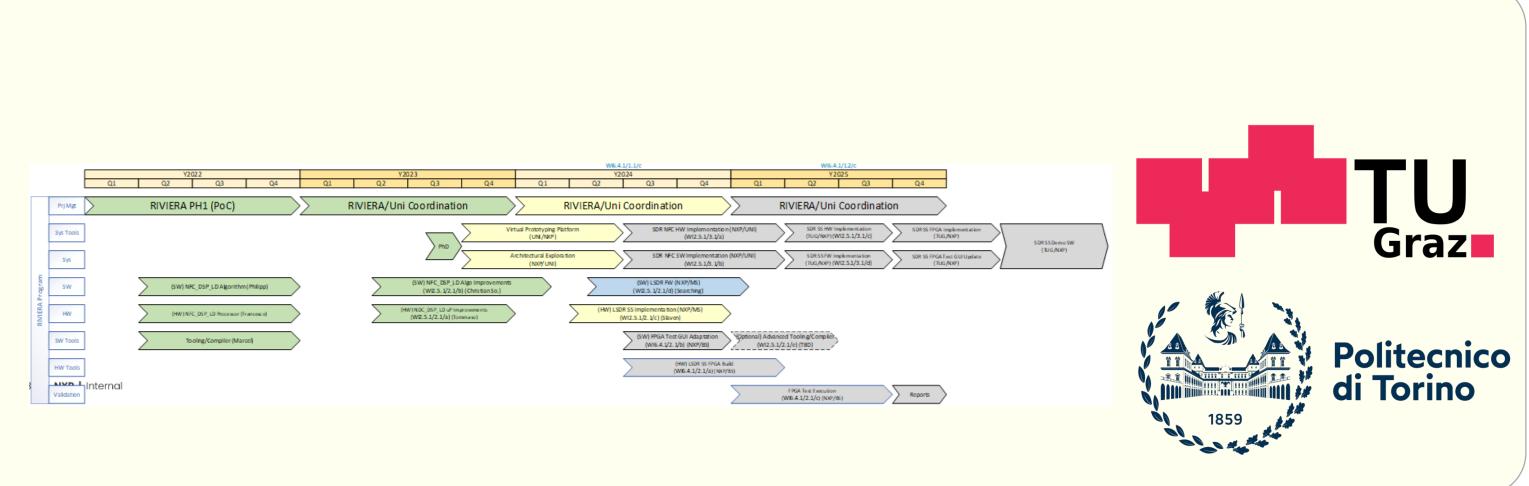

## Students' Collaboration Plan (NXP RIVIERA)

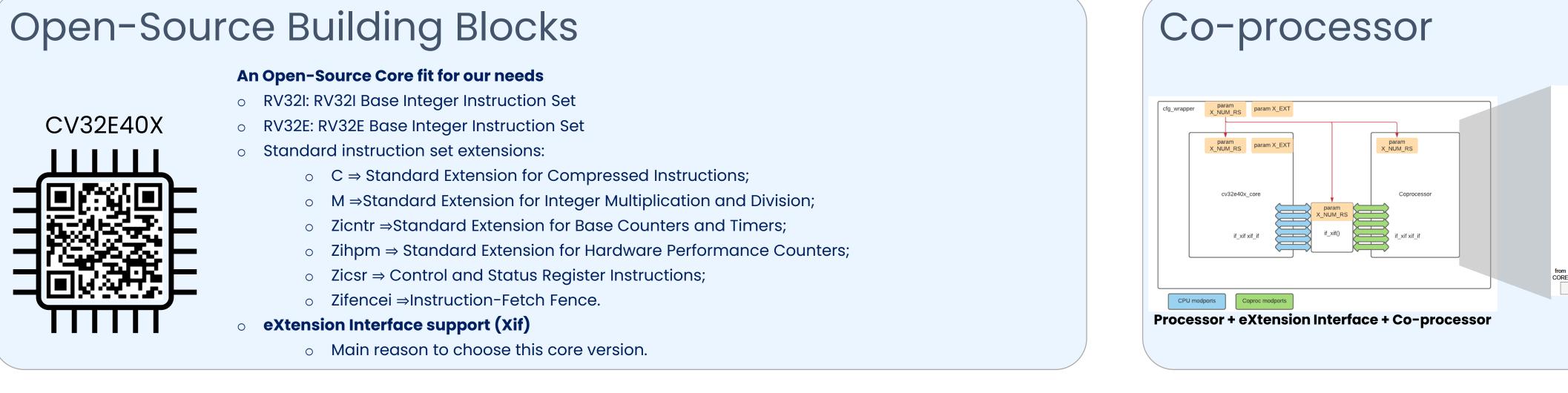

- **RIVIERA** is the acronym for "**RI**SC-**V** ISA Extensions for **R**FID **A**pplications". Ο

- NXP Austria academical program run with **TU-Graz** and **Politecnico di Torino**.

- Supported by NXP France on FPGA proto board.

- Concept: Architectural investigations aiming to SW Defined Radio for NFC Applications.

- o Duration: 4 years, mostly framed into TRISTAN Project.

- Multiple master, bachelor HW, SW and Validation thesis works.

- Status: 2 generations of master HW and SW student run.

- Next stage: MCU system build, mapping on FPGA, bring-up and validation.

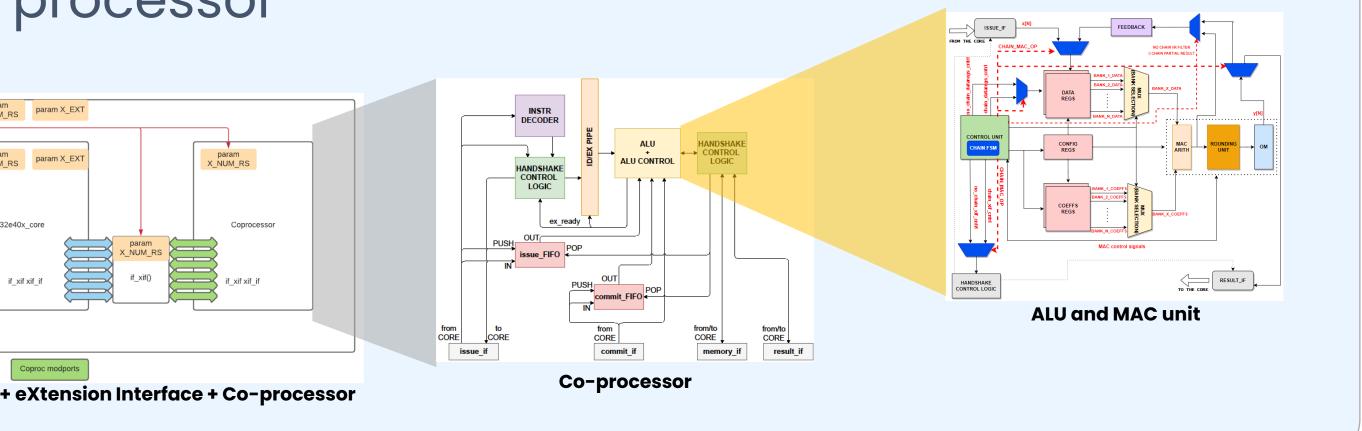

#### **RISC-V co-processor instructions (Ext-ISA)**

| Description         | Funct7 | Rs2         | Rs1        | Funct3 | Rd     | Opcode |                  |

|---------------------|--------|-------------|------------|--------|--------|--------|------------------|

|                     | 31 25  | 24 20       | 19 15      | 14 12  | 11 7   | 6 0    |                  |

| clear_data          | 0      | х           | bank_index | 0      | х      | 0x2b   |                  |

| clear_coeff         | 1      | х           | bank_index | 0      | х      | 0x2b   | Updated in Phase |

| set_nfeed           | 2      | n_feed      | bank_index | 0      | х      | 0x2b   |                  |

| set_rounding        | 3      | nbits_cut   | bank_index | 0      | Х      | 0x2b   |                  |

| set_simd*           | 4      | simd        | bank_index | 0      | Х      | 0x2b   |                  |

| load_data_mem       | 0      | mem_addr    | bank_index | 1      | Х      | 0x2b   |                  |

| load_coeff_mem      | 0      | mem_addr    | bank_index | 2      | х      | 0x2b   |                  |

| load_data_reg       | 0      | input_data  | bank_index | 3      | х      | 0x2b   |                  |

| load_coeff_reg      | 0      | input_coeff | bank_index | 4      | х      | 0x2b   |                  |

| exec_mac            | 0      | х           | bank_index | 5      | output | 0x2b   |                  |

| load_exec_data_mem  | 0      | mem_addr    | bank_index | 6      | output | 0x2b   |                  |

| load_exec_data_reg* | 0      | input_data  | bank_index | 7      | output | 0x2b   | Updated in Phase |

#### Next Steps

RIVIERA Phase-3 plan of record:

- Build of a MPU subsystem, based on the core + coprocessor;

- Development of a full SW stack to support the decoding algorithm; 0

- HW & SW integration on a virtual verification env (SV-UVM TB)

- Test env setup based on a FPGA prototyping platform; 0

- Validation and performance analysis. 0

TRISTAN Project has received funding from the Chips Joint Undertaking (Chips-JU) under the grant agreement nr. 101095947. Chips-JU receives support from the European Union's Horizon Europe's research and innovation programme and Austria, Belgium, Bulgaria, Croatia, Cyprus, Czechia, Germany, Denmark, Estonia, Greece, Spain, Finland, France, Hungary, Ireland, Israel, Iceland, Italy, Lithuania, Luxembourg, Latvia, Malta, Netherlands, Norway, Poland, Portugal, Romania, Sweden, Slovenia, Slovakia and Turkey.