# **RISC-V at BOSC: Achievements and Challenges** Shan Liu, Senior Design Engineer, BOSC

# **BOSC Introduction**

# Missions

**Misson 1:** Develop open-source & high-performance RISC-V CPUs ---- Xiangshan CPU family.

**Misson 2:** Build-up open-source RISC-V ecosystem.

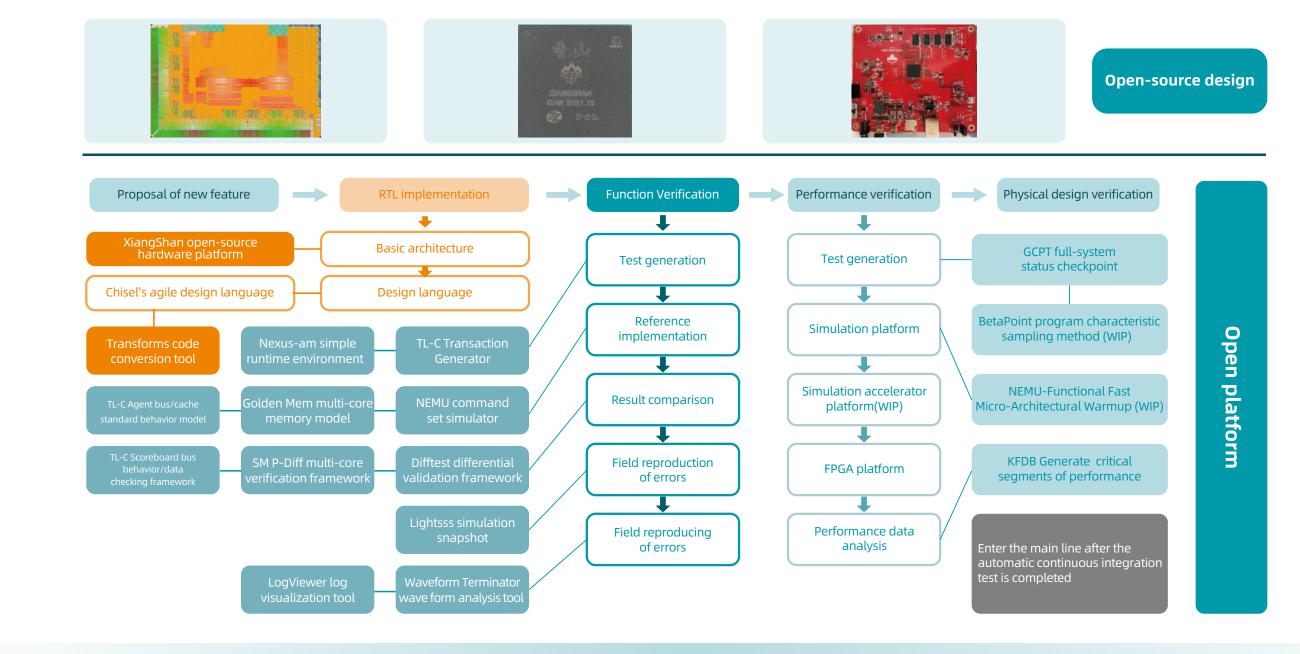

- Development infrastructure & tools

- Chip design methodologies: open-source verification &

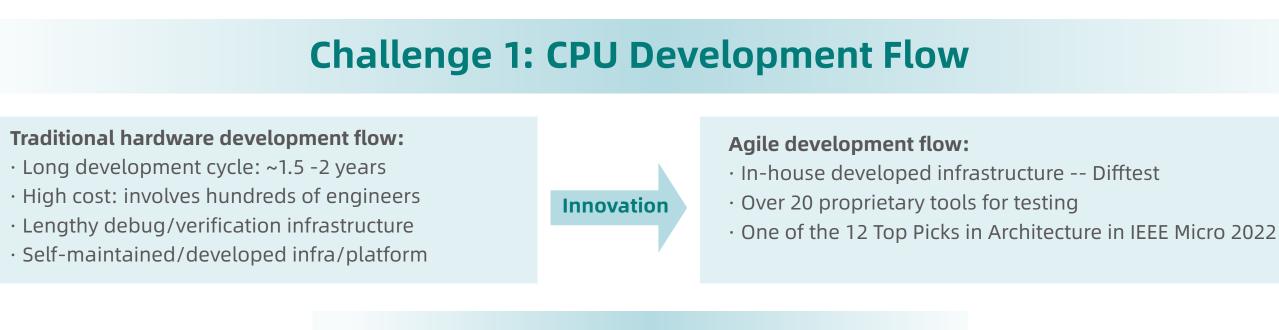

Agile(a.k.a Minjin) development flow

Challenges

## Agile Infrastructure

## Partnership & Cooperation

#### International cooperation of RISC-V

BOSC is deeply involved in community organizations such as the RISC-V International, and becoming its Premier member as well as a member of the RISE Foundation. It is also a member of OpenHW and a partner of embedded world China, and is actively participating in the strategic planning and technical route formulation of international RISC-V open source organizations.

RISC-V A RISE embeddedworldChina

## **Achievements**

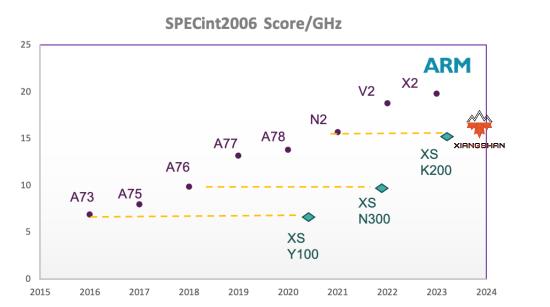

## Xiangshan CPU Family

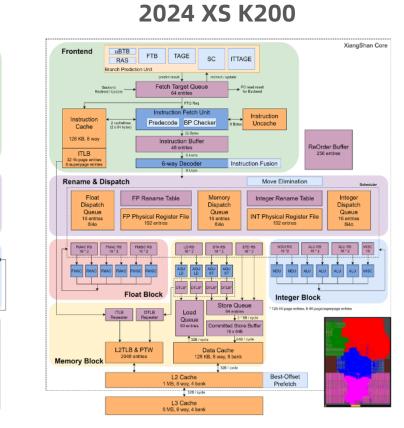

#### 2021 XS Y100

EOL

#### 2022 XS N300

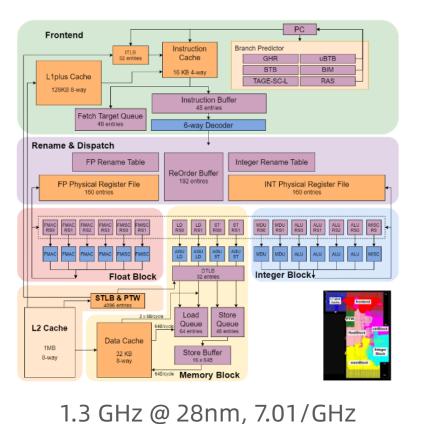

#### GHR uBTB BTB BIM TAGE-SC-L RAS

ename & Dispatch FP Rename Table Integer Rename Table

#### 2.1GHz @ 14nm, 9.55/GHz **Balanced Perf & Efficiency** (v.s. ARM A76)

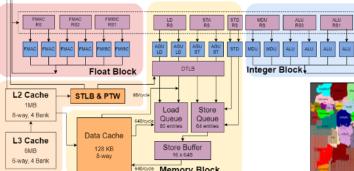

3GHz @ 7nm, 15/GHz **Ultimate Performance** (v.s. ARM N2)

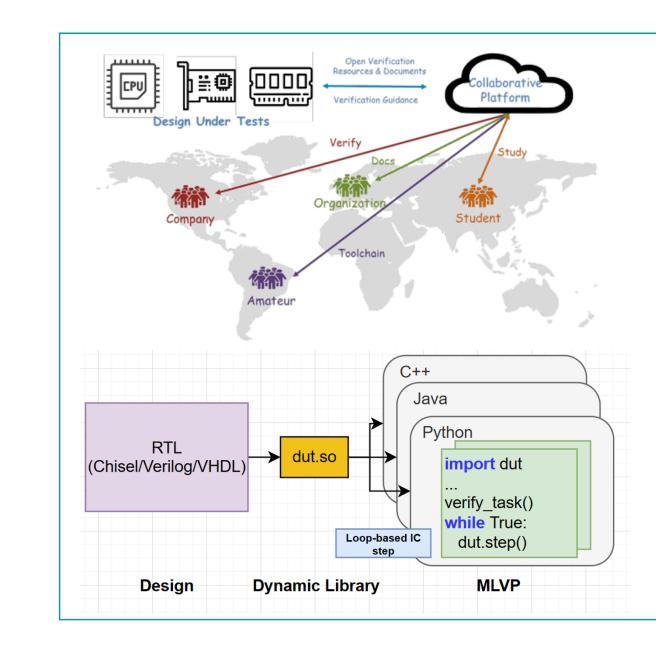

### **Challenge 2: Verification**

#### **Traditional verification:** $\cdot$ High expense: verification engineers >= design engineers Innovation · Language barrier: RTL expert • Non-uniformed infrastructure or platform

UnityChip verification: • Standard & free verification platform • Test cases using high-level languages (e.g. python) or RTL · Multi-language support

#### **Case Study**

We have used UnityChip to verify the branch predictor unit submodule in the front end of the Xiangshan Kunminghu processor. During the verification process, we divided the module into six subtasks: uFTB, Tage-SC, FTB, ITTAGE, RAS, and BPU Top.

2

D parted

han-BPU UT-Test Report We have collected verification data such as

## Xiangshan CPU Feature List

| Feature            | YQH         | NH                | КМН        |

|--------------------|-------------|-------------------|------------|

| Pipeline depth     | 12          | 12                | 12         |

| Rename width       | 4           | 4                 | б          |

| ROBsize            | 192         | 192               | 256+       |

| ALUs               | 4           | 4                 | 4          |

| L1 instr cache     | 16KB        | 64KB              | 64KB       |

| L1 data cache      | 32KB        | 64KB              | 64KB       |

| L2 cache           | 1024KB      | 256KB             | 1024KB     |

| L3 cache           | NA          | Upto4MB           | Upto16MB   |

| NoC support        | Ν           | Ν                 | WIP        |

| ITLB               | 32          | 32                | 48         |

| DTLB               | 32          | 128 direct mapped | 48         |

| L2 TLB             | 2048        | 2048              | 2048       |

| Vector             | Ν           | Y                 | Y          |

| Virtualization     | Ν           | Ν                 | Y          |

| ECCsupport         | Ν           | Y                 | Y          |

| PMA/PMP support    | Ν           | Y                 | Y          |

| Debug support      | Ν           | Y                 | Y          |

| External interface | AXI4        | AXI4              | AXI4/CHI   |

| ISA                | RV64GC      | RV64GCBKV         | RV64GCBKVH |

| Frequency@Process  | 1.3GHz@28nm | 2GHz@14nm         | 3GHz@7nm   |

| SPECint 2k6        | 7/ GHz      | 10/ GHz           | 15/ GHz    |

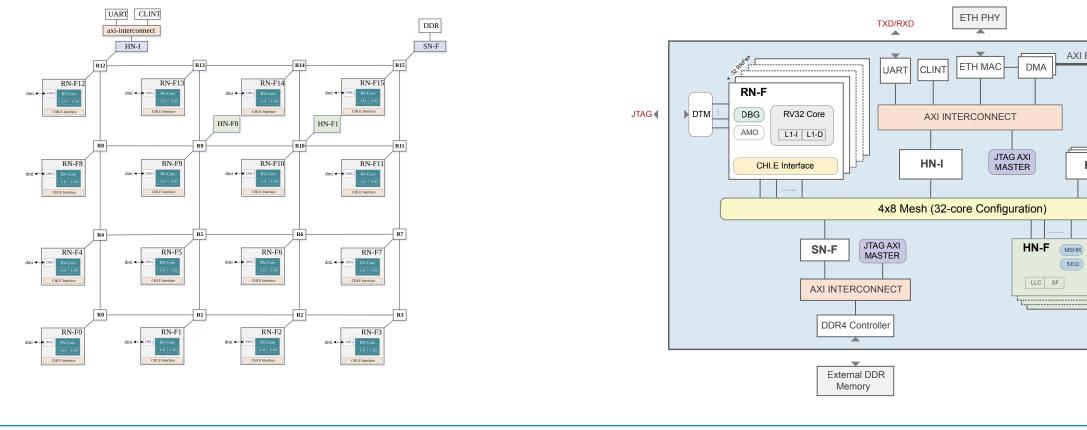

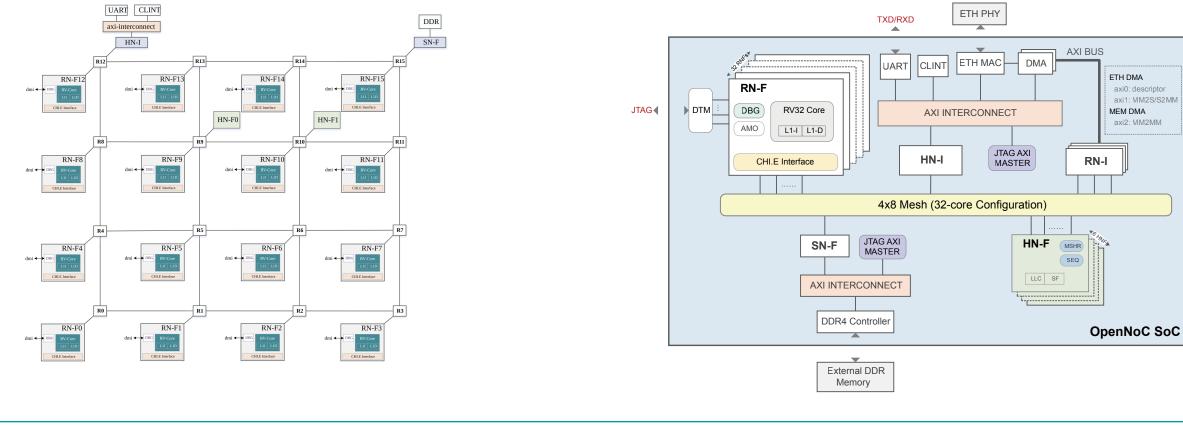

## **Open Network-on-Chip**

#### ·ARM AMBA 5 CHI 0050E.b

- •MESI based Cache coherency

- •Use Non-inclusive, Non-Exclusive policy

- •Support SF (Snoop Filter), maximum size 8MB

- •Support end-to-end QoS (Quality of Service) •Up to 8×8 Mesh

#### •Up to 128 RN-F nodes •Up to 16 NH-F nodes, with each HN-F's LLC size ranging from 0 t0 32MB •Up to 32 DDR channel ·256-bit data channel

| code coverage and                                                                         |                                                                                                                                                    |                      |                  |                      |                    |

|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------|----------------------|--------------------|

| functional coverage. We                                                                   | Line formation                                                                                                                                     | Functional Coverage  | _                |                      |                    |

| can also <b>map</b> this                                                                  | Line Coverage Functional Goverage<br>Coverage Res Her Lines Yost Lines Betail<br>Doldin, Life 1905 View (result)<br>Doldin, 1905 190 View (result) |                      |                  |                      |                    |

| coverage data to specific                                                                 | v ufTEraniesi range B                                                                                                                              |                      |                  |                      | 110-0 M(M)         |

| lines of code to selectively                                                              |                                                                                                                                                    |                      |                  |                      | Lance Market       |

|                                                                                           |                                                                                                                                                    |                      |                  |                      | 000041207          |

| improve them.                                                                             | ) Terret MALIN                                                                                                                                     |                      |                  | M14                  | PRIOR DO MILLER    |

| Five undergrads utilized a<br>pytest-based verification                                   |                                                                                                                                                    |                      |                  |                      |                    |

| environment which                                                                         | LCOV - code coverage report                                                                                                                        |                      |                  |                      |                    |

| identified some bugs and                                                                  | Current view: top level<br>Test: merged.info<br>Date: 2024-05-07 07:31:58                                                                          | Lines:<br>Functions: | Hit<br>1360<br>D | tutal<br>1541<br>0   | Coverage<br>88.3 % |

| achieved coverage results<br>comparable to those of<br>traditional verification<br>teams. | Directory Lin<br>minimum an affi<br>minimum<br>minimum<br>minimum                                                                                  |                      |                  | • 0/<br>• 0/<br>• 0/ | D                  |

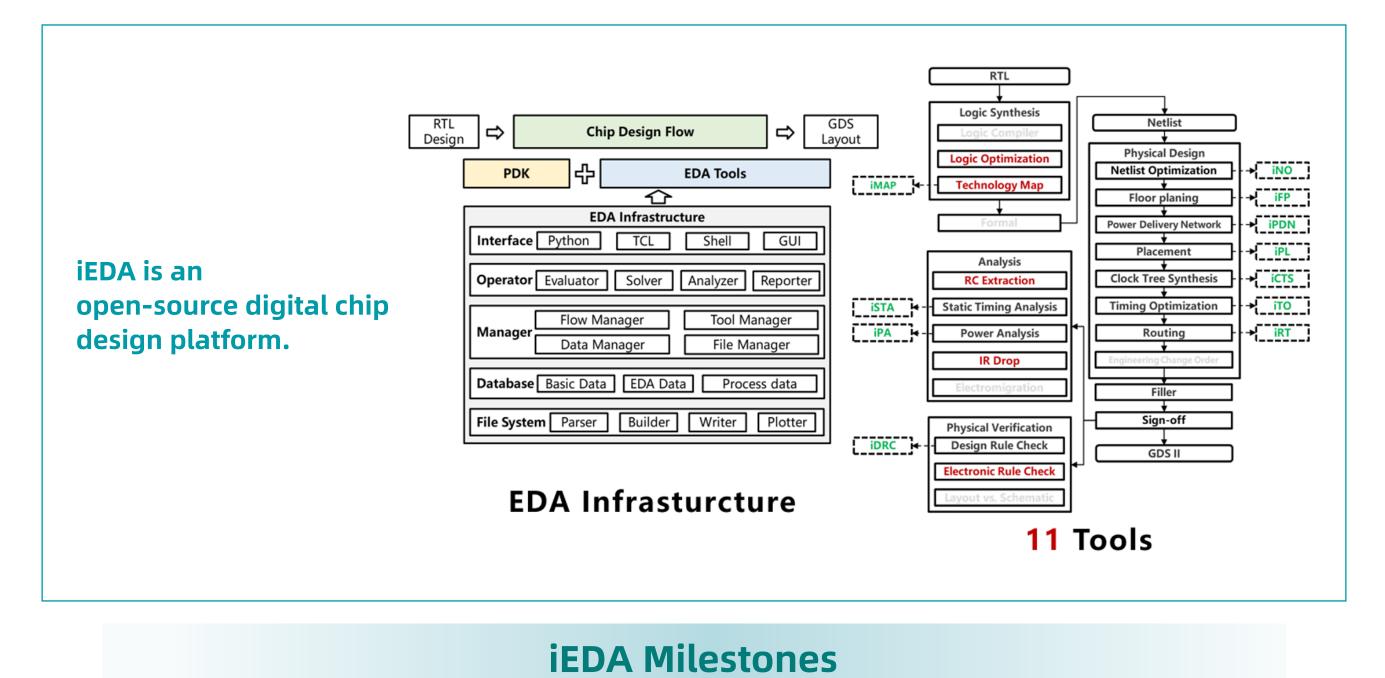

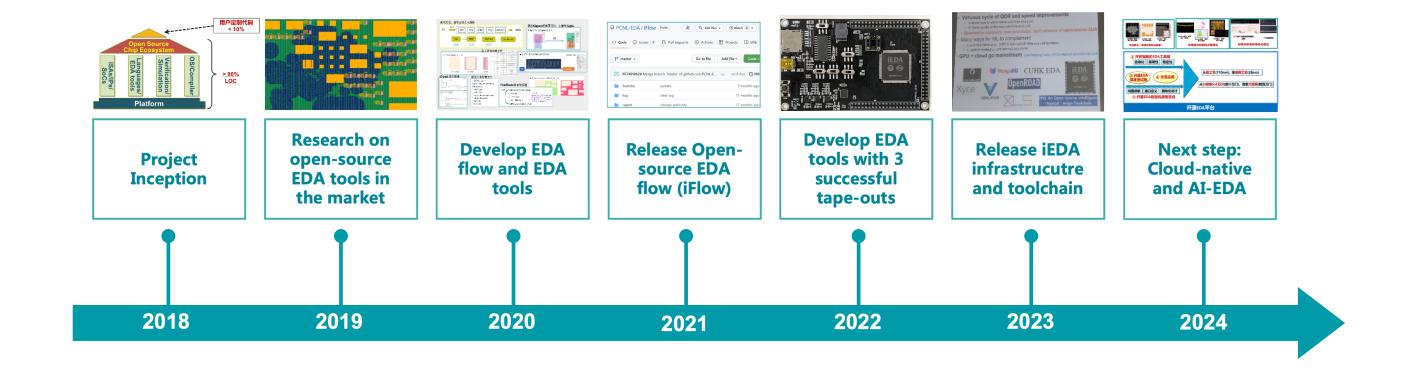

## **Challenge 3: Hardware Design EDA Tools**

# **For Your Information**

https://www.bosc.ac.cn https://open-verify.cc/en https://github.com/OpenXiangShan https://Xiangshan-doc.readthedocs.io

Xiangshan Wechat Official

iEDA Git Wechat Official

**UnityChip Verification**

Xiangshan Git Repo

iEDA Git Repo