# Atalanta: Open-Source RISC-V Microcontroller for Rust-Based Hard Real-Time Systems

Abdesattar Kalache Henri Lunnikivi Antti Nurmi

> Tampere University, Tampere, Finland RISC-V Summit Europe 2024

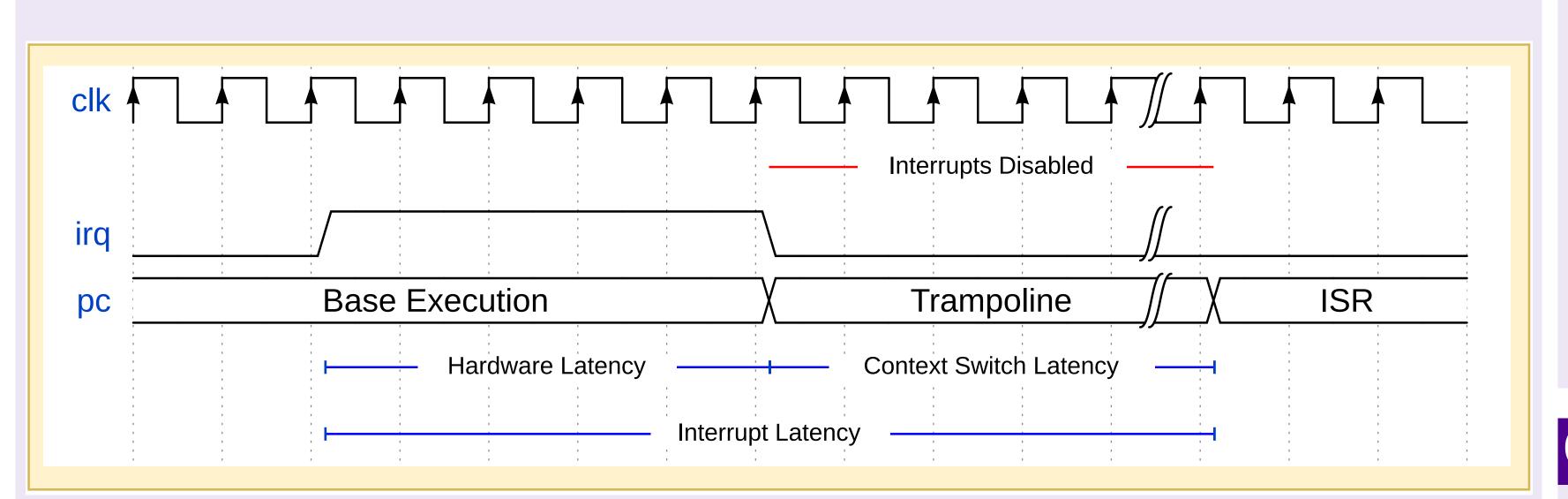

### Interrupt Latency

- The interrupt latency of a processor is a fundamental characteristic of real-time performance and is formed by two components:

- Hardware Latency Initial reaction latency of processor to interrupt request.

- Context Switch Latency Latency of storing/restoring processor state (register file, CSRs) from/to the stack.

## RTIC Framework

- The Real-Time Interrupt-Driven Concurrency Framework (RTIC) [1] is a task-based alternative to thread-based frameworks with formal guarantees for

- memory safety, absence of data races and defined behavior due to the Rust language and

- deadlock-free execution, single shared stack execution, single dispatch and bounded priority inversion due to the framework itself.

- Tasks are implemented as interrupt handlers, thus task switching is as efficient as the interrupt handling mechanism of the hardware without any additional overhead.

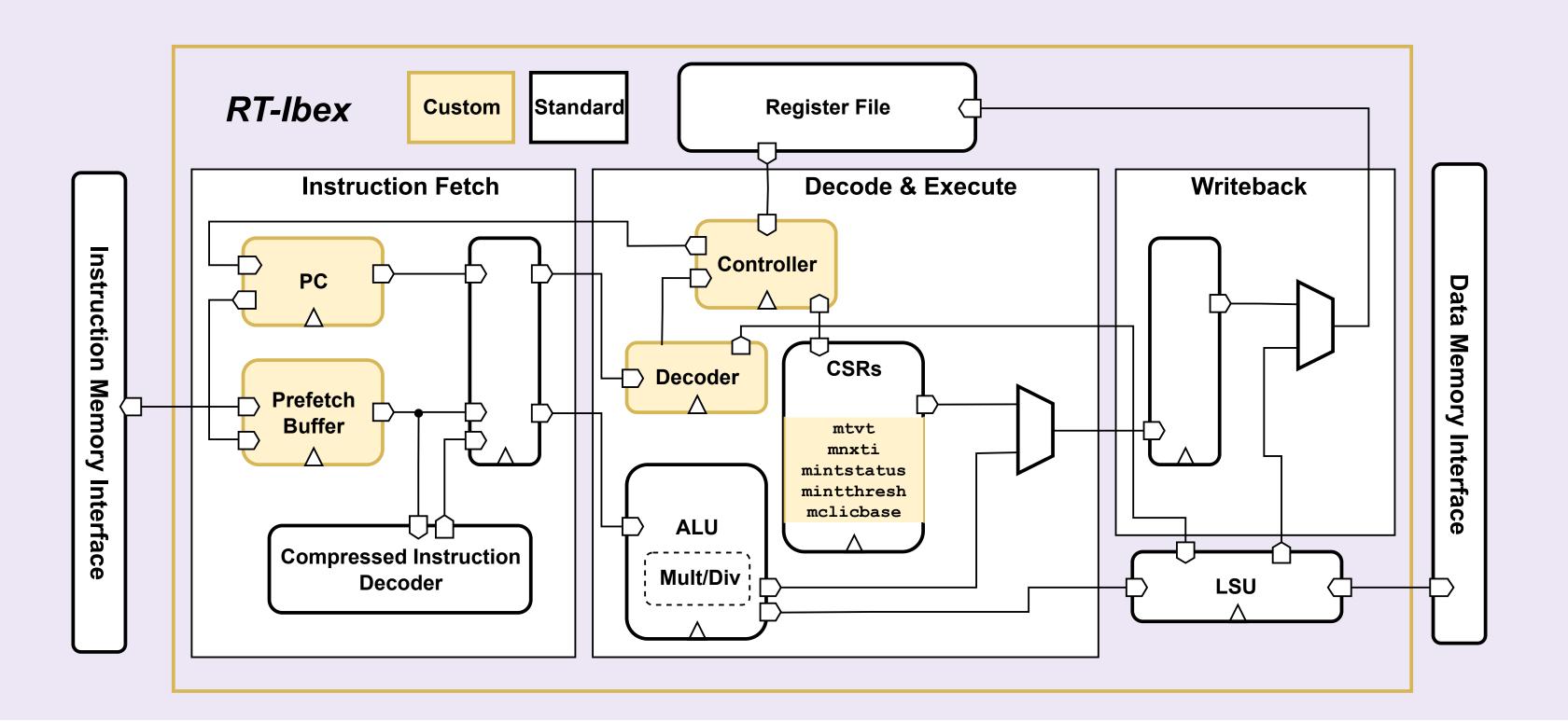

#### RT-Ibex

The open-source lbex processor was extended with a configurable Future Work interrupt interface and interrupt-level-based preemption to create the core-local interrupt controller (CLIC)-compliant RT-lbex.

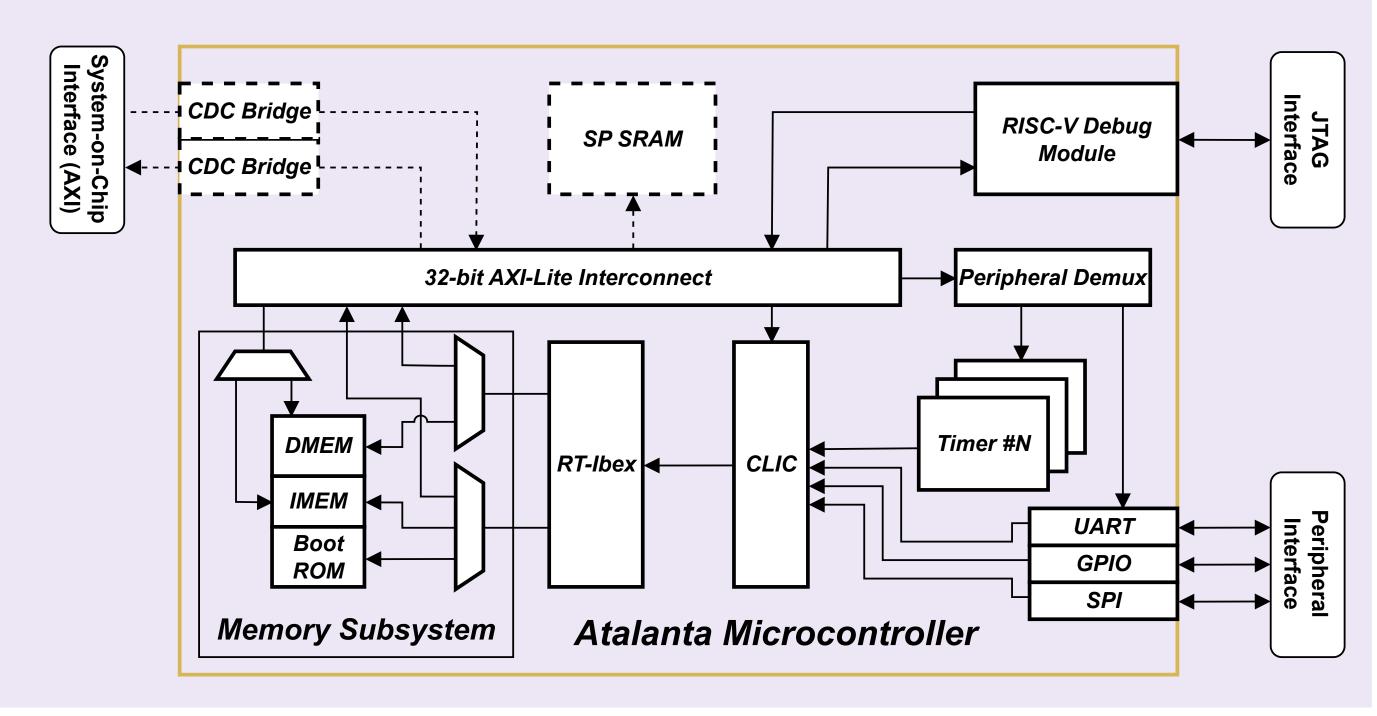

### Microcontroller Architecture

A minimal, extendable architecture designed for low-latency memory access to accelerate context switching.

# Comparison with State-of-the-Art

| This Work               | RISC-V | CLIC                    | Software<br>Stacking           | EABI  | 12                   | 5              | 16  | 21                   |

|-------------------------|--------|-------------------------|--------------------------------|-------|----------------------|----------------|-----|----------------------|

| Balas et al.[3]         | RISC-V | CLIC                    | HW Stacking + Register Banking | EABI  | 12                   | 6 <sup>a</sup> | 18  | 6 <sup>b</sup>       |

| Balas et al.[2]         | RISC-V | CLINT                   | Software<br>Stacking           | EABI  | 12                   | 6 <sup>a</sup> | 18  | 24                   |

| SiFive E21              | RISC-V | CLIC                    | Software<br>Stacking           | n.a   | n.a                  | n.a            | n.a | 20                   |

| Cortex <sup>®</sup> -R5 | ARM    | VIC/GIC                 | Register<br>Banking            | AAPCS | 9                    | n.a            | n.a | 20                   |

| Cortex®-M3/4            | ARM    | NVIC                    | Hardware<br>Stacking           | AAPCS | 9                    | 6              | 9   | 12                   |

| Cortex®-M0+             | ARM    | NVIC                    | Hardware<br>Stacking           | AAPCS | 9                    | 6              | n.a | 15                   |

| Cortex <sup>®</sup> -M0 | ARM    | NVIC                    | Hardware<br>Stacking           | AAPCS | 9                    | 6              | n.a | 16                   |

| Microcontroller         | ISA    | Interrupt<br>Controller | Interrupt<br>Context-Save      | ABI   | instruction<br>Count | Ta             | Ts  | Interrupt<br>Latency |

| Microcontroller         | ICA    | Interrupt               | Interrupt                      | ΛDI   | instruction          |                |     | T                    |

<sup>a</sup> Susceptible to jitter from multi-cycle instructions prior to vector table entry fetch.

- Architectural Optimizations clock domain split, improved hierarchy, hardware stacking.

- Case Studies Analysis of real-time performance with formal and empirical methods.

- ASIC Implementation PPA analysis with 22 nm technology node, memory models.

- [1] RTIC Contributors. RTIC: The Hardware-Accelerated Rust RTOS. https://rtic.rs/2/ book/en/. 2024.

- [2] R. Balas and L. Benini. "RISC-V for Real-time MCUs Software Optimization and Microarchitectural Gap Analysis". In: 2021 Design, Automation & Test in Europe Conference & Exhibition (DATE). 2021, pp. 874–877.

- [3] R. Balas, A. Ottaviano, and L. Benini. "CV32RT: Enabling Fast Interrupt and Context Switching for RISC-V Microcontrollers". In: IEEE Transactions on Very Large Scale Integration (VLSI) Systems (2024), pp. 1–13.

<sup>&</sup>lt;sup>b</sup> Interrupt latency can increase in the case of nested interrupts.