# Utilizing RISC-V Trace Standards for Efficient Bugfixing and Profiling

# Challenges Embedded Developers are Facing Today

- Driven by market requirements, embedded systems and chip architectures are becoming more complex:

- ➤ More powerful processors of different architectures like RISC-V in different multicore configurations (SMP, AMP).

- > → Different operating systems such as Linux as a "rich operating system", RTOS or an AUTOSAR variant in the automotive industry.

- Heterogeneous multicore architectures increase the requirements for bug fixing and thus for both pure debuggers and real-time trace.

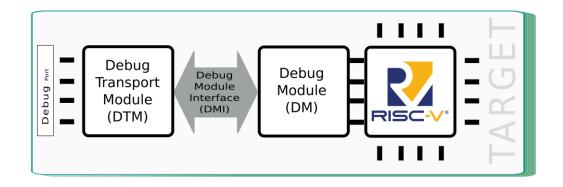

# RISC-V Debugging Made Easy

"RISC-V External Debug Support" Specification v1.0.0 incorporates everything needed for simple and complex debugging scenarios

- Great solution for simple and fairly complex RISC-V Systems

- > Open to adaptions to support most complex and diverse SoCs

- > Flexible DTM designs make heterogeneous debugging easy

- > Several options to add peripheral IP such as Trace

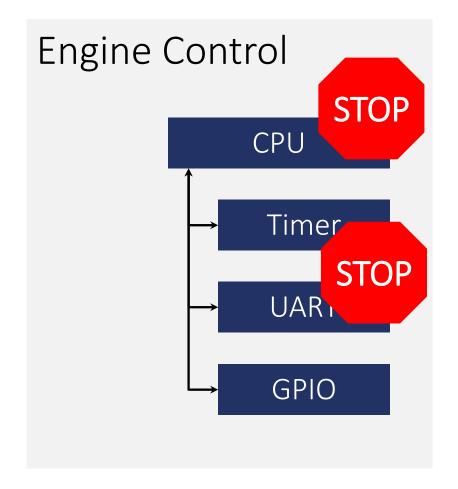

## From Debug to Trace

- We can freeze the core

- > We might freeze also some peripherals

- But we can not freeze the surrounding

How can we still find bugs?

# Trace Supplements Debugging

- Trace based debugging

- Debug without stopping the CPU

- > Find bugs which appear only in real time

- Optimizing with timing measurements

- > Analyse the code performance of the application

- > Analyse outside events

- > Prove the meeting of real time requirements

- Prove code coverage

### RISC-V Trace Solutions

- Specifications for two RISC-V Trace Standards have been ratified recently

- > RISC-V E-Trace Standard

- RISC-V N-Trace Standard

- > Standards consist of different documents

|                   | RISC-V<br>N-Trace<br>Specification | RISC-V<br>E-Trace<br>Specification | RISC-V Unformatted Trace Packet Encapsulation Specification | RISC-V Trace Control Interface Specification | RISC-V<br>Trace<br>Connectors<br>Specification |

|-------------------|------------------------------------|------------------------------------|-------------------------------------------------------------|----------------------------------------------|------------------------------------------------|

| RISC-V<br>N-Trace | •                                  |                                    |                                                             | •                                            | •                                              |

| RISC-V<br>E-Trace |                                    | •                                  | •                                                           | •                                            | •                                              |

### RISC-V Trace Solutions

- > RISC-V trace specifications are also suitable for heterogeneous systems

- Flexible ways to access the trace component's configuration registers via System Bus Access, DMI, message passing networks, ...

- > Filters to limit trace usage

- Transportability via other trace infrastructure such as CoreSight ATB

- Lauterbach supports the latest versions of the E- and N-Trace specifications in various implementations

We will discuss this later in more detail

# Compare RISC-V Trace Specifications

- Currently no assessment as to which is better

- Different optimization mechanisms and protocol characteristics

- Efficiency depends how good chip, application and trace protocol work together

| N-Trace                                           | E-Trace                         |  |

|---------------------------------------------------|---------------------------------|--|

| Instruction Trace                                 | Instruction + Data Trace        |  |

| Inferable Jump<br>Optimization                    | Inferable Jump<br>Optimization  |  |

| Implicit Return Optimization (in different modes) | Implicit Return Optimization    |  |

| Repeated History<br>Optimization                  | Address Optimization            |  |

| Virtual Address<br>Optimization                   | Implicit Exception Optimization |  |

|                                                   | Branch Prediction Optimization  |  |

|                                                   | Jump Target Cache Optimization  |  |

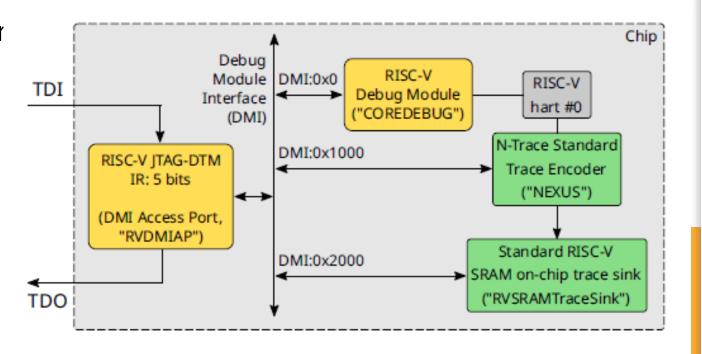

# Case Study: Simple RISC-V Trace

> Small embedded RISC-V controller

Simple and easy to use trace infrastructure

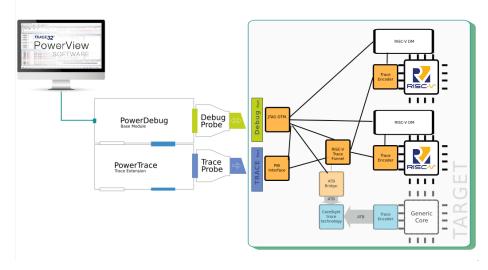

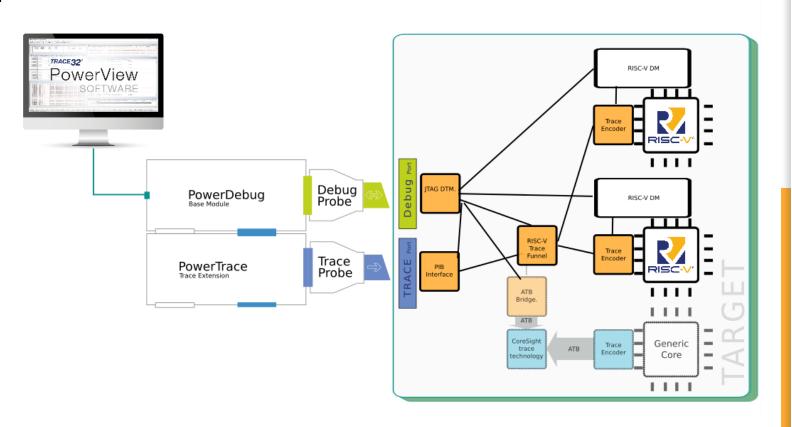

# Case Study: Heterogeneous RISC-V Trace

More complex system with RISC-V and other cores

Fits to all possible tracing requirements

# Last but not Least: Lauterbach is <u>Always</u> at the Forefront of RISC-V Technology

**Lauterbach Supports Infineon's Automotive RISC-V Virtual Prototype**

Publishing Date: March 7, 2025

os - as the main CPU(s) or as a ctures. As the leading tool supplier g on the newest and most exciting ions of todays and future chips

latforms running L4Re

s A25 cores with the recently

Learn more about our RISC-V support and visit us at our booth.

nd

# Summary

Trace

N-T

> Chips are getting more and more complex and implement a growing number of RISC-V cores in different (heterogeneous) multicore configurations (SMP, AMP).

> "RIS nee For more details download our Whitepaper

"Debugging of RISC-V-Based Chips Made Easy ":

beg https://www2.lauterbach.com/download/pdf/white-paper/whitepaper-beg debugging-risc-v-based-chips-made-easy.pdf

Lauterbach's modular in Note 32 system covers <u>an acous and trace requirements</u> for any RISC-V-based chip today — find your solution easily here: https://www.lauterbach.com/supported-platforms/architectures/risc-v

Your **KEY** to Embedded Innovations since 45 Years

Utilizing RISC-V Trace

Standards for Efficient

Bugfixing and Profiling

Nicolas.Delemarre@Lauterbach.com

QUESTIONS?