# REPTILES: Repeated Tiles of Sargantana, a RISC-V multicore based on OpenPiton

Noelia Oliete-Escuín<sup>1</sup>, Arnau Bigas-Soldevila<sup>1</sup>, Narcís Rodas<sup>1</sup>, Albert Aguilera<sup>1</sup>, Sajjad Ahmad<sup>1</sup>, Jonathan Balkind<sup>2</sup>, Xavier Carril<sup>1</sup>, Max Doblas<sup>1</sup>, Ivan Díaz<sup>1</sup>, Roger Figueras<sup>1</sup>, Alireza Foroodnia<sup>1</sup>, Cesar Fuget<sup>3</sup>, Ignacio Genovese<sup>1</sup>, Raúl Gilabert<sup>1</sup>, Abbas Haghi<sup>1</sup>, Alexander Kropotov<sup>1</sup>, Neiel Leyva<sup>1</sup>, Oscar Lostes-Cazorla<sup>1</sup>, Lorién López-Villellas<sup>4</sup>, Davy Million<sup>5</sup>, Alireza Monemi<sup>1</sup>, Sérik Pérez<sup>1</sup>, Juan Antonio Rodríguez<sup>1</sup>, Víctor Soria-Pardos<sup>1</sup>, Behzad Salami<sup>1</sup>, Francesc Moll<sup>1</sup>, Oscar Palomar<sup>1</sup>, Miquel Moretó<sup>1</sup> and Lluc Alvarez<sup>1</sup>

<sup>1</sup>Barcelona Supercomputing Center (BSC), Barcelona <sup>2</sup>University of California, Santa Barbara <sup>3</sup>University Grenoble Alpes, Inria <sup>4</sup>University Zaragoza <sup>5</sup>University Grenoble Alpes, CEA

### Abstract

**Chip industry** continues advancing and expanding modern computing systems, resulting in **more complex multi-core processors**. Conversely, **academic projects** face scalability challenges due to **limited resources and infrastructure**. The **community needs open-source frameworks** that enable innovation and knowledge sharing.

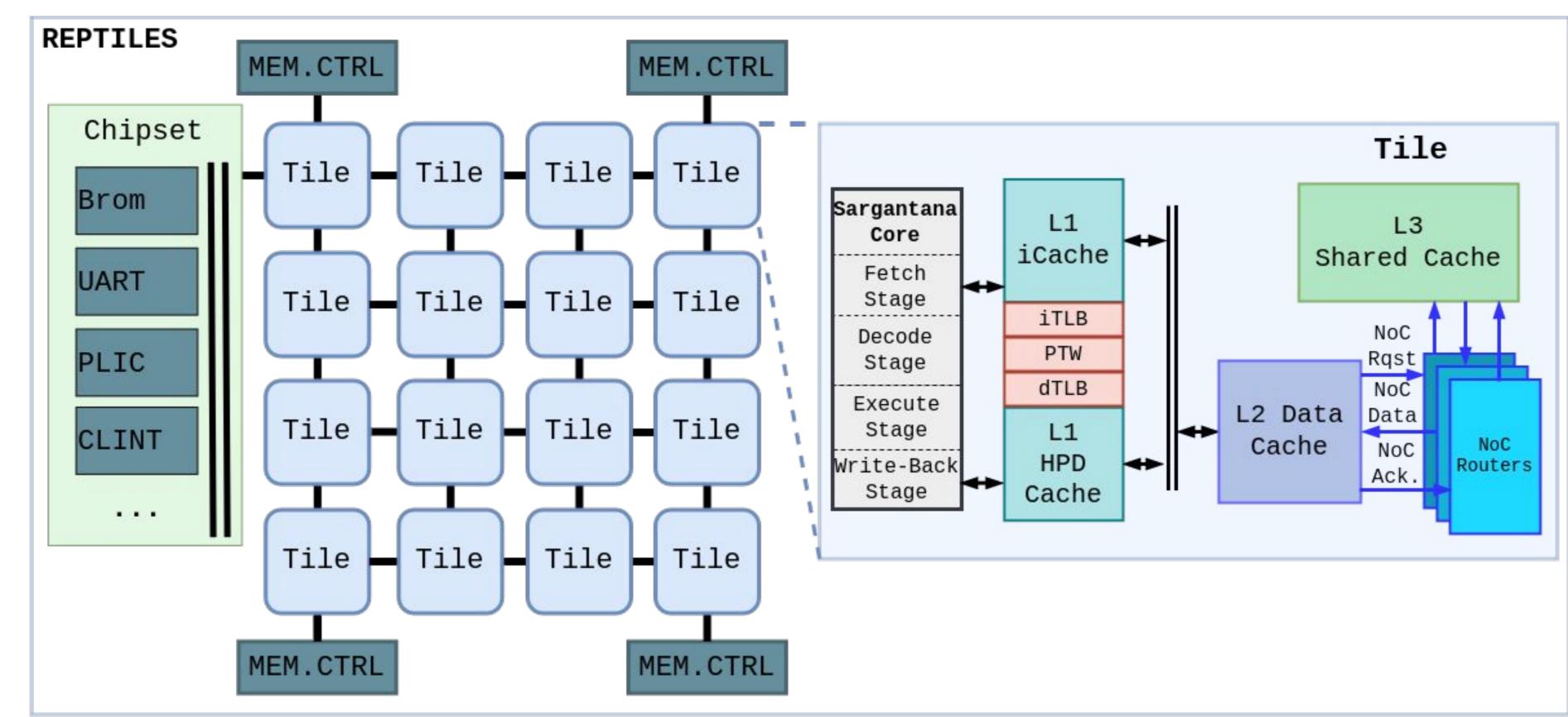

This work presents **REPTILES**, **REP**eated **TILE**s of Sargantana, an **open-source RISC-V multicore framework** based on Sargantana and OpenPiton. We aim to provide an accessible HPC framework where researchers can develop, experiment with, and optimize HPC applications. Additionally,

we show the new features incorporated in OpenPiton and Sargantana designs to improve the performance of HPC applications. Finally, we demonstrate that REPTILES present a suitable scalability achieving a speedup of 3.1× on average with 4 cores.

## Contributions

**REPTILES** is based on the open-source designs: **OpenPiton and Sargantana**

## OpenPiton

Center

Vacional de Supercomputación

BARCELONATECH

Sargantana is a Linux-capable 64-bit RISC-V processor that implements the RV64GV ISA.

## **OpenPiton Improvements**

- Parametric NoC width: 64, 128, 256, 512 and 704 bits.

- Parametric cache block sizes: 16, 32, and 64 bytes.

- Parametric number of MSHRs in all cache levels: from 2 up to 64.

- Parametric cache sizes and associativities.

- Support for parallel SRAM access in the L2 and L3 caches.

- Enhanced design with the connection of Sargantana to the High-Performance Data Cache (HPDCache).

### Sargantana Improvements

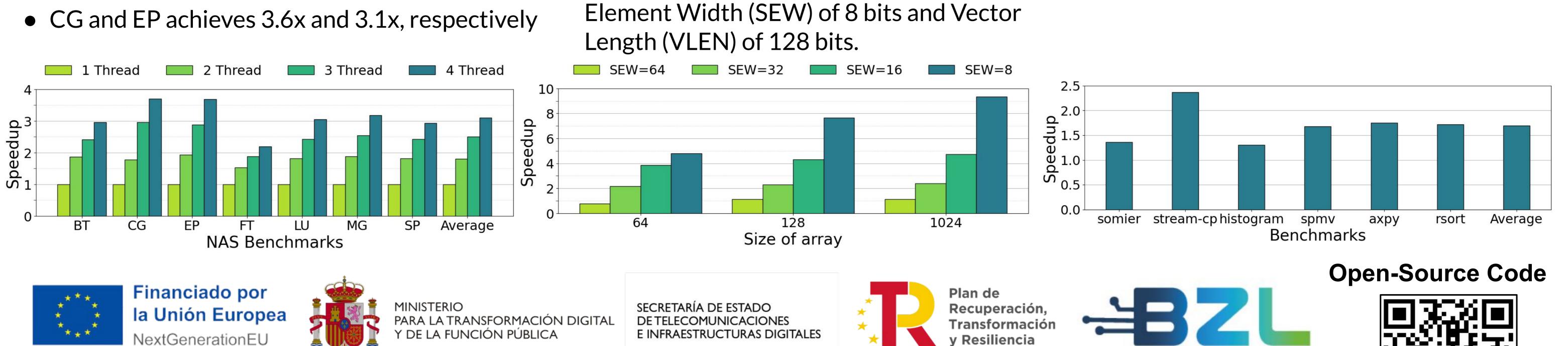

- Upgraded RISC-V Vector Extension (RVV) from version 0.7 to 1.0, configurable from 128 to 512 bits (in this poster, 128).

- Added support for most of the RVV specifications, except for the LMUL>1 setting and vector FP instructions.

- Added RISC-V extensions Sdext (for debugging support) and Sscofpmf (to enable reading core performance counters in Linux via perf).

### Results

- Increasing number of threads demonstrates suitable scalability, 3.1x on average.

- The vectorization of a matrix addition shows

The OpenPiton HPC improvements provide up to 9.3x speedup when using a Standard

1.7x speedup on selected benchmarks.

This project with reference REGAGE22e00058408992 is promoted by the Ministry for Digital Transformation and Public Service, within the framework of the Recovery, Transformation and Resilience Plan - Funded by the European Union - NextGenerationEU and partially funded by Spanish MCIU/AEI project PID2023-146511NB-I00 co-funded by EU ERDF and by Generalitat de Catalunya [2021-SGR-00763].