# Towards an Industrial-Grade Open-Source Floating-Point Unit for RISC-V Vector Processors

Enis Mustafa, Michael Platzer, Domenic Wüthrich and Florian Zaruba

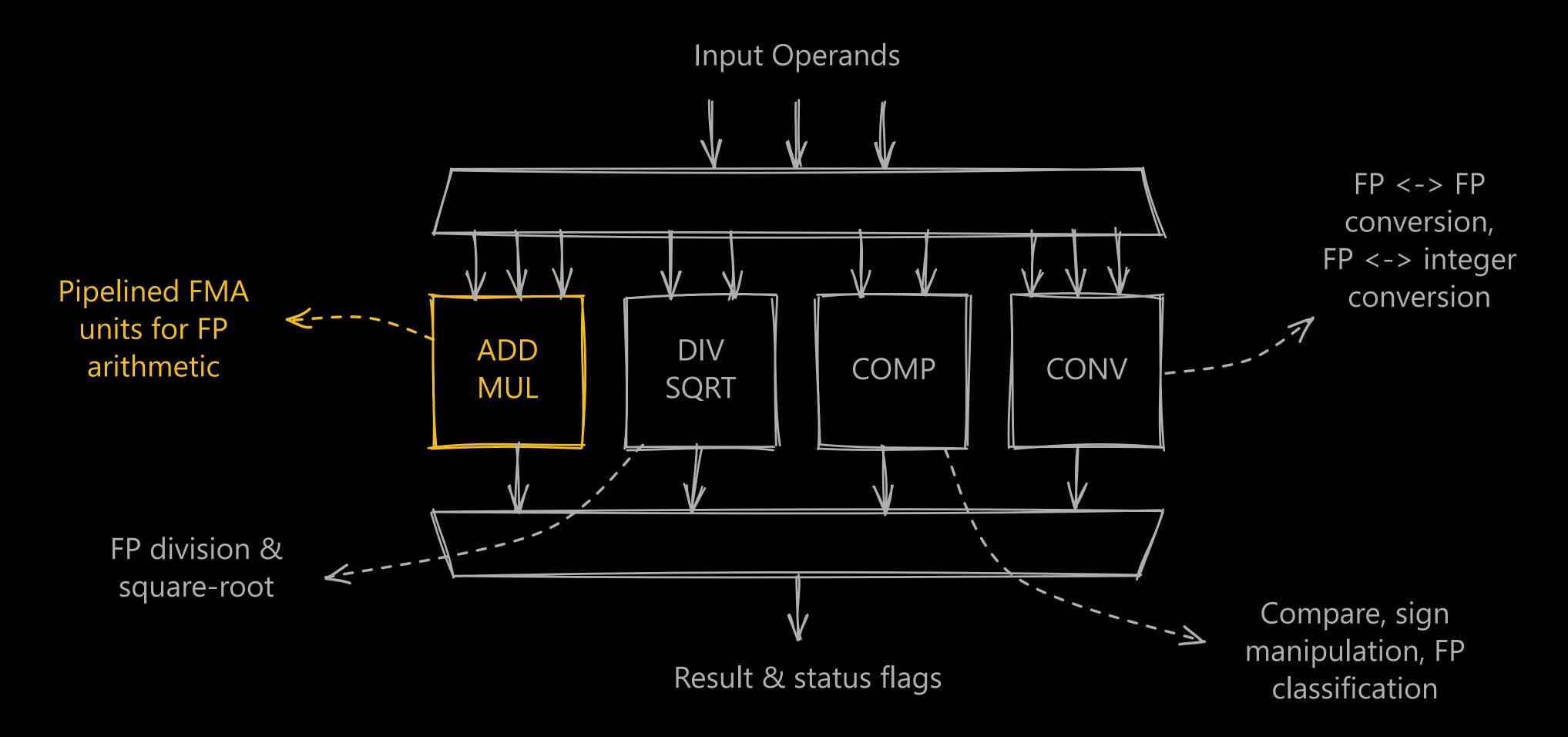

## OpenHW Group CVFPU<sup>†</sup>

Parametric floating-point unit with support for standard RISC-V formats and operations as well as transprecision formats Formerly known as FPnew, developed at ETH Zürich [1]

## Contributions for Improved Vector Support

• Symmetric Widening Add

Added *symmetric* widening add (same width operands) in addition to *asymmetric* add (one narrow, one wide operand) for V extension support

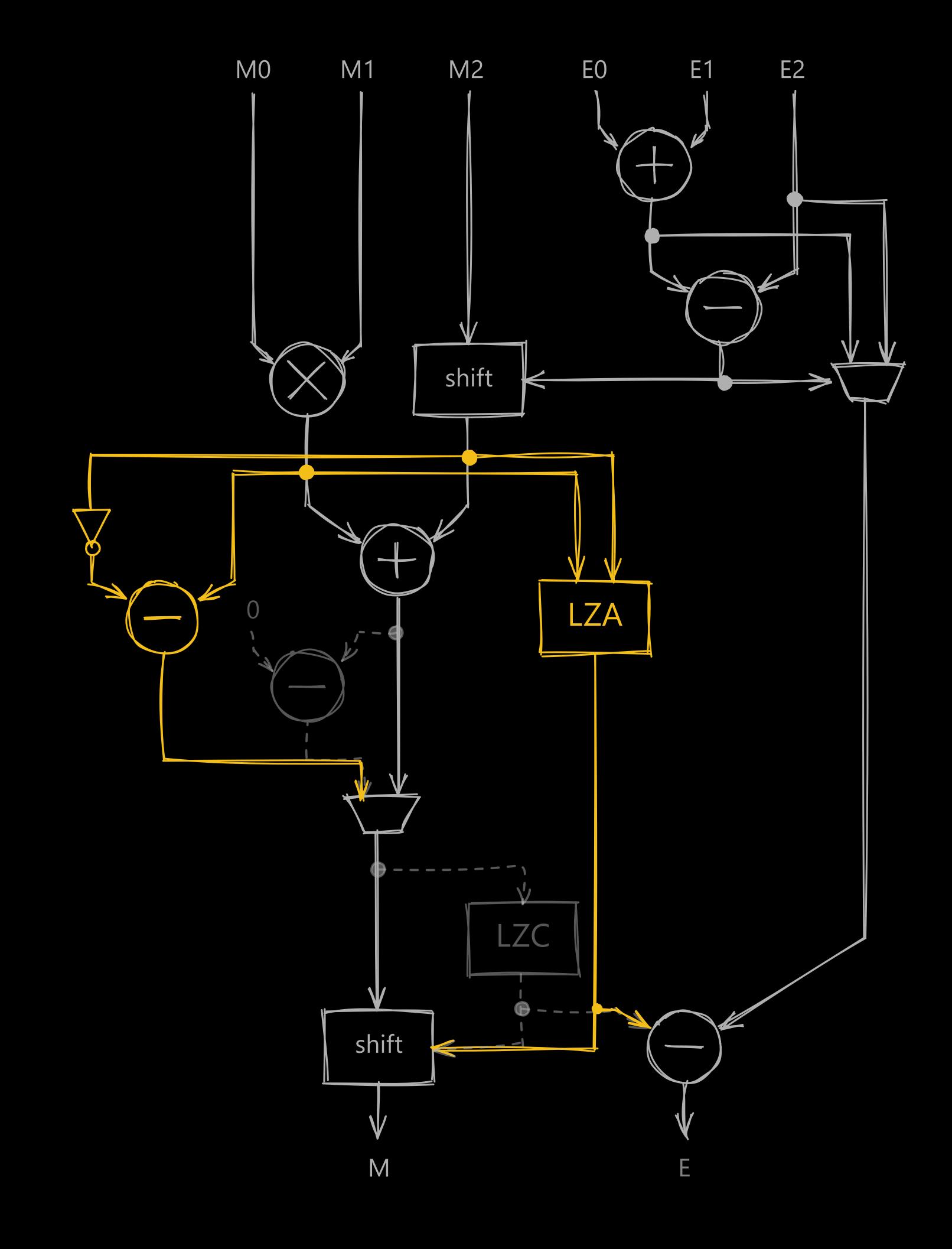

FMA Datapath Improvements

Parallel positive & negative sums to avoid two sequential adder carry chains

Leading Zero Anticipator (LZA) to calculate shift amount in parallel with sums

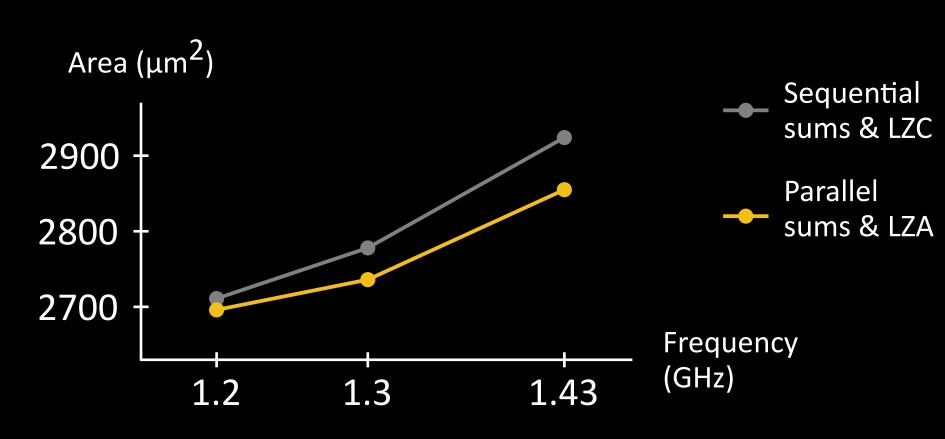

### Area vs Timing Improvement w/o Retiming

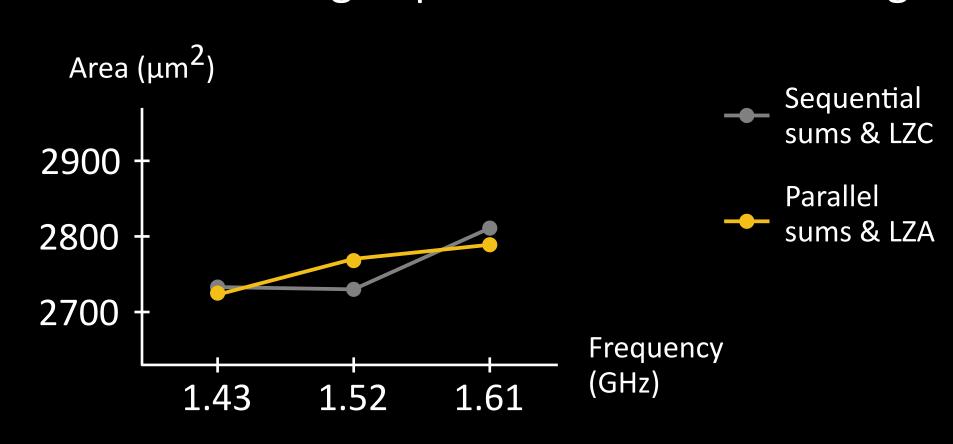

### Area vs Timing Improvement with Retiming

Extend RISC-V DV with V extension

Random instruction generator RISC-V DV (maintained by CHIPS Alliance) extended with V extension support