# Enhancing your RISC-V SoC debug & optimization with embedded functional monitors

Mat O'Donnell, Software Architect Lead Tessent Embedded Analytics, Siemens EDA

## Agenda

Functional Monitoring – what and why?

Mitigating issues for high bandwidth

Actionable insights – Customer Use Cases

Continuous in life monitoring

Summary

## Functional monitoring – why?

The effort required to validate, debug, and optimize SoCs continues to escalate

Need better ways to observe if SoCs behave and perform as intended

Reduces SoC debug effort prior to launch

Simplifies system performance optimization before and after launch

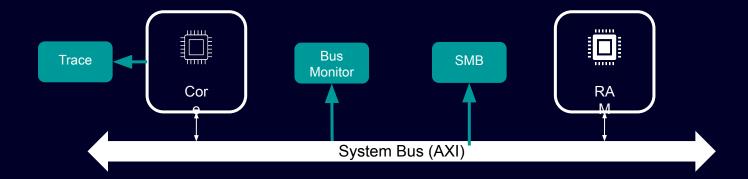

## Functional monitoring – what?

Observing non-intrusively if your SoC behaves as it was designed

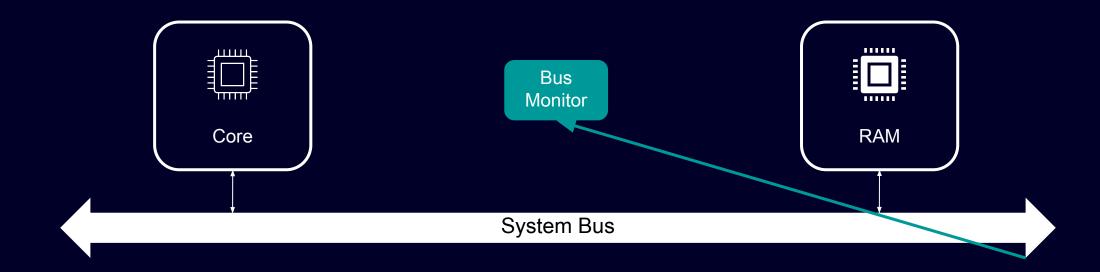

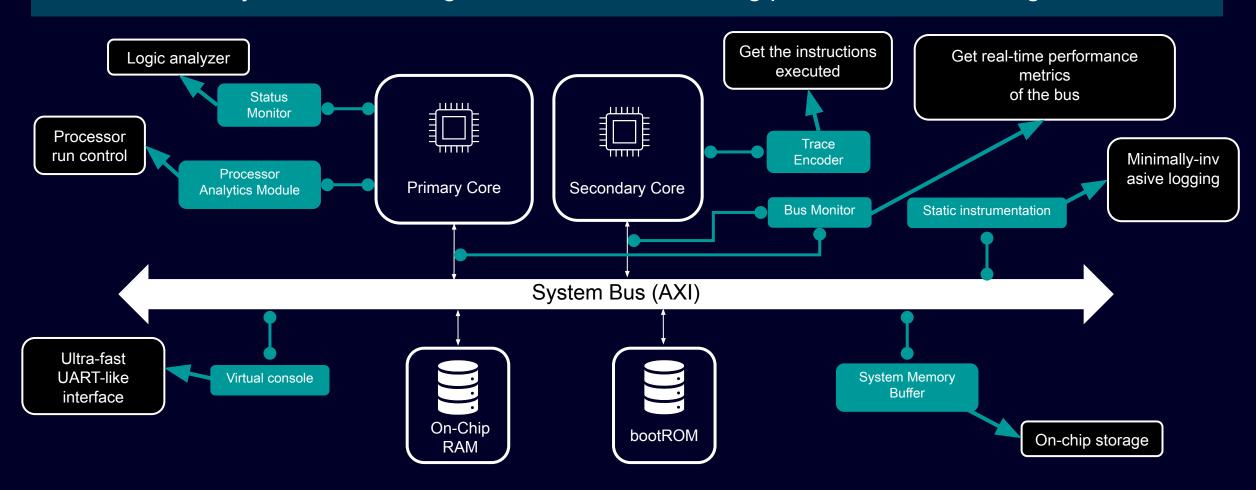

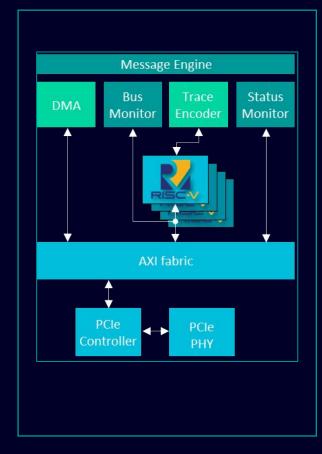

## System-wide functional monitoring

Full system-level debug and functional monitoring provide additional insights

- Smart Filtering

- Smart Logging

- Counters

- Cross-triggering

```

# configure filter for writes between two addresses

filter = hsdk.BusMonitor.Interface.Filter()

filter.address(0x60000000, 0x60054600, "inclusive")

filter.types("write")

```

- Smart Filtering

- Smart Logging

- Counters

- Cross-triggering

```

# configure filter

filter = hsdk.BusMonitor.Interface.Filter()

filter.types("write")

# trace any transactions that match the filter

trace = interface.trace(filter, "write_address")

```

- Smart Filtering

- Smart Logging

- Counters

- Cross-triggering

```

# configure filter

filter = hsdk.BusMonitor.Interface.Filter()

filter.address(0x60000000, 0x61000000, "inclusive")

# count the number of busy cycles

count = interface.count("busy_cycles", "count", filter)

```

- Smart Filtering

- Smart Logging

- Counters

- Cross-triggering

```

# configure filter

filter = hsdk.BusMonitor.Interface.Filter()

filter.address(0x600000000, 0x600000004, "inclusive")

filter.type("write")

# fire an event when the filter matches

event = hsdk.BusMonitor.Event()

bus_monitor.event(filter, event)

# configure SMB as a circular buffer

smb = hsdk.SMB("to")

smb.output_on(event)

```

## Monitoring for performance improvements

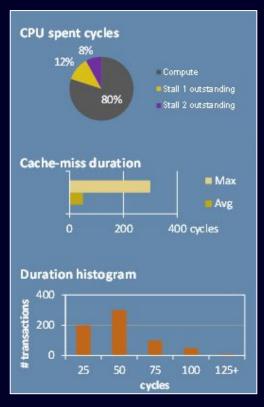

## CPU performance loss

Identified excessive max cache miss duration, which impacted overall performance

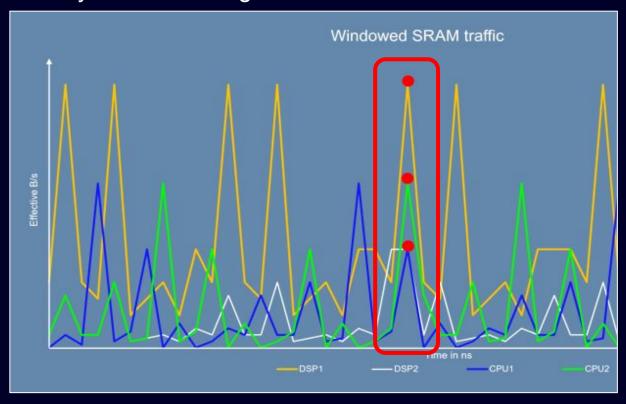

## Memory bandwidth degradation

All cores try to access memory with high bandwidth simultaneously

Details: How Picocom optimizes 5G SoCs and networks with Tessent

## Functional monitoring for actionable insights

```

soc_noc_rt0=>{0x3E02_0000 to 0x3E02_8000 }

Address: 0x00000428 Name: region55_subregion1_cnr_if_snoc_uaxia_m_ia_agent_status => req is outstanding, value: 0x10

Address: 0x00000828

Name: region55_subregion2_cnr_if_snoc_uaxia_s_ta_agent_status => NO outstanding req, value:0x0

Name: region55_subregion3_cnr_if_snoc_uaxib_m_ia_agent_status => NO outstanding req, value:0x0

Address: 0x00000c28

Address: 0x00001028

Name: region55 subregion4 cnr if snoc uaxib s ta agent status=> NO outstanding req, value:0x0

Address: 0x00001428

Name: region55_subregion5_cxram_csr_ta_agent_status => NO outstanding req, value:0x0

Address: 0x00001828

Name: region55_subregion6_lxb_snoc_daxi_s_ta_agent_status => NO outstanding req, value:0x0

Address: 0x00001c28

Name: region55_subregion7_lxb_snoc_daxia_m_ia_agent_status => NO outstanding req, value:0x0

Address: 0x00002028

Name: region55 subregion8 lxb snoc daxib m ia agent status=> NO outstanding req, value:0x0

Address: 0x00002428

Name: region55 subregion9 rt1 access ta agent status => NO outstanding req, value:0x0

Address: 0x00002828

Name: region55 subregion10 soc cip pcie data ia agent status, req is outstanding, value: 0x50

Address: 0x00002c28

Name: region55 subregion11 soc cip sys cfg s ta agent status, resp is active, value: 0x20

Address: 0x00003028

Name: region55 subregion12 soc cip sys data ia agent status, => NO outstanding req, value:0x0

Address: 0x00003428

Name: region55_subregion13_soc_cxram0_ta_agent_status => NO outstanding req, value:0x0

Address: 0x00003828

Name: region55_subregion14_soc_cxram1_ta_agent_status => NO outstanding req, value:0x0

Address: 0x00003c28

Name: region55 subregion15 soc cxram2 ta agent status => NO outstanding req, value:0x0

Address: 0x00004028

Name: region55_subregion16_soc_cxram3_ta_agent_status => NO outstanding req, value:0x0

Address: 0x00004428

Name: region55_subregion17_soc_dbg_smb_m_ia_agent_status_=> NO outstanding req, value:0x0

Address: 0x00005428

Name: region55_subregion21_soc_dbg_smb_s_ta_agent_status => NO outstanding req, value:0x0

Address: 0x00005828

Name: region55_subregion22_soc_dbg_trace_sram_ta_agent_status => NO outstanding req, value:0x0

Address: 0x00005c28

Name: region55 subregion23 soc if csr ta agent status => NO outstanding req, value:0x0

soc_noc_rt1=>{0x3E02_8000 to 0x3E02_C000 }

Address: 0x00000028

Name: region8 subregion0 lxb snoc daxi s ia agent status

Address: 0x00000428

Name: region8 subregion1 lxb snoc daxia s ta agent status

Address: 0x00000828

Name: region8 subregion2 lxb snoc daxib s ta agent status

Address: 0x00001028

Name: region8_subregion4_rt1_access_ia_agent_status, req is outstanding, value: 0x10

```

## Functional monitoring for actionable insights

0:0 2455293,xbm5,177493478730,Y,axi monitor port 0,flag:state\_change,channel:read\_addr(direct),enabled:0,history\_mode:stream

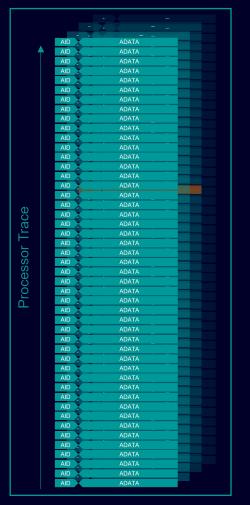

## Functional monitoring for actionable insights

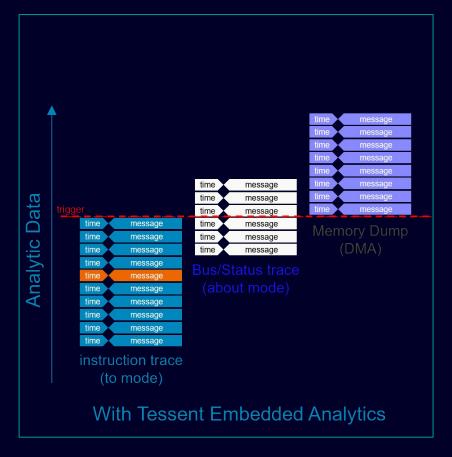

Traditional methods produce very large amount of trace data

SoC instrumented with Embedded Analytics IP Capture relevant data around trigger condition Debug trace before, during and after failure

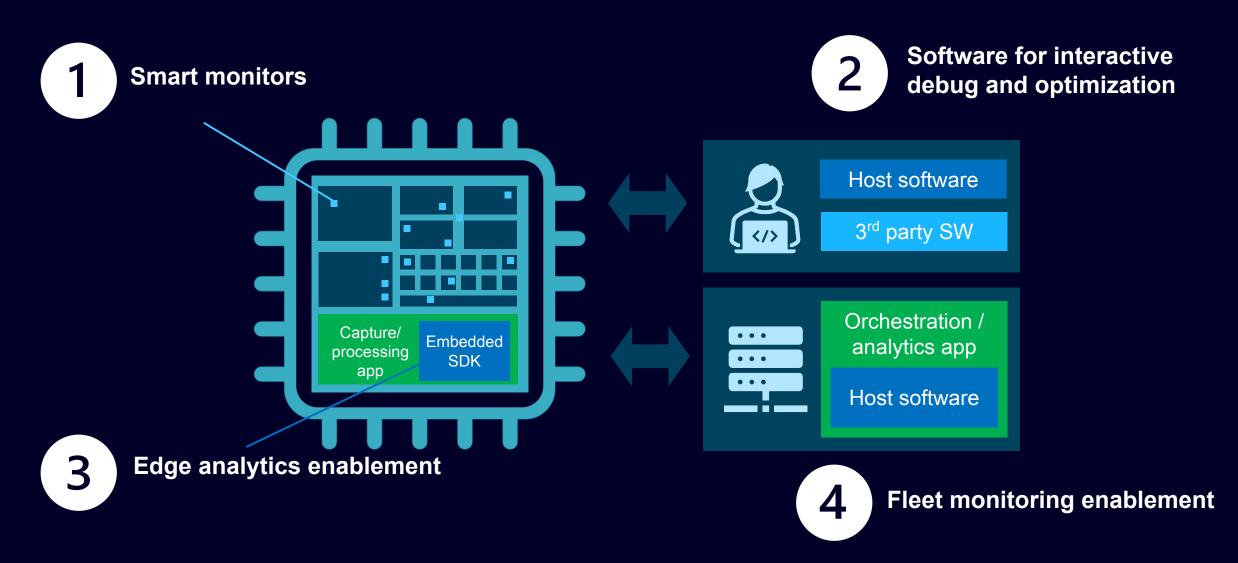

## **Building a Scalable SLM Solution**

# Summary

Functional monitoring reduces debug time

Added visibility simplifies performance optimization

Smart functional monitoring helps save bandwidth

End-to-end, from bring-up to in-life

## Join us at RISC-V Europe Summit 2025

#### **Presentation**

Efficient debug and trace of RISC-V systems: a hardware/software co-design approach

Thursday May 15, 10:00 in Gaston Berger (S2)

Poster session available at Thursday May 15, Island 1.1 (S1)

#### **Presentation**

Unleashing the Power of RISC-V E-Trace with a Highly Efficient Software Decoder

Thursday May 15, 11:45 in Gaston Berger (S2)

Poster session available at Thursday May 15, Island 2.2 (S2)

#### **Demo presentation**

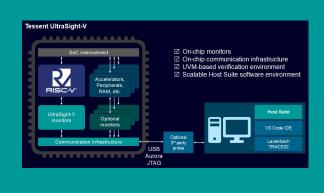

RISC-V on-chip debug & trace solution: Tessent UltraSight-V