# Real-Time Extension to the RISC-V Advanced Interrupt Architecture

Alexey Khomich, Evgenii Paltsev and Paul Stravers

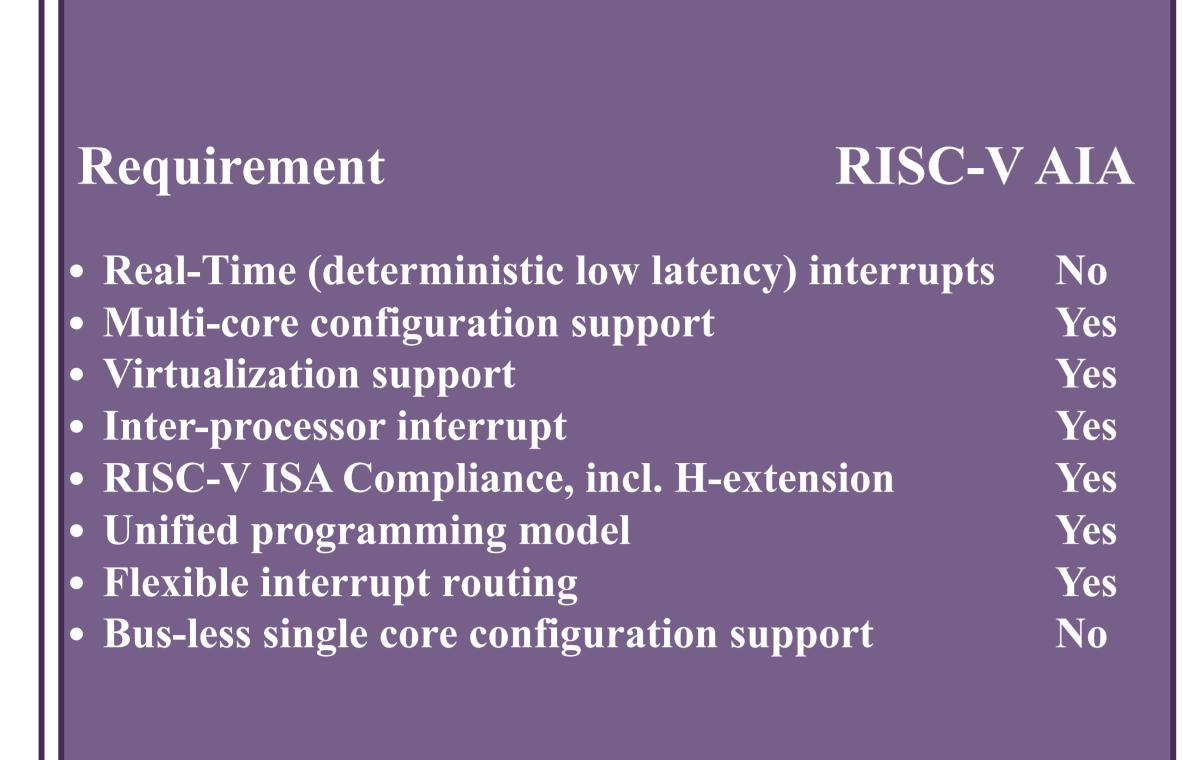

#### Motivation

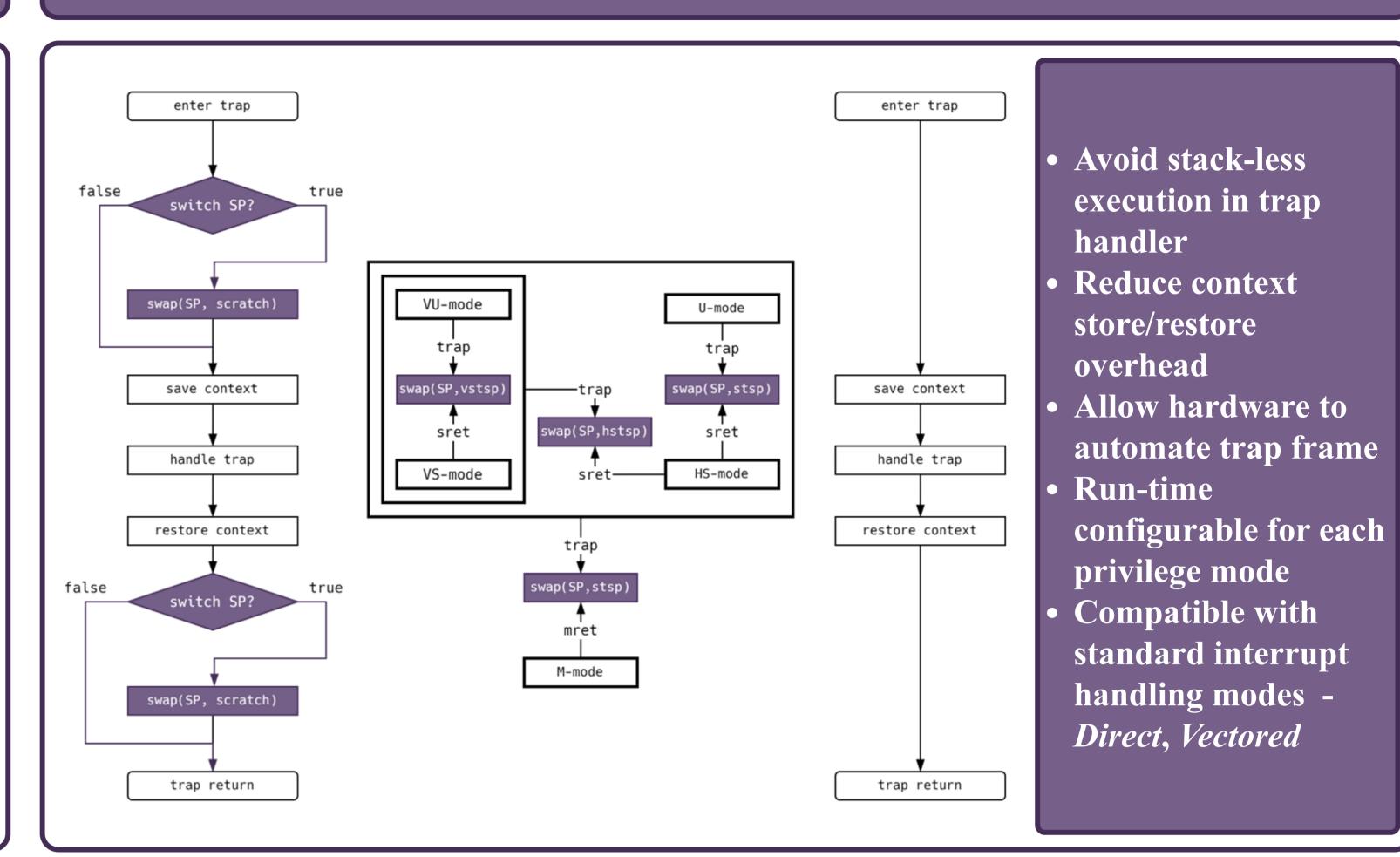

### Trap Stack Pointer Management

Proposed Extensions:

- Nested vectored interrupts

- Low latency interrupt delivery

- Light weight realtime interrupt architecture

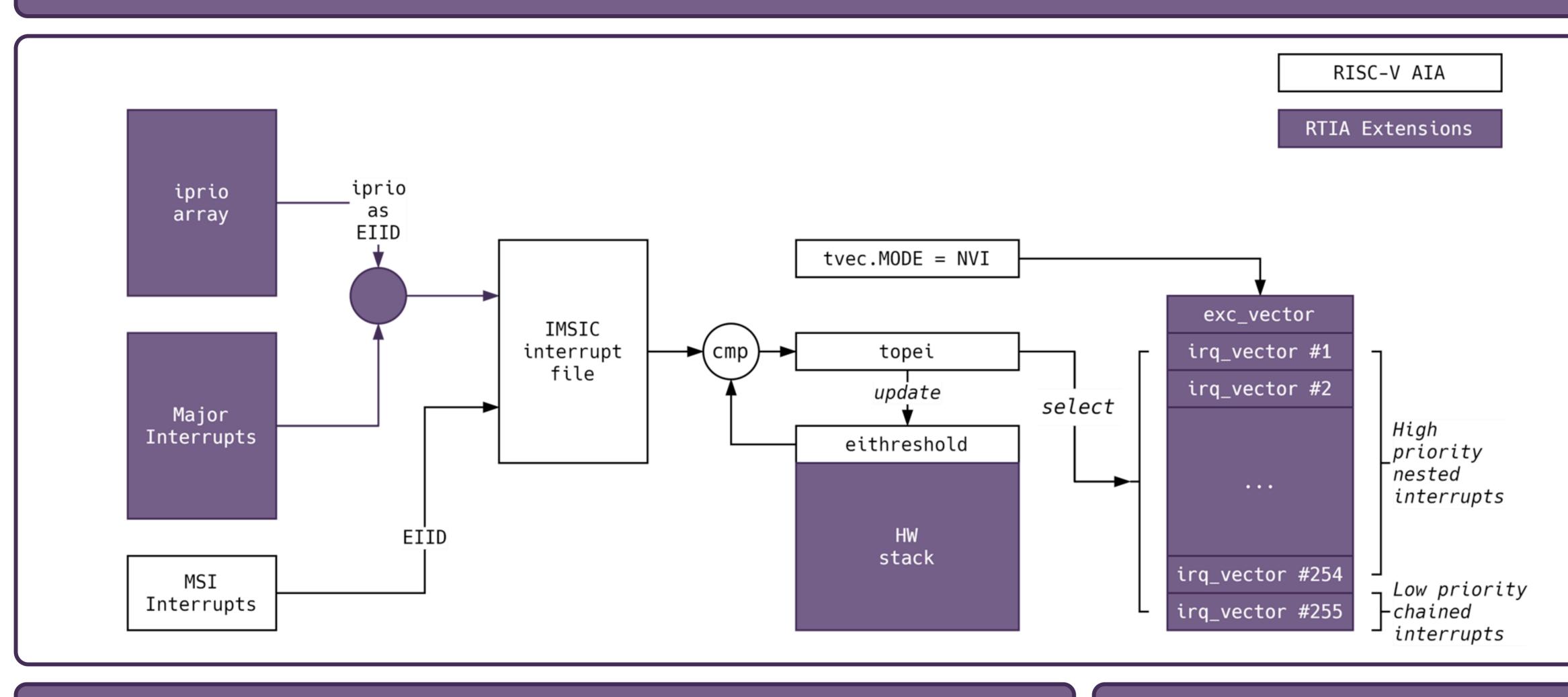

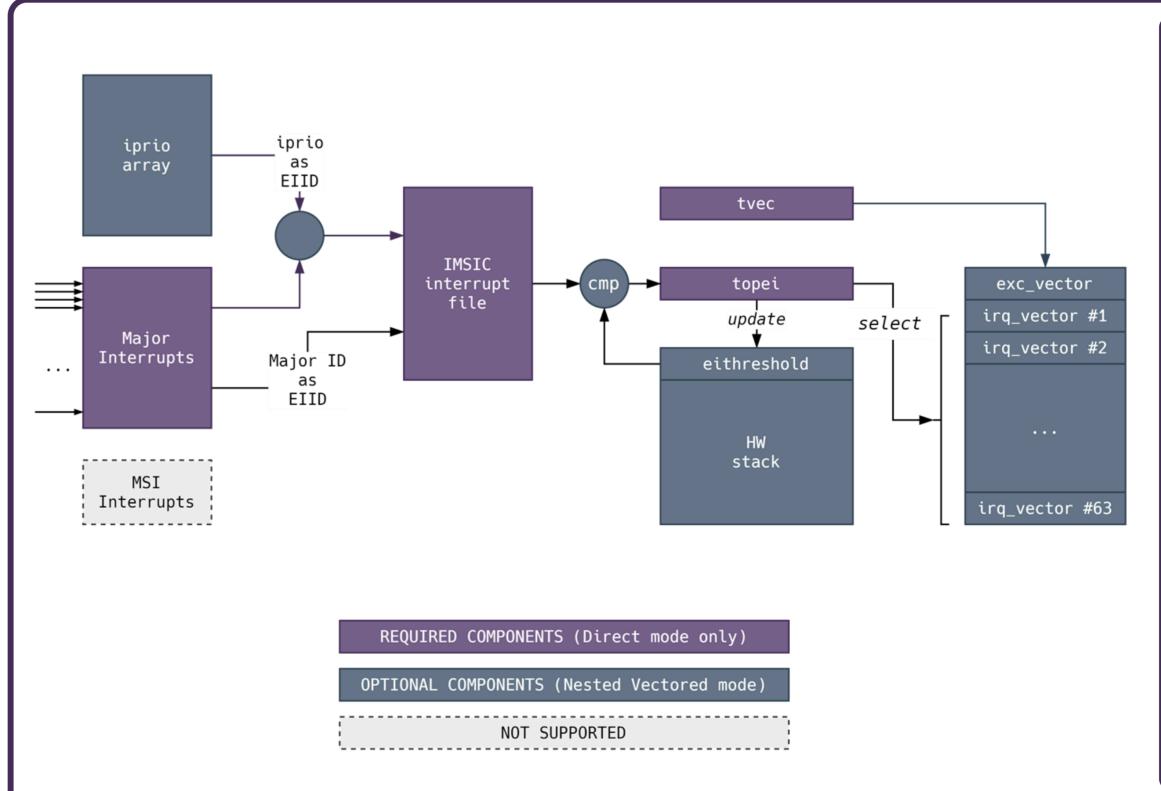

#### Nested Vectored Interrupts

- New Nested Vectored interrupt handling mode

- Major interrupt reporting via IMSIC file (use *iprio* as EIID)

- External interrupt vectors table:

- Single shared exception trap vector

- Up to 255 high priority nested interrupts

- Lower priority chained interrupts (share single vector)

- Automatic external interrupt claim and jump by vector

- Interrupt complete triggered from software

- Interrupt priority level threshold update at claim/complete

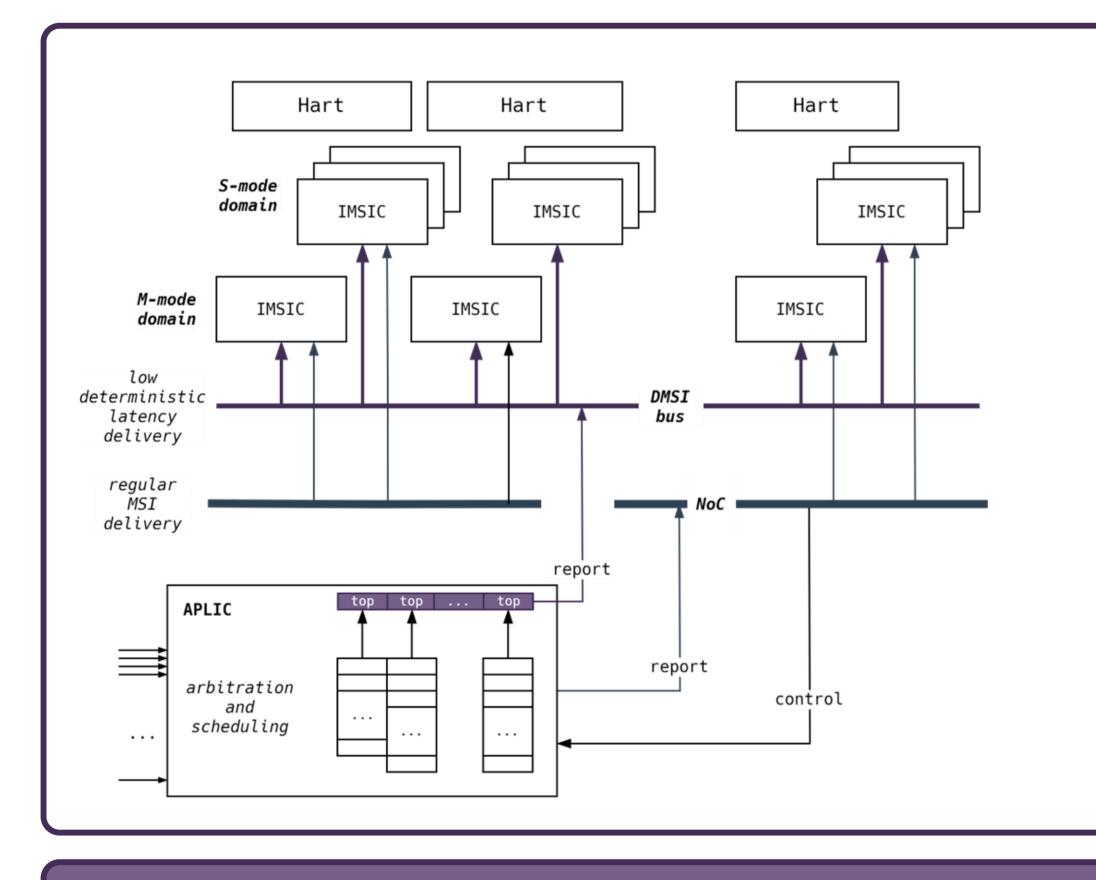

#### Real-Time Interrupt Delivery

# Light Weight Real-Time Interrupt Architecture

- New optional Direct Message

Signaling Interrupt (DMSI)

delivery mode

Configurable for each

- Configurable for each interrupt source at APLIC side

- Wide bandwidth, deterministic low latency DMSI bus

- Delivery prioritization by domain, target, priority

- DMSI cannot be initiated in software, regular MSI can be used for IPI

- Core major interrupts routed via M-mode IMSIC file

- Fixed or configurable major interrupt priorities (*iprio* array) are used as IMSIC EIIDs

- Optional interrupt threshold and Nested Vectored interrupt handling mode with up to 63 priority levels

- Backward

compatibility with

RISC-V Privileged ISA

and AIA

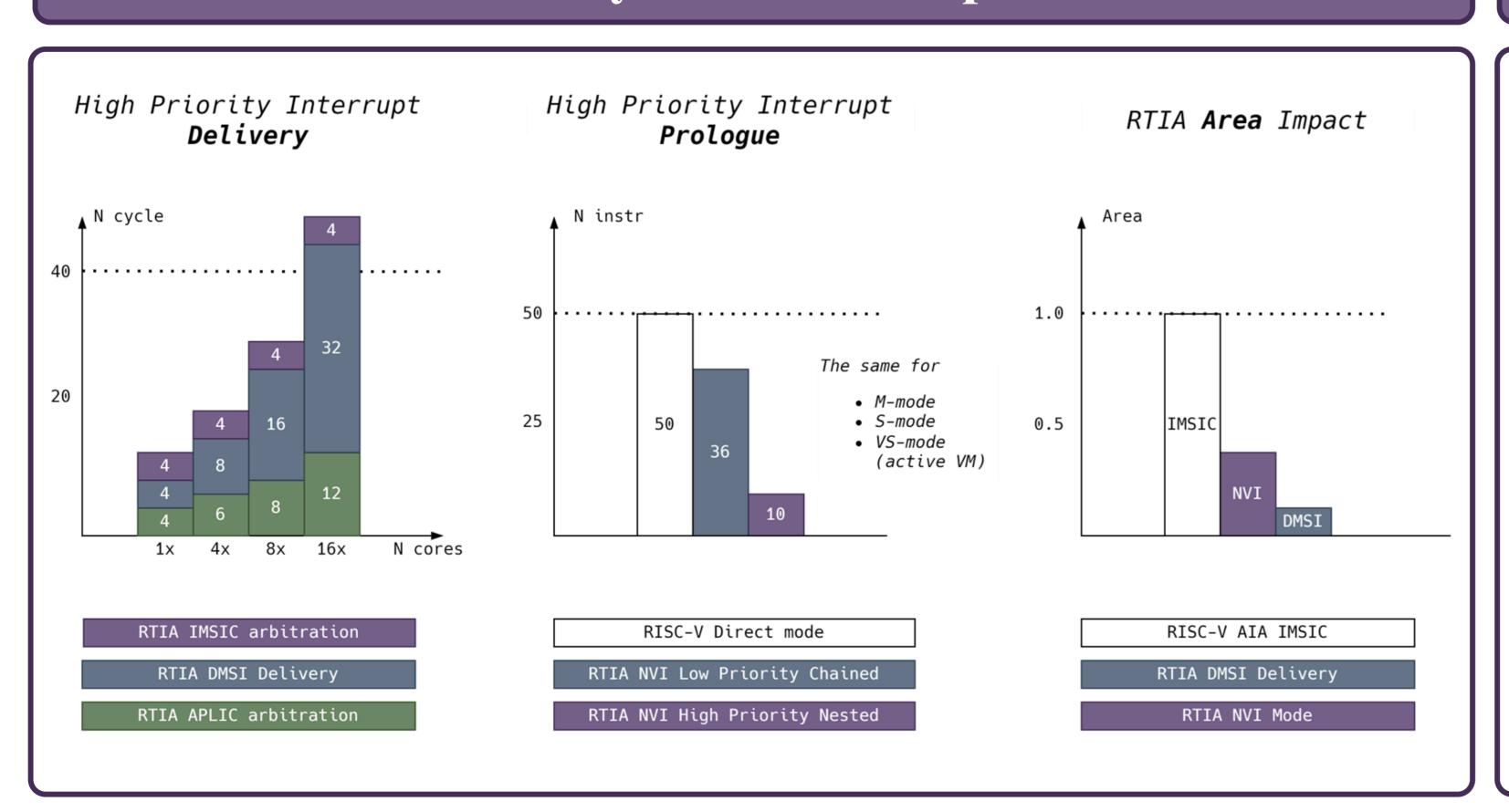

#### Latency and Area Impact

## RTIA Extensions Development Status

#### Completed

- **Synopsys RTIA Specification**

- Functional simulator

- Functional simulation

Functional tests

- Compiler support

- Synopsys ARC-V core IP (M/S/U-mode, no virtualization) RTL

#### In progress

- Synopsys ARC-V core IP (incl. Hextension) RTL

- Virtualization software prototype (Type-1) hypervisor

- RTIA support for Linux kernel

- OSS RTOSes porting

#### Plans

• RISC-V RTIA Specification Proposal