# SCAR: Selective Cache Address Remapping for Mitigating Cache **Side-Channel Attacks**

Pavitra Prakash Bhade Indian Institute of Technology Goa, India pavitra19231101@iitgoa.ac.in

**Olivier Sentieys** olivier.sentieys@inria.fr

Sharad Sinha University of Rennes, Inria, France *Invia* Indian Institute of Technology Goa, India sharad@iitgoa.ac.in

## Introduction

- Cache side-channel attacks (CSCA), exploiting cache conflicts, pose serious risks in shared cache environments.

- Current defenses rely on full encryption of cache mappings to prevent eviction-based attacks like Flush+Reload, Prime+Probe.

- Full mapping encryption introduces significant performance overhead and is vulnerable to predictive analysis due to uniform address coverage.

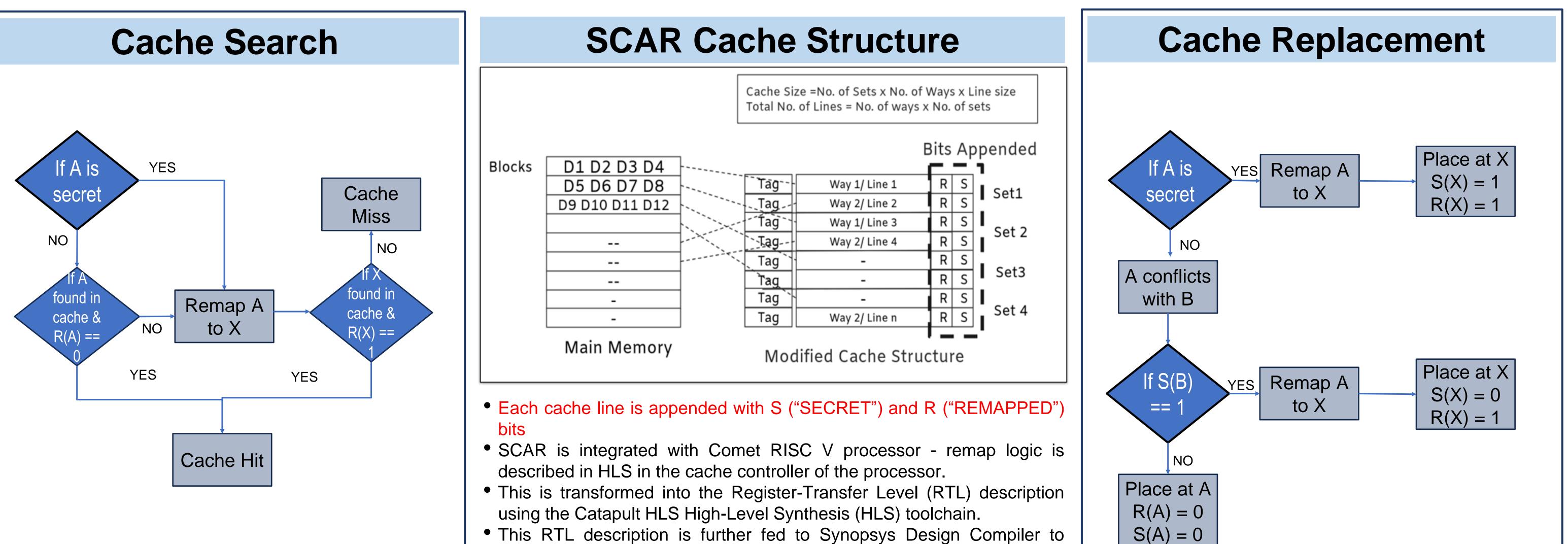

- SCAR is a selective mapping technique that encrypts only critical regions, reducing attack surfaces and performance impact.

- The approach requires minimal changes to cache microarchitecture and replacement policies, making it ideal for RISC-V systems.

- Implementation on a RISC-V core shows only negligible performance overhead with improved security.

## **Proposed Algorithms and Cache Structure**

#### transform it into a gate-level netlist using a 28nm FDSOI technology.

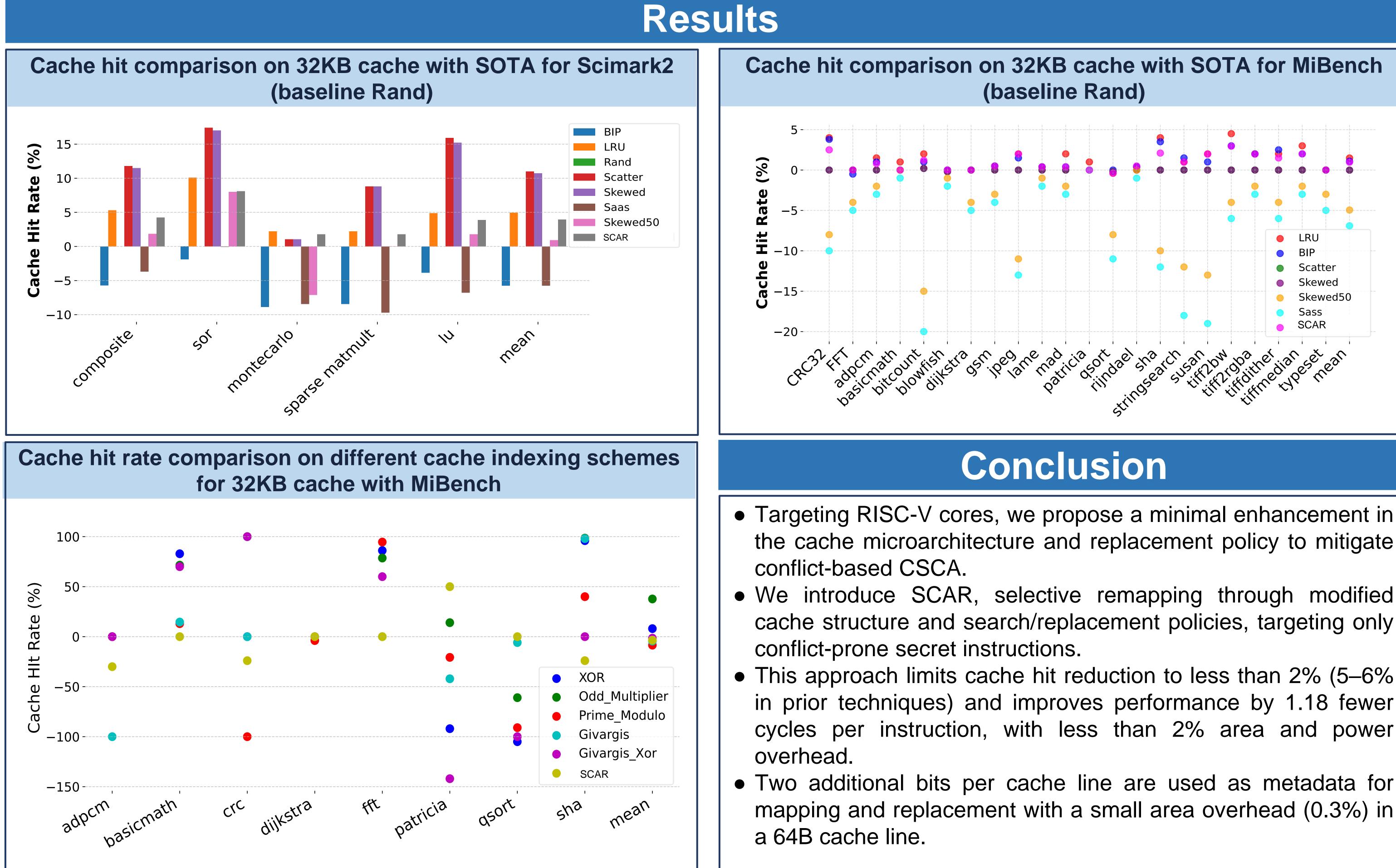

- the cache microarchitecture and replacement policy to mitigate

- We introduce SCAR, selective remapping through modified cache structure and search/replacement policies, targeting only

- This approach limits cache hit reduction to less than 2% (5–6%) in prior techniques) and improves performance by 1.18 fewer cycles per instruction, with less than 2% area and power

- Two additional bits per cache line are used as metadata for mapping and replacement with a small area overhead (0.3%) in

#### **RISC-V SUMMIT EUROPE 2025 (Paris, France)**