# **Comprehensive Lockstep Verification for** leti NAND ELEC. NaxRiscv SoC integrating RISCV-DV, RVLS, and Questa/UVM

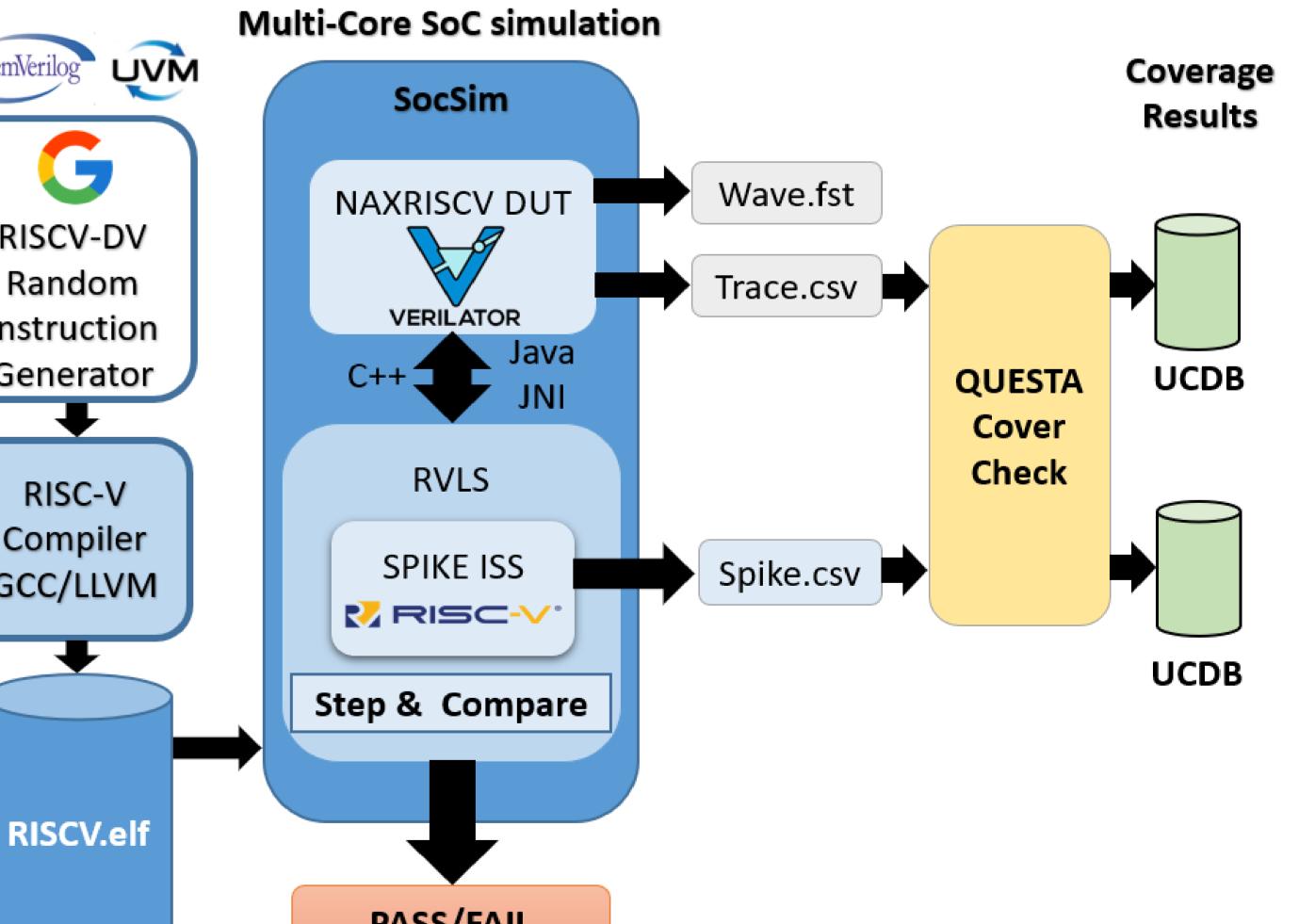

Our lockstep verification framework for the NaxRiscv OoO superscalar core combines hybrid RTL/ISS simulation via RVLS, constrained-random test generation with RISCV-DV, and coverage collection through Questa/UVM to enable early detection of corner-case bugs and ensure strict ISA compliance.

# Introduction

We overcome the complexity of modern processor verification by performing lockstep co-simulation of the NaxRiscv RTL using Verilator and Spike ISS

# **Automated Verification Pipline Powered by Jenkins Cl**

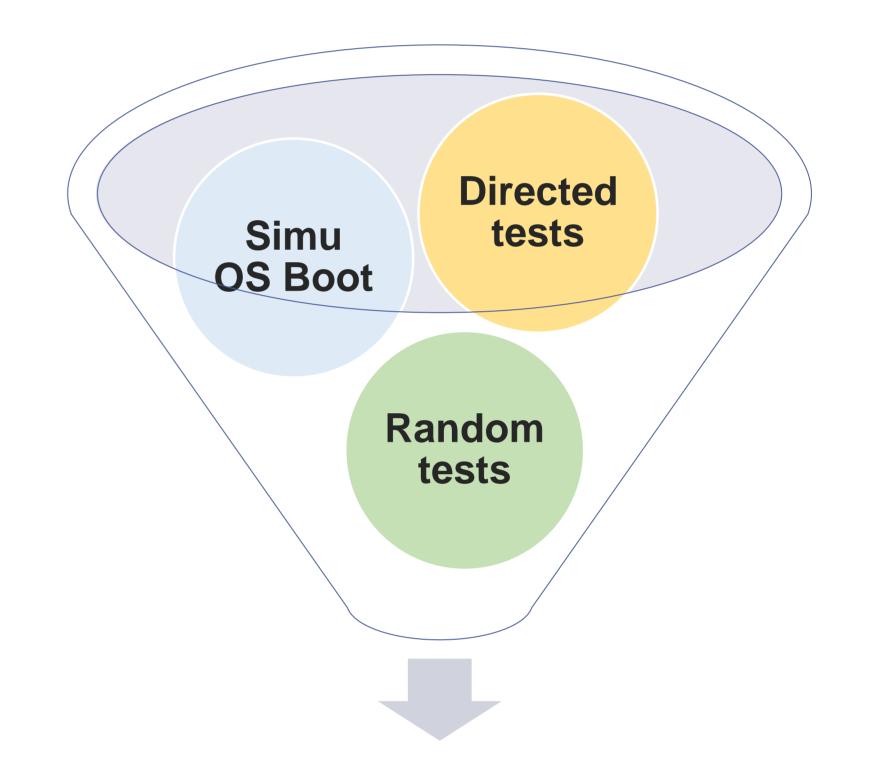

- **Directed Testing**

- Riscv-tests / Riscv-arch-tests (ISA compliance).

- 2. Real-World Benchmarks

- CoreMark, Dhrystone, FreeRTOS/Linux boot.

- 3. Constrained-Random Testing

- RISCV-DV (edge cases, interrupts, hazards).

#### 4. <u>Coverage Collection</u>

Questa to create coverage report frome ISS trace.

| Result Overview                |                         |

|--------------------------------|-------------------------|

| Issue                          | Triggred exception      |

| I/O memory mapping<br>mismatch | Trap store access fault |

| Misaligned instructions        | Load page fault         |

| CSR configuration<br>mismatch  | Missed trap in DUT      |

#### **Functionally verified design**

# Conclusion

#### PASS/FAIL

### **Benefits**

- A lockstep cycle-accurate SoC verification. Ο

- Fully automated Jenkins CI/CD pipline. Ο

- Collection of coverage reports.

- Early detection of critical corner cases. Ο

#### Perspectives

- Automation of coverage reporting merge. • Jenkins deploys tests on FPGA via LiTex.

- Integration of RVFI for a formal verification.

Authors : BILLAL IGHILAHRIZ, OLIVIER SAVRY

1. Univ. Grenoble Alpes, CEA, Leti, F-38000 Grenoble, France

BILLAL.IGHILAHRIZ@CEA.FR OLIVIER.SAVRY@CEA.FR

[1] <u>https://github.com/SpinalHDL/NaxRiscv</u>

[2] https://github.com/chipsalliance/riscv-dv