**Supercomputing** Centro Nacional de Supercomputación

# WebRISC-V: a 64-bit RISC-V Pipeline Simulator for Computer Architecture Classes

Roberto Giorgi<sup>1,2</sup> and Gianfranco Mariotti<sup>1</sup>

<sup>1</sup> Department of Information Engineering and Mathematics, University of Siena - Italy

<sup>2</sup> Barcelona Supercomputing Center (BSC) - Spain

mariotti@diism.unisi.it giorgi@unisi.it

### Motivation

Contributing to the RISC-V acceptance in the Computer Architecture education communities by smoothing the migration from MIPS to RISC-V in classes, through the creation of a simple and easily accessible tool to test RISC-V programs on a pipelined processor

## Achievements

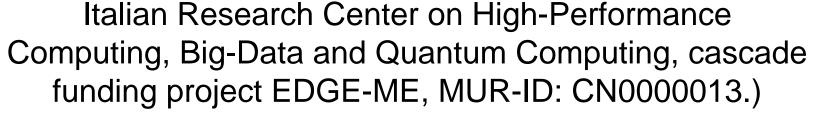

- WebRISC-V is released as open source under the permissive BSD license [1]; it is possible to test it online at http://www.dii.unisi.it/~giorgi/WebRISC-V

- WebRISC-V was first presented in Phoenix, AZ, USA

## The need for RISC-V Educational Tools

- RISC-V is what Computer Architecture teachers are looking for: not tighten to a few vendors!

- It is open and the standard is maintained by the non-profit RISC-V Foundation [3]

- RISC-V educational tools are needed understand the sw/hw intricacies and basic concepts [4]

at the WCAE @ ISCA 2019, it is Open Access on the ACM digital library [2] and it continues to evolve!

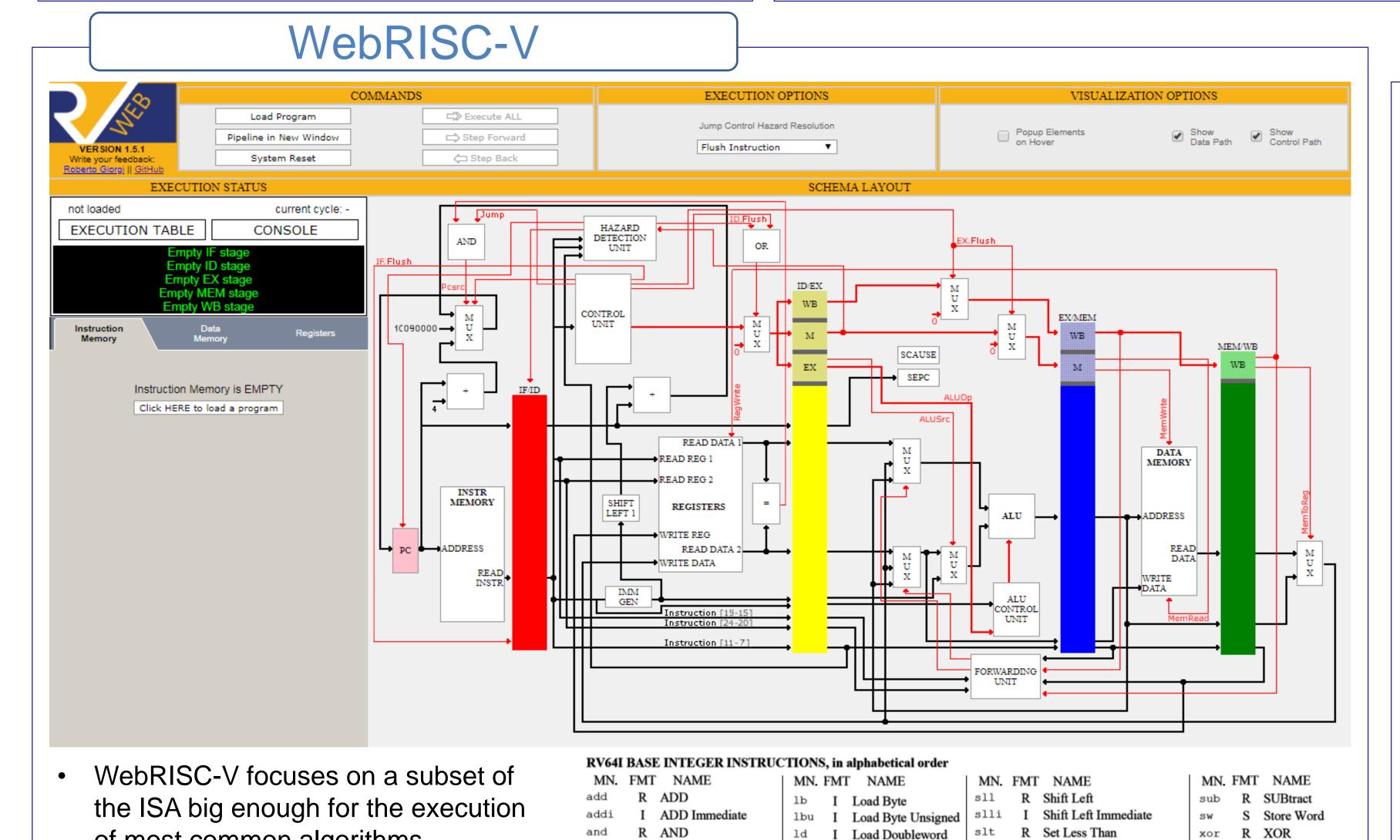

## Comparison with other **Datapath simulators**

WebRISC-V was compared with several Datapath simulators of several architectures: WinDLX [6] of DLX, MARS MIPS X-Ray [7], DrMIPS [8], Mipster32 [9], UCOMIPSIM [10], Visimips [11], WASP [12], WebMIPS [13] of MIPS and Ripes [14] of RISC-V.

The following table was produced from this process.

|      |            | Graphical                     | Visualization             |                 | path<br>entation | Web<br>Accessibility         |                    |  |

|------|------------|-------------------------------|---------------------------|-----------------|------------------|------------------------------|--------------------|--|

|      |            | Presentation                  | Architectural<br>Elements | syngle<br>cycle | pipelined        | $_{\rm side^1}^{\rm client}$ | server<br>$side^2$ |  |

| DLX  | WINDLX     | Stage<br>Blocks               |                           |                 | ~                |                              |                    |  |

|      | MARS X-RAY | Datapath                      |                           | ~               |                  |                              |                    |  |

|      | DrMIPS     | Datapath with<br>Control Unit | $\checkmark$              | ~               | ~                |                              |                    |  |

| S    | Mipster32  | Stage<br>Blocks               |                           |                 | ~                |                              |                    |  |

| MIPS | UCOMIPSIM  | Datapath with<br>Control Unit | √                         |                 | ~                |                              |                    |  |

|      | Visimips   | Datapath with<br>Control Unit |                           |                 | ~                |                              |                    |  |

|      | WASP       | Datapath with<br>Control Unit | ✓                         |                 | ~                | √                            |                    |  |

|      | WebMIPS    | Datapath with<br>Control Unit | ✓                         |                 | ~                |                              | √                  |  |

| .    |            |                               |                           |                 |                  |                              |                    |  |

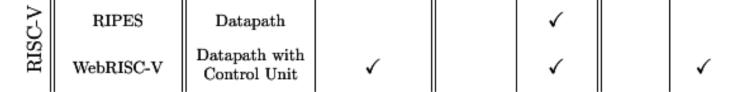

of most common algorithms RIPES WebRISC-V is a 64-bit simulator: it

implements the RV64I base part and the RV64M extension [5]

| andi   | Ι  | AND Immediate        | lh  | Ι | Load Halfword    | slti  | Ι | Set Less Than Immediate  | xori                            | Ι | XOR Immediate |

|--------|----|----------------------|-----|---|------------------|-------|---|--------------------------|---------------------------------|---|---------------|

| beq    | SB | Branch EQual         | lw  | Ι | Load Word        | sltiu | I | Set < Immediate Unsigned |                                 |   |               |

| bne    | SB | Branch Not Equal     | or  | R | OR               | sltu  | R | Set Less Than Unsigned   | <b>RV64M Multiply Extension</b> |   |               |

| ebreak | Ι  | Environment BREAK    | ori | Ι | OR Immediate     | sra   | R | Shift Right Arithmetic   | mul                             | R | MULtiply      |

| ecall  | Ι  | Environment CALL     | sb  | S | Store Byte       | srai  | Ι | Shift Right Arith Imm    | mulh                            | R | MULtiply High |

| jal    | UJ | Jump & Link          | sd  | S | Store Doubleword | srl   | R | Shift Right              | div                             | R | DIVide        |

| jalr   | Ι  | Jump & Link Register | sh  | S | Store Halfword   | srli  | I | Shift Right Immediate    | rem                             | R | REMainder     |

<sup>&</sup>lt;sup>1</sup>Additional plug-ins required. <sup>2</sup>Accessible directly from the Web without the use of plug-ins.

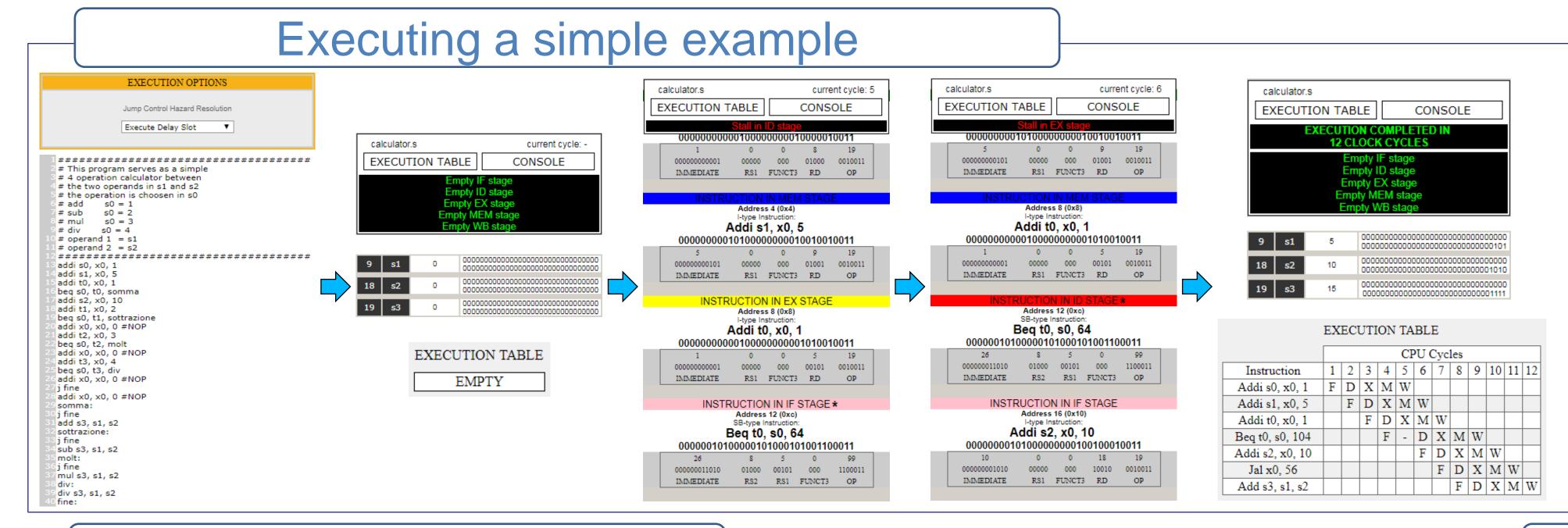

Here we can see some snippets of an execution, with the Delay Slot activated, of the example code "Simple Calculator". We can see the occurrence and passing through the pipeline of stalls and the instructions that generated them, what happens in memory, what happens in the registers and the clock cycles necessary for the code provided.

#### References

- [1] G. Mariotti and R. Giorgi, "WebRISC-V" : https://github.com/Mariotti94/WebRISC-V

- [2] G. Mariotti and R. Giorgi, "WebRISC-V: A Web-Based Education-Oriented RISC-V Pipeline Simulation Environment", 2019

- [3] K. Asanovic, "RISC-V State of the Union", RISC-V Workshop, Zurich, 11 June 2019.

- [4] C. Redmond, "Guiding the Future of RISC-V", RISC-V Workshop, Zurich, 11 June 2019.

- [5] D. A. Patterson and J. L. Hennessy, "Computer Organization and Design RISC-V Edition: The Hardware Software Interface, 1st ed.", 2017

- [6] H. Grunbacher and H. Khosravipour, "WinDLX and MIPSim pipeline simulators for teaching computer architecture", 1996

- [7] G. C. R. Sales, M. R. D. Araújo, F. L. C. Pádua, and F. L. Correa Júnior, "MIPS X-Ray: A plug-in to MARS simulator for datapath visualization", 2010

- [8] B. Nova, J. C. Ferreira, and A. Araújo, "Tool to support computer architecture teaching and learning", 2013

- [9] J. C. de Oliveira Quintas, "Mipster32: A 32 bit MIPS Simulator", 2017

## Acknowledgements

This work is partly funded by the Barcelona Zettascale Laboratory, promoted by the Spanish Ministry for Digital Transformation and the Civil Service, within the framework of the Recovery, Transformation and Resilience Plan - Funded by the European Union -NextGenerationEU and via the PNRR M4C2-Inv1.4