## Auto-Transcode into RISCV Vector Code from Other Vector/ SIMD ISAs using LLVM Infrastructure

(Quickly Bring-up Optimized Libraries and Workloads on RISCV Vector and Other Architectires)

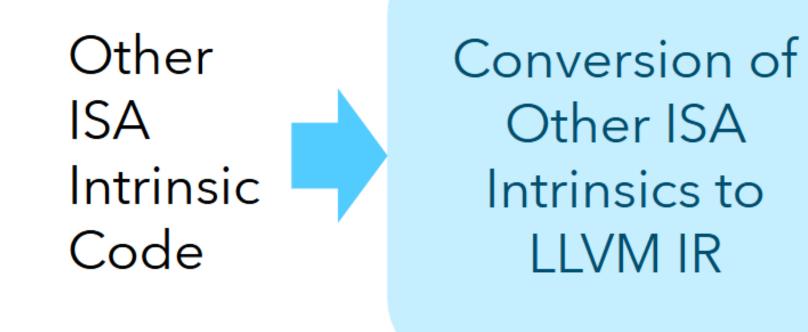

• Auto Re-Vectorization Flow

Modification of Input ISA Attributes to RISCV Vector Attributes

Execution of LLVM Vector Optimizer Passes for RVV Target

Lowering of LLVM IR to RISCV Vector Assembly

RISCV Vector Assembly Code

General Compilation Flow

## **Example Result with Matmul Kernel**

| Target Processor | Generic Flow<br>(cycles) | Auto Re-Vectorization<br>Flow<br>(cycles) | Performance Gain |

|------------------|--------------------------|-------------------------------------------|------------------|

| SiFive X280      | 548                      | 315                                       | 1.74 x           |

| SiFive P670      | 91                       | 52                                        | 1.75 x           |

- Quickly bring up optimized libraries and workloads on processors with new architectures like RVV1.0 (reduces manual effort)

Can be a more efficient starting point for further hand-optimization

Modular design - leverages LLVM infrastructure - so can be extended

- to any input and output ISAs supported in the LLVM ecosystem

- Plans to open-source the tool

- Nisanth Mathilakath Padinharepatt, Sanket Lonkar,

- **MIPS Technologies**

Scan QR for More Details >