# **Modular SAIL: dream or reality?**

Petr Kourzanov, Anmol Anmol

Imec DSRD Compute Systems Architecture (CSA) Kapeldreef 75, 3001 Leuven, Belgium. {first}.{last}@imec.be

#### **Artefacts:**

Know more about us:

## INTRODUCTION

**Unlocking the Full Potential of RISC-V ISA Modularity: Addressing Compositionality Challenge**: To fully benefit from RISC-V ISA modularity, the community must address compositionality. This involves extending beyond module specifications. It encompasses broader aspects of the RISC-V development flow, including *emulation*, *simulation*, *testing* and verification.

# **Our Proposal: Modular SAIL**

- An approach to infuse compositionality into the SAIL-RISCV golden model.

- **Feasibility**: We demonstrate that it is possible to adapt the flow (and in future, the SAIL compiler itself) to support modules at the emulator level. - **Results**: Comparative study of the pluggable emulator's overheads

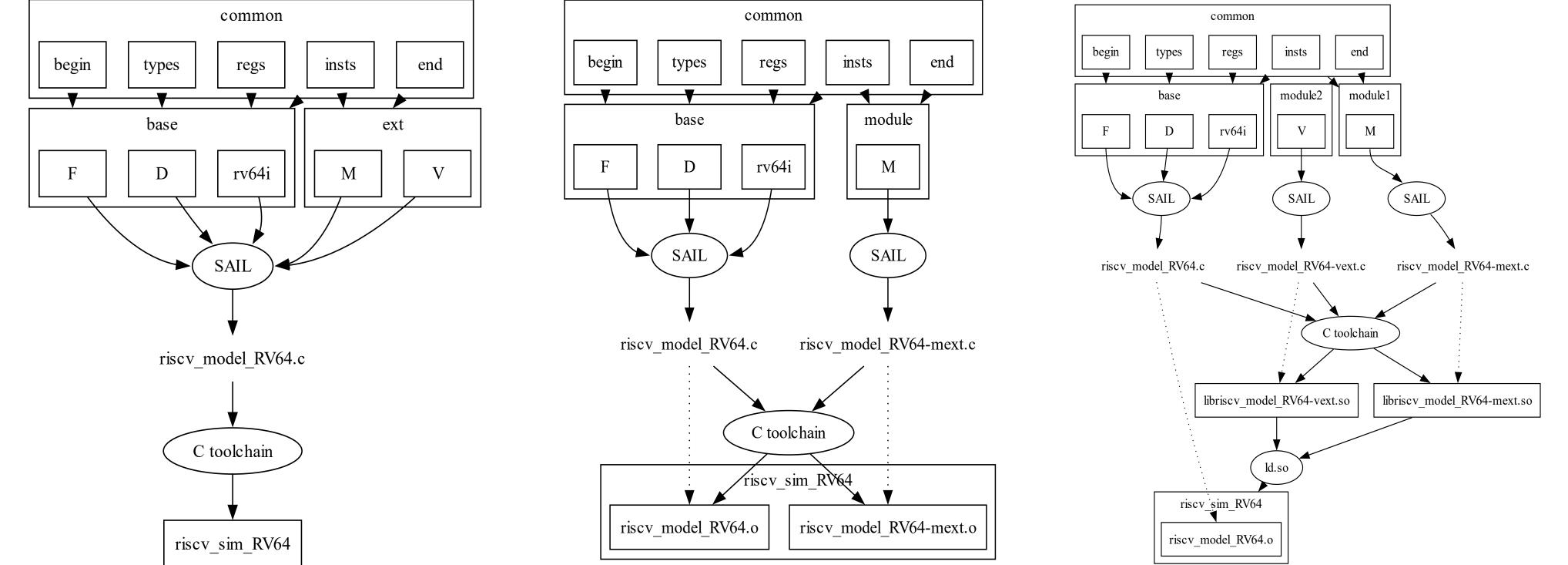

Our methodology centers on transforming a monolithic SAIL-RISCV emulator into a modular design that enhances compositionality and facilitates both static and dynamic module bindings **Approach:** Decompose the original monolithic emulator into a base module and individual extension modules. This separation allows each extension to expose a well-defined API while relying on a shared architectural state provided by the base emulator.

METHODOLOGY

Modular variants on top of (0) Baseline LTO: (1) Statically linked static binding, (2) Statically linked (semi-Dynamic binding, and (3) Runtime-linked Dynamic binding (see IMPLEMENTATION)

- for both static and dynamic bindings

- Same functional behavior as the original monolithic emulator (RISC-V ISS)

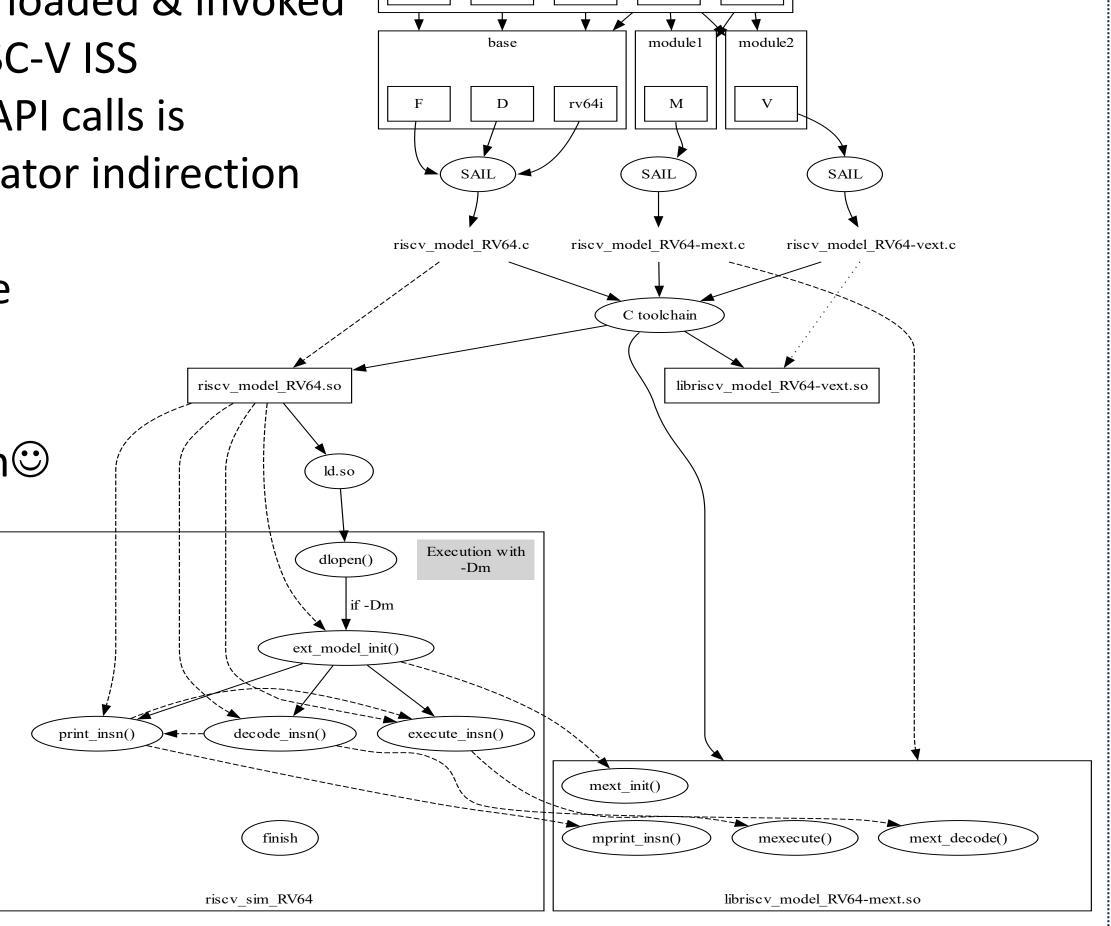

Fig 1: Proposed changes to the baseline SAIL flow (0): Static M (1), Semi-Dynamic M & V (2)

#### **EXPERIMENTAL RESULTS**

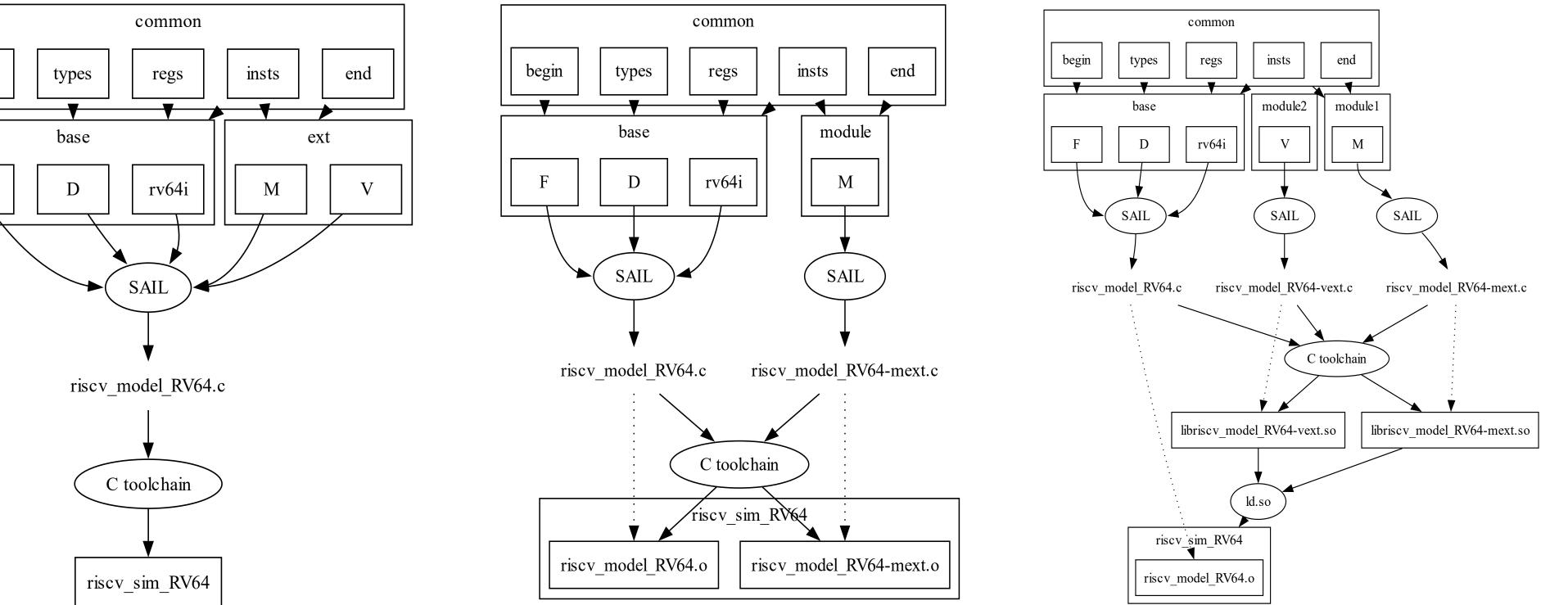

- We evaluated the performance of the pluggable emulator using static, and dynamic bindings Our performance evaluation on dedicated Xeon systems demonstrates that both static and dynamic binding techniques preserve the functional behavior of the original monolithic SAIL-RISCV emulator, and that the performance is in many cases improved

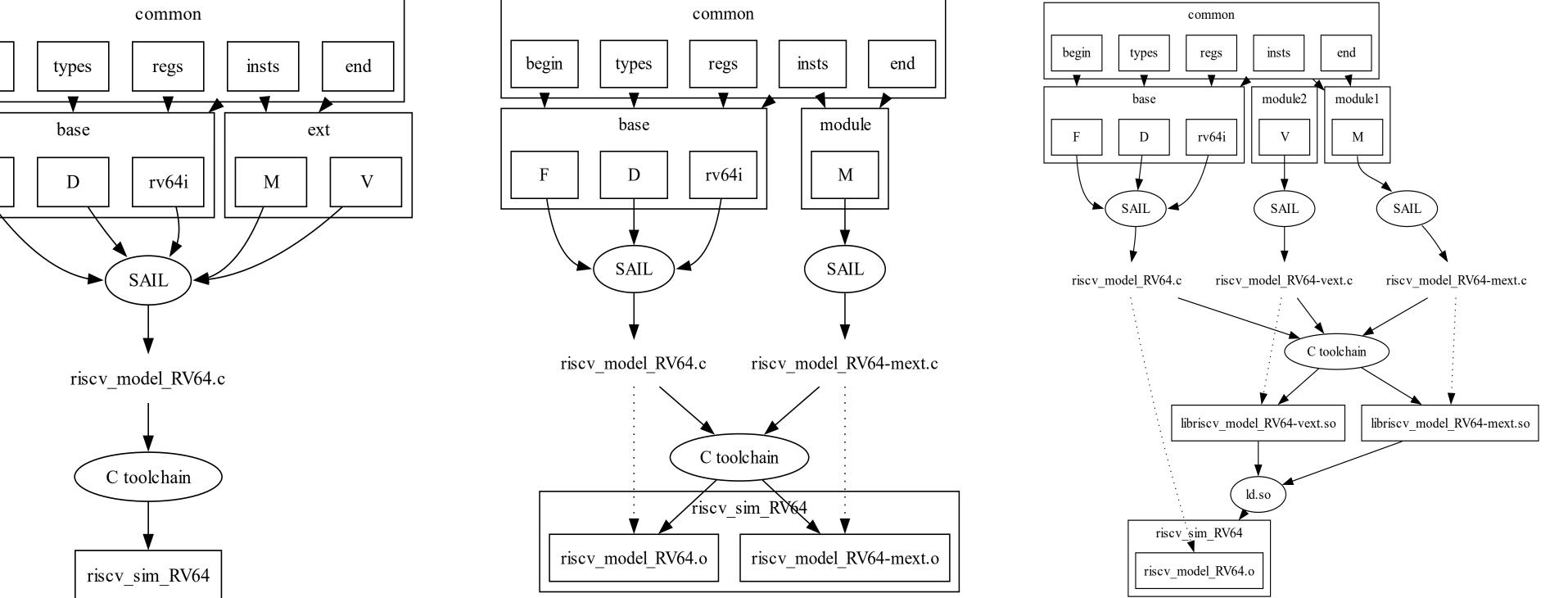

- The modular approach incurs no excessive binary size overheads. While the baseline LTO is still the most code size-efficient solution the segregation of base model and extension models into modules with static- or dynamic binding does not compromise code size.

### IMPLEMENTATION

- Each module in our system provides a clear API for querying, initializing, decoding, executing, and pretty-printing instructions. These module emulators support only the instructions from their defined ISA extensions and rely on the base emulator module for e.g., RF, system context and LSU

- Integration is done through simple patch that adds required calls to respective functions in **zstep()** and **model\_init()** of the base emulator.

- Statically linked static and dynamic bindings are inserted directly into the code for the Static case (1) and Semi-Dynamic case (2)

- For Fully-Dynamic (case 3) extension lacksquare

loading is parameterized from cmdline Only used modules are loaded & invoked begin for execution of the RISC-V ISS Insertion of extension API calls is performed via an simulator indirection

Results are positive:

- Less cache pressure

- Less branching

**Fig 4:** Proposed SAIL flow changes for the Fully-Dynamic **M** (3)

#### **CONCLUSION AND FUTURE WORK**

#### REFERENCES

This experiment validates that:

- injecting compositionality into the SAIL-RISCV flow is not only feasible but also 1. advantageous for the evolving RISC-V ecosystem

- 2. By decoupling extensions from the base emulator, vendors can independently develop and exchange dynamic libraries without exposing proprietary details

- thereby fostering a more open, collaborative and secure environment. 3.

This modularization strategy paves the way for future enhancements, such as

- on-demand loading and runtime certification of extension modules

- supporting further extensions as modules, including floating-point **F**, **D** as well as **VectorCrypto** or the upcoming IME/AME/AI enhancements

We believe that this work represents a significant step toward creating a scalable, adaptable, and compositional framework that meets the growing complexity of modern **RISC-V** designs.

[1] Andrew Waterman, "The RISC-V instruction set". https://doi.org/10.1109/HOTCHIPS.2013.7478332 [2] Open Vector Iface. https://shorturl.at/ulFa9 [3] CORE-V-XIF. <u>https://shorturl.at/egnAV</u> [4] CX Proposal. <u>https://shorturl.at/ufIGF</u> [5] SAIL. <u>https://github.com/rems-project/sail</u> [6] Model. <u>https://github.com/riscv/sail-riscv</u> [7] Spike RISC-V ISS. <u>https://shorturl.at/OOBlf</u> [8] CBI from Codasip. https://shorturl.at/X61Kj [9] Evaluating a RISC-V processor running Benchmarks using the QEMU VP: https://shorturl.at/aF11p