RISC-V®

## **Embedded FPGA-Shell:**

# **Emulating RISC-V Architectures at FPGA**

Sajjad Ahmed<sup>1</sup>, Elias Perdomo<sup>1,2</sup>, Joan Teruel<sup>1</sup>, Mostafa Mojahed<sup>1</sup>, Alexander Kropotov<sup>1</sup>, Teresa Cervero<sup>1</sup>, Xavier Martorell<sup>1</sup>, Miquel Moretto<sup>1</sup>, Behzad Salami<sup>1</sup>

[sajjad.ahmed, elias.perdomo, joan.teruel, mostafa.mojahed, alexander.kropotov, teresa.cervero, xavier.martorell, miquel.moreto, behzad.salami]@bsc.es

<sup>1</sup>Department of Computer Sciences, Barcelona Supercomputing Center

<sup>2</sup>Universidad Politécnica de Cataluña

## **MOTIVATIO**

- ✓ FPGA validation is extential for RISC-V processor development and system-level research.

- Developers spend excessive time wiring up interfaces (PCIe, DDR, JTAG, etc.) rather than focusing on core architecture.

- K Lack of reusable, modular shells makes porting to new FPGA boards difficult and time-consuming.

- Debug and bring-up processes are fragmented across toolchains and scripts.

- We introduce an open-source, plug-and-play FPGA shell to automate and streamline the emulation of RISC-V multicore designs on AMD platforms.

#### **EMBEDDED FPGA-SHELL**

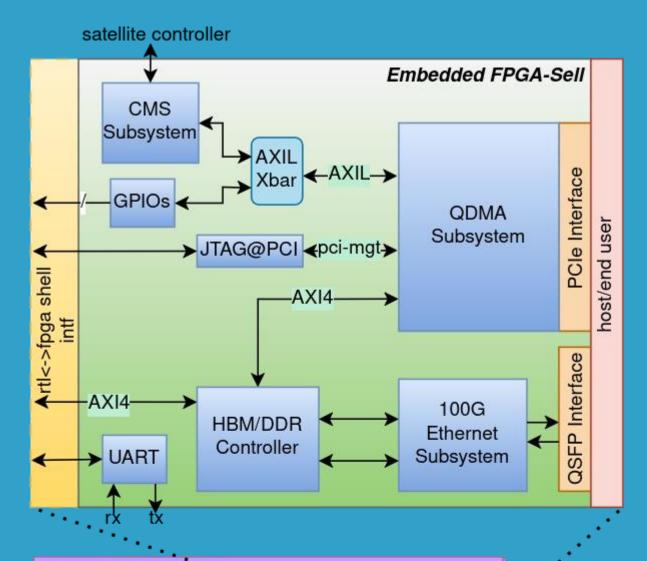

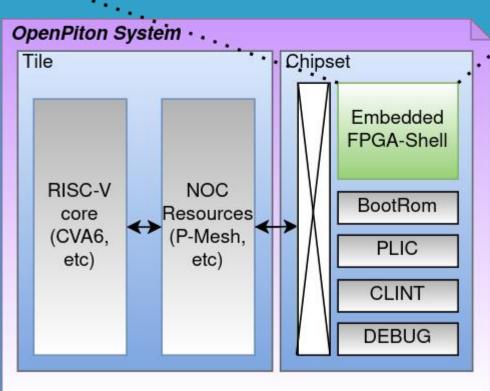

fig#1: Embedded FPGA-Shell architecture integrated with OpenPiton system

#### **ARCHITECTURE**

#### Shell Structure:

- Modular design combining IP blocks, scripts, and integration interfaces.

- Name of the Integrated Peripherals:

- QDMA (PCIe), Ethernet (QSFP), DRAM (DDR4/HBM), UART, JTAG@PCIe, QSPI Flash, CMS.

- **System Integration:**

- Connects directly to OpenPiton's chipset (AXI4/AXI-Lite interfaces).

- Supports CVA6 and in-house designed RISC-V cores.

- **(#)** Communication & Interconnect:

- AXI crossbars for IP integration.

- Aurora (FPGA-FPGA link), PCIe (host communication).

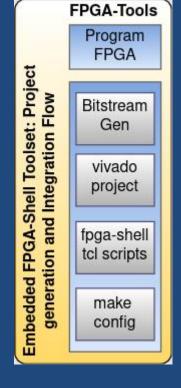

#### **FPGA-TOOLS**

- Project Automation

- Makefile-based config & build flow

- Automates project setup, synthesis, and bitstream generation

- 🕺 Vivado Integration

- **Custom TCL scripts for block** design and IP configuration

- Supports both UltraScale+ and Versal architectures

Dual level debugging (OpenPite

- Debug Toolchain

- JTAG@PCle with OpenOCD

fig#2: FPGA-

Tools

### **EVALUATION**

- Emulated in house and open source Multi Core RISC-V designs.

- Multistage Linux boot verified.

- Performance evaluation (in progress)

| IP       | LUTs<br>(1303680) | CLB<br>Regs<br>(2607360) | BRAM<br>Tile<br>(2016) |

|----------|-------------------|--------------------------|------------------------|

| QDMA     | 49887             | 51468                    | 81.5                   |

| НВМ      | 1073              | 874                      | 4                      |

| Ethernet | 47965             | 68861                    | 29.5                   |

| Others   | 2650              | 3549                     | 0                      |