Plenary sessions

Keynotes and presentations in the Gaston Berger amphitheatre (S2)

Notes for plenary session presenters

Before the conference:

- Presenations shall be prepared as PPTX or PDF files.

- The final asbtract and slides are due for Monday, April 21st, 2025.

- At least one author of the poster must register for the core conference (Tuesday 13 to Thursday 15).

- The slides will be collected beforehand and displayed from a shared laptop.

At the conference:

- Get in touch with your Session Chair long before the session.

- Get in touch with the audio/video team 15 min. before the session.

Quick links to sessions

-

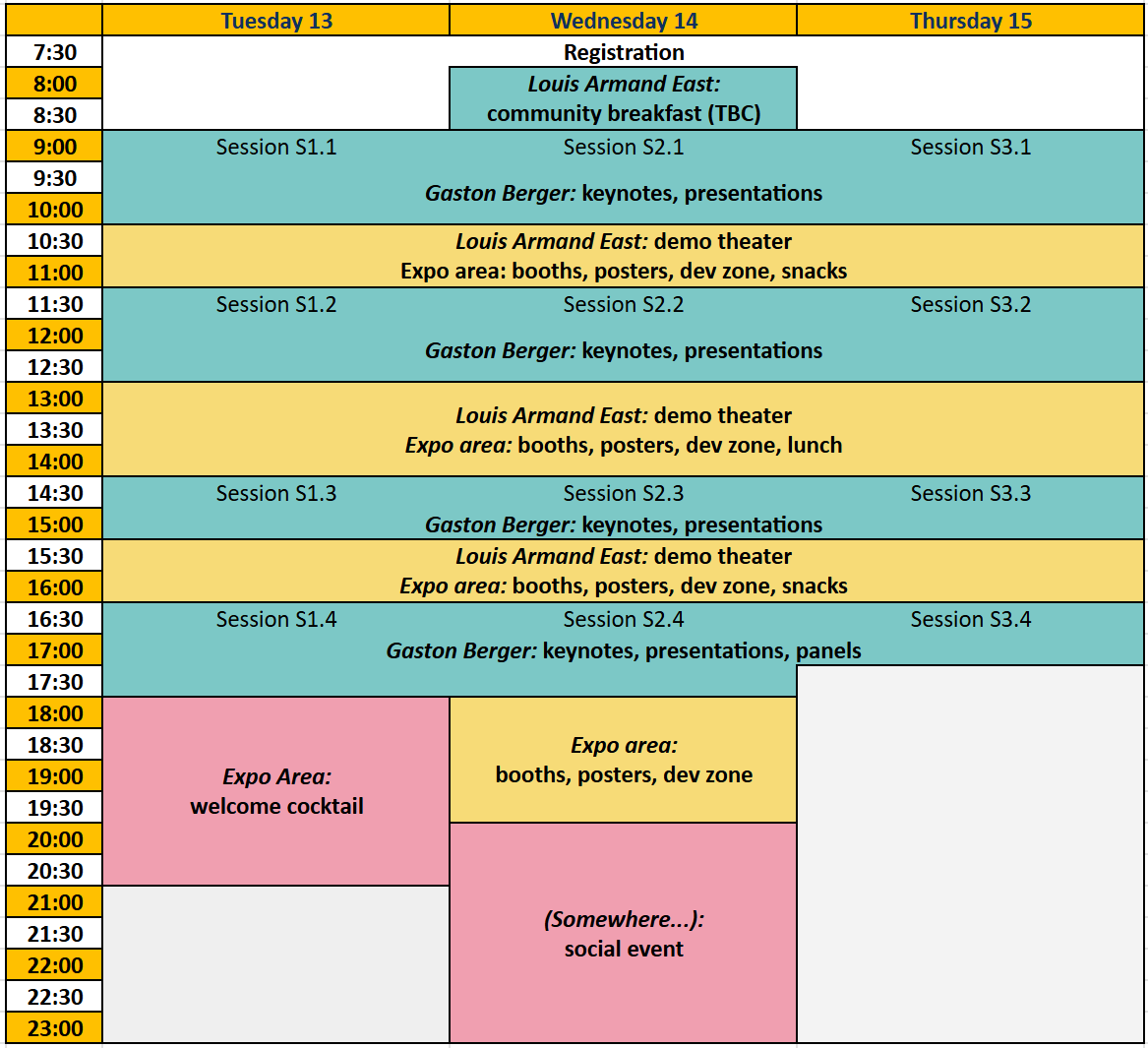

Tuesday 13: T1.1 09:00–10:30 plenary. T1.3 11:30–13:00 plenary. T1.4 13:00–14:30 lunch and demos. T1.5 14:30–15:30 plenary. T1.6 15:30–16:30 break and demos. T1.7 16:30–18:00 plenary.

-

Wednesday 14: T2.0 08:00–09:00 community breakfast. T2.1 09:00–10:30 plenary. T2.2 10:30–11:30 break and demos. T2.3 11:30–13:00 plenary. T2.4 13:00–14:30 lunch and demos. T2.5 14:30–15:30 plenary. T2.7 16:30–18:00 plenary.

-

Thursday 15: T3.1 09:00–10:30 plenary. T3.2 10:30–11:30 break and demos. T3.3 11:30–13:00 plenary. T3.4 13:00–14:30 lunch and demos. T3.5 14:30–15:30 plenary. T3.7 16:30–17:30 plenary.

Plenary sessions & Demos

Keynotes, invited talks, industrial and technical presentations will presented in plenary sessions in the Gaston Berger amphitheater. Demos will presented during lunches and some breaks in the Louis Armand East amphitheater

Tuesday 13, 09:00-10:30

Session chair: Teresa Cervero, BSC.

Plenary keynotes and presentations in Gaston Berger amphitheater (S2).

Welcome to the RISC-V Summit Europe 2025 in Paris

Video . Slides

. T1.1.01, Tue 13 at 09:00, in Gaston Berger (S2).

By Christian Fabre, RISC-V Summit Europe 2025 Local Chair, CEA.

Abstract: The welcome address to the RISC-V Summit Europe 2025 will present the venue, provide an overview of the agenda, and details the social event.

To page top — To session T1.1 — To talk T1.1.01

Program Overview of the RISC-V Summit Europe 2025

Video . Slides

. T1.1.02, Tue 13 at 09:05, in Gaston Berger (S2).

By Borja Perez Pavon, RISC-V Summit Europe 2025 Program Chair, Universidad de Cantabria.

Abstract: Details on the 3 days program, the CfP, the selected talks and the topcis covered.

To page top — To session T1.1 — To talk T1.1.02

RISC-V Leadership Update

Video . Slides

. T1.1.03, Tue 13 at 09:10, in Gaston Berger (S2).

By Lu Dai, Board Chair, RISC-V International, Stefan Wallentowitz, Vice Chair, RISC-V International.

Abstract: An update on leadership at RISC-V international

To page top — To session T1.1 — To talk T1.1.03

From ISA to Industry: Accelerating Technical Progress and RISC-V adoption in 2025

Video . Slides

. T1.1.04, Tue 13 at 09:15, in Gaston Berger (S2).

By Andrea Gallo, RISC-V VP Technology, RISC-V.

Abstract: RISC-V has come a long way from its birth 15 years ago. A decade and a half of technical development and industrial application from the combined efforts of an ever more powerful ecosystem is resulting in adoption across industry verticals from Datacenter to Automotive to High Performance Computing, with SHD group predicting around a 30% RISC-V share in key markets. In this talk we explore the current momentum behind RISC-V, and the plans and activities we are putting in place to make this RISC-V powered future a reality.

To page top — To session T1.1 — To talk T1.1.04

Real Systems. Real Traction. The Next Chapter in High-Performance RISC-V in Data Centers.

Video . Slides

. T1.1.05, Tue 13 at 09:40, in Gaston Berger (S2).

By Balaji Baktha, Founder, President, CEO, and Chairman, Ventana.

Abstract: With AI compute needs reshaping the industry, RISC-V is gaining global momentum—and Ventana is leading that shift. From hyperscaler infrastructure to next-generation automotive platforms, customers are turning to Ventana for real silicon, real systems, and a faster path to deployment.Ventana is accelerating the adoption of high-performance RISC-V systems—from silicon to software, and from cloud to edge. Building on last year’s introduction of RUCA (RISC-V Unified Compute Architecture), this keynote will highlight how strong customer traction is being driven by Ventana’s full-stack platform approach—one that uniquely combines high-performance IP, packaged chiplets, boards, system software, and robust commercial readiness.

Bio: Balaji Baktha is the founder and CEO of Ventana Micro Systems, a leader in high-performance RISC-V processors. He is an experienced semiconductor executive and a serial technology entrepreneur and investor with a proven track record in founding and exiting several successful startups over more than 30 years in Silicon Valley. Balaji is a board member of RISC-V International as well as several other startups, and a Limited Partner and Senior Advisor at PE and VC funds. Prior to Ventana, Balaji was the founder and CEO of Veloce Technologies, the world’s first 64-bit ARM based high performance processor for cloud-compute (acquired by AppliedMicro). Before Veloce, Balaji was the VP and GM of the Communications Business at Marvell Semiconductor where he managed multiple product groups including compute, wired and wireless networking, and Enterprise Storage SoCs. Before Marvell, Balaji co-founded Platys, a startup that pioneered iSCSI storage networking and was subsequently acquired by Adaptec (now Microsemi). Prior to Platys, Balaji founded Shuttle Technologies (acquired by SCM Micro) to build the first digital media & storage I/O SoCs for Apple, Sony, and HP.

To page top — To session T1.1 — To talk T1.1.05

Sovereignty, independence, innovation: 7 years of HW/SW codesign with RISC-V at CEA

Video . Slides

. T1.1.06, Tue 13 at 10:00, in Gaston Berger (S2).

By Thomas Dombek, Head of Digital Integrated Circuits and Systems Department, CEA.

Abstract: By ending the epoch of closed, proprietary ISAs, RISC-V has opened a new era of innovation in the computing world. Its open ISA not only enables the tailoring of architecture to various application domains, from performance to low power, and from safety to security, but it also enables new forms of joint initiatives in the design and tools ecosystem. This ranges from new forums of cooperation between industrial competitors in the market, to new models of industry/academic collaboration. The versatility of open ISA specifications, which enables both open-source, public cooperation and also closed-door commercial agreements, will facilitate new kinds of partnerships and unexpected advances in the computing field at large. This talk will provide a return of experience from seven years of commitment to the RISC-V ecosystem and, a peek at key achievements of CEA and its academic and business partners.

Bio: Thomas Dombek is head of the Digital Systems and Integrated Circuits division at CEA LIST (French Atomic Energy Commission), Saclay, France. He received his master’s degrees in engineering from Ecole Centrale de Lyon, France, and in microelectronics from the Technical University of Darmstadt, Germany, in 1998. He has worked over 15 years in the semiconductor industry at various research and management positions within Philips, NXP and ST-Ericsson France. In 2011, he joined CEA LIST, heading research on software, modeling and hardware challenges in smart embedded systems.

To page top — To session T1.1 — To talk T1.1.06

Enabling the Next Phase of RISC-V: Product Innovation and Scalable Solutions

Video . Slides

. T1.1.07, Tue 13 at 10:15, in Gaston Berger (S2).

By Ning He, SVP and CTO, ESWIN.

Abstract: RISC-V has achieved remarkable success in the IoT application and is now expanding into more advanced scenarios. To sustain this growth, a comprehensive product portfolio, mature software support, and systematic large-scale deployments are essential. This presentation highlights how ESWIN Computing, a leading innovator in RISC-V, enriches the RISC-V ecosystem through multiple industry-first products while enhancing software capabilities. Additionally, we will showcase how our system-level solutions for vertical industries accelerate the structured adoption and widespread deployment of RISC-V, driving the ecosystem’s rapid evolution.

Bio: Dr. Ning He is the Senior Vice President and Chief Technology Officer of ESWIN Computing Technology Co. Ltd, a leading RISC-V products and solutions provider in China. He holds a Bachelor‘s and a Master’s degree from the University of Electronic Science and Technology of China, and a Ph.D. degree in Electrical Engineering from Arizona State University, USA. Prior to joining ESWIN, Dr. He served as Vice President and CTO at a company listed on China’s A-share market. With extensive expertise in modem system design, computing architecture, IC product solutions, and technology management, he now leads the development of RISC-V ecosystem and technology platforms at ESWIN. Beyond his corporate role, Dr. He actively contributes to industry standardization as the rotating chairman of both the RISC-V Working Committee at the China Electronics Standardization Association and the Zhongguancun Standardization Association, driving the standardization and advancement of RISC-V technologies.

To page top — To session T1.1 — To talk T1.1.07

Tuesday 13, 11:30-13:00

Session chair: Philipp Tomsich, VRULL.

Plenary keynotes and presentations in Gaston Berger amphitheater (S2).

RISC-V State of the Union

Video . Slides

. T1.3.01, Tue 13 at 11:30, in Gaston Berger (S2).

By Krste Asanović, Chief Architect, SiFive.

Abstract: In this session RISC-V’s Chief Architect will give an overview of RISC-V adoption across computing markets from Embedded to AI. Krste will discuss new developments in the RISC-V ISA, including security extensions and matrix extensions for AI, as well as new profile and platform initiatives.

Bio: Krste Asanovic is Professor Emeritus and a Professor of the Graduate School in the EECS Department at the University of California, Berkeley. He received a PhD in Computer Science from UC Berkeley in 1998 then joined the faculty at MIT, receiving tenure in 2005. He returned to join the faculty at Berkeley in 2007, where he co-founded the Berkeley Parallel Computing Laboratory (‘Par Lab’), and led the ASPIRE Lab, and co-led the ADEPT Lab and Berkeley SLICE Lab. His main research areas are computer architecture, VLSI design, parallel programming and operating system design. He has led the RISC-V open ISA project at Berkeley from its inception in 2010 and co-founded the RISC-V Foundation in 2015, which has now become RISC-V International. He is now Chief Architect at RISC-V International. He also co-founded SiFive in 2015 to commercialize RISC-V processors, where he is Chief Architect. He is an ACM Fellow and an IEEE Fellow. (CC BY 3.0 by Krste Asanovic)

To page top — To session T1.3 — To talk T1.3.01

RISC-V ISA Extensions with Hardware Acceleration for Hyperdimensional Computing

Extended abstract . Slides

. T1.3.02 (sub. #109), Tue 13 at 12:00, in Gaston Berger (S2).

By Rocco Martino, Sapienza University of Rome. Marco Angioli, Sapienza University of Rome. Antonello Rosato, Sapienza University of Rome. Marcello Barbirotta, Sapienza University of Rome. Abdallah Cheikh, Sapienza University of Rome. Mauro Olivieri, Sapienza University of Rome.

Abstract: Hyperdimensional Computing (HDC) leverages high-dimensional distributed representations called hypervectors (HVs) and simple arithmetic operations, making it an ideal paradigm for learning tasks on resource-constrained devices. This work introduces the first RISC-V Instruction Set Architecture (ISA) extension specifically designed to execute all fundamental arithmetic operations of HDC directly through dedicated instructions, which, when appropriately combined, enable a variety of learning tasks by efficiently encoding and processing information. This extension is coupled with a specialized hardware acceleration unit, integrated into the Klessydra-T03 RISC-V core, to perform computations on binary HVs efficiently. The proposed solution enables a seamless trade-off between execution time and hardware resource utilization through both synthesis-time configurability and runtime programmability. The custom ISA extension is fully integrated into the RISC-V GCC toolchain, allowing software developers to exploit its capabilities via intrinsic function calls. Benchmarking on an FPGA platform demonstrates significant performance improvements across a wide range of HDC tasks, from basic arithmetic operations to real-world classification problems.

To page top — To session T1.3 — To talk T1.3.02

Real-Time Extension to the RISC-V Advanced Interrupt Architecture

Video . Extended abstract

. Slides

. Poster

. T1.3.03 (sub. #206), Tue 13 at 12:15, in Gaston Berger (S2).

By Alexey Khomich, Synopsys Inc. Evgenii Paltsev, Synopsys. Paul Stravers, Synopsys Inc.

Abstract: The Real-Time Interrupt Architecture (RTIA) is the evolution of RISC-V Advanced Interrupt Architecture (AIA) targeted to extend use cases to real-time latency critical scenarios and/or to resource constrained designs. The RTIA defines necessary mechanisms for interrupt nesting and low latency fixed overhead interrupt handling. Keeping compatibility with RISC-V Privileged ISA and RISC-V AIA, the RTIA provides the same programming model for light weight embedded applications and heavy feature rich systems allowing mixing it in virtual environments.

To page top — To session T1.3 — To talk T1.3.03

RISC-V Heterogeneous Programming Paradigm: Atomic IO Enqueue (AIOE) Extension and AIOE with Virtualization

Video . Extended abstract

. Slides

. Poster

. T1.3.04 (sub. #148), Tue 13 at 12:30, in Gaston Berger (S2).

By Ren Guo, Alibaba Damo Academy.

Abstract: With the increasing diversification of intelligent computing workloads, traditional programming paradigms face multidimensional challenges driven by architectural innovations. Addressing the concurrent demands of heterogeneous tasks, including AI inference, real-time graphics rendering, and high-performance signal processing, this presentation focuses on atomic IO enqueue instructions - the core technology enabling hardware accelerator interactions in heterogeneous computing architectures. This approach establishes efficient accelerator communication mechanisms through hardware primitives such as 64-byte atomic enqueue transfers and queue status feedback. At the protocol level, PCIe specifications define DMWr TLP (Transaction Layer Packet) for non-post write operations, while Armv8.7/9.2 implements 64-byte atomic enqueue operations via ST64BV instructions, and x86 architectures provide comparable functionality through MOVDIR64B and ENQCMD(S) instructions.

This presentation introduces RISC-V’s Atomic IO Enqueue Extension (AIOE) and its virtualization enhancements: the G-stage Page Table In-Process Context (GIPC) mechanism for RISC-V IOMMU, which improves accelerator sharing work queue in multi-tenant environments. In addition, we will share AIOE’s latency mitigation approach for PCI-e.

To page top — To session T1.3 — To talk T1.3.04

Accelerating AI Models with Andes Matrix Multiplication (AMM) and RISC-V Vector (RVV) extensions: From CNNs to LLMs

Video . Extended abstract

. Slides

. T1.3.05 (sub. #86), Tue 13 at 12:45, in Gaston Berger (S2).

By Pei-Hsiang Hung, Andes Technology. Chung-Hua Yen, Andes Technology. I-WEI WU, Andes Technology.

Abstract: Matrix multiplication is a critical operation in a wide range of compute-intensive applications, including machine learning, image processing, and scientific computing. The computational demands of large-scale matrix operations necessitate specialized hardware acceleration to improve efficiency and performance. To address this challenge, RISC-V International (RVI) formed the Integrated Matrix Extension (IME) Task Group. To serve immediate market demands, Andes Technology implements the Andes Matrix Multiplication (AMM) instruction set, an extension to the RISC-V Vector Extension (RVV), which Andes presented in IME meetings. The AMM instruction set introduces two primary enhancements:

- Matrix operations optimized for 8-bit integers, specifically targeting AI and deep learning applications

- Advanced 2D load/store instructions that minimize memory access overhead

To assess AMM’s capabilities, we integrated it into the Intermediate Representation Execution Environment (IREE) for efficient compilation and execution on AMM-enabled RISC-V systems. A key aspect of this implementation involved extending IREE’s compilation infrastructure, which included:

- Developing a new MLIR pass to tensorize matrix multiplication and tensor data load/store operations

- Designing a custom MLIR dialect tailored for AMM to support all its instructions.

- Implementing conversion passes to lower matrix multiplication and tensor operations from the vector dialect to AMM one

Our evaluation covered a broad spectrum of AI models, ranging from convolutional neural networks (CNNs) to large language models (LLMs), to measure performance improvements. This presentation explores the integration process, shares benchmark results, and discusses strategies for optimizing AI workloads using AMM and RISC-V Vector Extensions. We also examine the challenges encountered during AI model compilation and consider future developments in RISC-V-based AI acceleration.

To page top — To session T1.3 — To talk T1.3.05

Tuesday 13, 13:00-14:30

Session chair: Daniel Große, Johannes Kepler University Linz.

Booths and posters in expo area (S1, S2, & S3).

Demos in Louis Armand East amphitheater (S3).

An all RISC-V vehicle is not far away.

Video . T1.4.02, Tue 13 at 13:15, in Louis Armand East (S3).

By Manfred Schlett, Senior Director, SiFive, SiFive.

Abstract: SiFive will discuss the increasing use of RISC-V in the automotive industry and how the market will evolve.

Bio: As SiFive’s Business Director for Automotive, Manfred’s background encompasses executive roles at Automotive Tier 1 suppliers, as well as business and technical leadership across prominent semiconductor companies like Qualcomm, Cambridge Silicon Radio, and Renesas, and innovative startups such as Hyperstone. His Ph.D. in Mathematics complements an exhaustive track record in the design of microprocessors and related platforms.

To page top — To session T1.4 — To talk T1.4.02

Accelerating RISC-V Design and Verification with AI Agents

Video . T1.4.03, Tue 13 at 13:25, in Louis Armand East (S3).

By Mehir Arora, Founding Engineer, ChipAgents.ai.

Abstract: This presentation provides an interactive demonstration of ChipAgents, the breakthrough AI agent for hardware engineering. Built to integrate seamlessly with RISC-V workflows, ChipAgents leverages LLM-powered agents to automate testbench generation, code debugging, and verification tasks. Mehir Arora will walk through the system architecture, real-world usage scenarios, and the impact of AI agents on accelerating RTL iteration cycles. Attendees will gain a first-hand look at how agentic AI is reshaping the chip design process—boosting productivity, coverage, and confidence in critical paths.

Bio: Mehir Arora is a Founding Engineer at ChipAgents, where he leads efforts in agentic AI engineering solutions for chip design and verification. With a background in AI research and systems engineering, Mehir has contributed to high-impact projects across agentic flow orchestration, backend development, waveform agents, and RTL coverage analysis. He specializes in bridging large language models and agentic AI with complex EDA workflows to drive intelligent automation in semiconductor design.

To page top — To session T1.4 — To talk T1.4.03

Accelerating AI/ML SoCs with Andes RISC-V Solutions

Video . T1.4.04, Tue 13 at 13:35, in Louis Armand East (S3).

By Charlie Su, President and CTO Andes Technology, Andes Technology.

Abstract: Andes RISC-V processor solutions have been adopted in various AI/ML SoC architecture. Customers with comprehensive compute engines utilize Andes’ high-performance control processors to keep their hardware fully engaged. Those with specialized GEMM and non-linear function accelerators leverage Andes’ powerful vector processors, enhanced by automated custom extension (ACE) capabilities, to ensure new AI/ML tasks can be performed efficiently within their Processing Elements (PEs) for future proof. For small-scale AI/ML applications, Andes processors with P extension prove effective. This talk will explore Andes’ extensive processor offerings for AI/ML and the comprehensive software stack provided by AndesAIRE™, Andes Intelligence Runs Everywhere.

Bio: Dr. Charlie Su cofounded Andes in 2005. He established R&D and Technical Marketing and has been driving product planning, development, and promotion to establish Asia’s first patented licensable processor IP families AndesCore™. In 2016, Dr. Su led the team to incorporate RISC-V into Andes fifth-generation architecture AndeStar™ V5, and started a new chapter of Andes growth in existing markets such as IOT, MCU/MPU, Storage and WiFi/BT as well as new markets such as AI/ML, Automotive, and 5G. Before returning to Taiwan, Dr. Su spent over 12 years in the Silicon Valley on the Sun multi-core multi-threading Ultrasparc T1 and T2 processors, the C-Cube E-series MPEG media processors, the MIPS OOO R10K processor, and the Intergraph Clipper VLIW processor. Charlie got his Ph.D. in Computer Science from the University of Illinois at Urbana-Champaign.

To page top — To session T1.4 — To talk T1.4.04

Accelerating Future Computing with RISC-V

Video . T1.4.05, Tue 13 at 13:45, in Louis Armand East (S3).

By James Shi, Principal Software Test Engineer, Xuantie.

Abstract: In this presentation, we will introduce the XuanTie IP portfolio —particularly the newly released XuanTie C series IPs, C920 for edge computing, the C930 for server applications, and the AI‑enhanced XuanTie C908X. We will also cover the IP’s supporting ecosystem, including both hardware platform and software support.

Bio: am currently a Principal Software Test Engineer at Alibaba DAMO Academy, focusing on kernel and Linux OS testing for XuanTie RISC-V processors. My expertise includes validating CPU memory models and conducting system integration and performance testing for the high-performance RISC-V CPUs XuanTie C930, C920, and C908. I am actively contributing to RISC-V Certification Steering Committee since in 2024 and Architecture Compatibility Test SIG since 2023. I devoted myself to build a comprehensive and openly-accesable RISC-V certification testing framework and certification system, where I collaborate with the RISC-V International to promote RISC-V certification testing.

To page top — To session T1.4 — To talk T1.4.05

RACE:Powering Next-Gen RISC-V AI Solutions

Video . T1.4.06, Tue 13 at 13:55, in Louis Armand East (S3).

By Shan Lui, Senior Hardware Design Engineer, Beijing Institute of Open-Source Chip (BOSC), BOSC.

Abstract: The RISC-V+AI Computability Ecosystem (RACE) aims to promote the standardization the RISC-V AI instruction set, address fragmentation challenges, and foster innovation in RISC-V AI products with the following key technical objectives: Contribute to RISC-V AI Instruction Set Extension; Coordinate the development of an optimized AI system software stack; Coordinate the development of RISC-V AI IP cores compatible with V+M+T SoC designs; Bridge upstream and downstream ecosystems for seamless adoption. This presentation will focus on the roadmap milestones and technical details in developing a cohesive RISC-V AI products as well as introduce the RACE committee

Bio: Shan Liu is a skilled IP developer with seven years of experience in the semiconductor industry. Formerly a technical leader at Intel, she now leads the Memory Subsystem team at BOSC. Shan specializes in external memory, System on Chip, Network-on-Chip, CPU emulation, FPGA verification, and FPGA acceleration

To page top — To session T1.4 — To talk T1.4.06

Utilizing RISC-V Trace Standards for Efficient Bugfixing and Profiling

Video . Slides

. T1.4.07, Tue 13 at 14:05, in Louis Armand East (S3).

By Nicolas Delemarre, Field Application Engineer & Technical Manager, Lauterbach.

Abstract: This presentation explores the use of RISC-V trace standards to improve debugging and profiling efficiency in modern embedded systems. As chip architectures and embedded systems grow increasingly complex, developers face significant challenges: more powerful multicore processors in various configurations (SMP, AMP), diverse operating systems (Linux, AUTOSAR, …), and heterogeneous multicore architectures that increase debugging requirements. The ‘RISC-V External Debug Support’ specification v1.0.0 offers a comprehensive solution for both simple and complex debugging scenarios, with flexibility to adapt to the most diverse SoCs. The presentation will demonstrate how trace tools leverage these standards to facilitate RISC-V system debugging and optimize application performance.

Bio: Nicolas Delemarre joined Lauterbach in 2018 and serves as both Field Application Engineer and Technical Manager for the French subsidiary. With a degree in Embedded Systems, he is a TRACE32 expert specializing in Arm and RISC-V architectures. As Technical Manager, Nicolas oversees all customer technical support, training, and services. During his six years at Lauterbach, he has assisted hundreds of clients across various platforms and developed custom OS awareness packages for French customers. Nicolas is passionate about solving complex problems and understanding systems “under the hood.” His expertise in RISC-V makes him a valuable resource for customers navigating this open instruction set architecture. Outside of work, he contributes to open-source projects and develops personal Cortex-M based systems, continuously expanding his embedded systems knowledge.

To page top — To session T1.4 — To talk T1.4.07

Tuesday 13, 14:30-15:30

Session chair: Andy Moore, RISC-V International.

Plenary keynotes and presentations in Gaston Berger amphitheater (S2).

Panel -- RISC-V at 15

Video . T1.5.01, Tue 13 at 14:30, in Gaston Berger (S2).

Panelists: Krste Asanović, Chief Architect, SiFive. Yungang Bao, Deputy director of ICT/CAS and Chief Scientist of Beijing Institute of Open Source Chip (BOSC). Stefan Wallentowitz, Professor, Hochschule München & FOSSi Foundation..

Moderator: Andrea Gallo, VP of Technology, RISC-V International.

Argument: As RISC-V marks its 15th birthday, we bring together some key contributors to its development and success, to listen to their experiences and anecdotes and look to the future to see what we can expect from the next 15 years!

To page top — To session T1.5 — To talk T1.5.01

Akeana, leveraging strong legacy to offer the broadest IP portfolio

Video . Slides

. T1.5.02, Tue 13 at 15:00, in Gaston Berger (S2).

By Graham Wilson, Head of Product, Akeana.

Abstract: A history lesson on the evolution of the team that formed Akeana as an industry leader of processor and interconnect IP, allowing them to build and verify a broad range of processor IP.

Bio: Graham has over 25 years of experience in the semiconductor, IP industry with 15 years in processor IP, working at companies as Tensilica/Cadence, Synopsys and SiFive. His main area of focus has been DSP, Vector processors, with recent focus on AI computation processors. At Akeana, Graham is responsible for product management and product marketing.

To page top — To session T1.5 — To talk T1.5.02

Enter the RISC-V AI era with Andes

Video . Slides

. T1.5.03, Tue 13 at 15:02, in Gaston Berger (S2).

By Niraj Dengale, Senior FAE, Andes Technology.

Abstract: Andes has been a pioneer in enabling customers to achieve their AI processing needs through providing both hardware and software solutions. My talk will shade a light on how efficiently Andes is supporting the AI ecosystem.

Bio: Niraj Dengale working as a senior FAE in Andes Technology Europe Munich office to help our customers during the CPU evaluation process as well as after they start SoC integration. Niraj have been in Andes for 7 years and witnessed the impact RISC-V is making in the CPU market.

To page top — To session T1.5 — To talk T1.5.03

Getting towards first-time RISC-V silicon with automated end-to-end formal

Video . Slides

. T1.5.04, Tue 13 at 15:04, in Gaston Berger (S2).

By Ashish Darbari, Founder & CEO, Axiomise.

Abstract: This talk will share how our smart formal methods powered by formalISA® and footprintTM can empower you to build your RISC-V silicon right the first time, going beyond compliance testing by axiomising correctness through exhaustive proofs, exposing corner-case bugs and coverage for functional, PPA, safety and security verification.

Bio: As CEO of Axiomise, Dr Ashish Darbari co-founded and led Axiomise in successfully deploying the unique combination of training, consulting, services, custom solutions, and verification IP. Under his leadership, Axiomise acquired over 20 customers in 7+ years with zero VC funding and turned Axiomise into a multi-million-pound organisation with a team of 25 staff members. Ashish holds a Bachelor’s in EEE from BIT Mesra, India, a Master’s from TU Dresden, Germany and a DPhil in Computer Science from the University of Oxford, focusing on formal verification. Before starting Axiomise, Ashish worked in OneSpin Solutions, Imagination Technologies, General Motors, Arm and Intel.Ashish is a Fellow of the British Computing Society and a senior member of IEEE and ACM. From 2015-1018, he was a Royal Academy of Engineering Visiting Professor at the University of Southampton. A keen innovator in formal verification, Ashish has 67 US, UK and EU patents in formal verification.

To page top — To session T1.5 — To talk T1.5.04

Revolutionizing RISC-V Chip Design with AI Agents

Video . Slides

. T1.5.05, Tue 13 at 15:06, in Gaston Berger (S2).

By David Wang, Founding Engineer, ChipAgents.ai.

Abstract: RISC-V teams today spend months on manual RTL coding and verification. ChipAgents leverages AI agents to turn natural language specs into synthesizable Verilog and full test benches and iterates on them with your existing EDA tools.

Bio: David Wang is a founding engineer at ChipAgents.ai, where he is working to develop language model agents that translate natural-language specs into synthesizable RTL and test benches, dramatically speeding up RISC-V chip design and verification workflows.. Prior to ChipAgents.ai, he worked as a researcher in the UC Santa Barbara NLP Group, where he developed and benchmarked methods to iteratively refine language model outputs using external feedback.

To page top — To session T1.5 — To talk T1.5.05

What's new at Codasip?

Video . Slides

. T1.5.06, Tue 13 at 15:08, in Gaston Berger (S2).

By Peter Shields, Senior Product Manager, Codasip.

Abstract: As the leading European RISC-V vendor, we have a lot going on. This talk will share our latest product updates including new possibilities for fast migration from Arm to RISC-V, new core customization features, and the latest progress in CHERI memory protection. We will also talk about our advancements in high-performance computing as part of the EU-funded DARE project.

Bio: Peter Shields is a Product Manager at Codasip. He has over 25 years of experience in Applications Engineering, Engineering Management and Customer Engineering roles in both EDA and semiconductor IP, particularly for complex SoCs. Prior to Codasip, Peter was a product manager at Siemens, and previously held roles at UltraSoC, Synopsys, Imagination Technologies, Mentor, LogicVision and Cadence. He holds a BEng from the University of Birmingham, UK.

To page top — To session T1.5 — To talk T1.5.06

The LLVM Parallel Universe Project for openEuler: What We Learned from openEuler RISC-V

Video . Slides

. T1.5.07, Tue 13 at 15:10, in Gaston Berger (S2).

By Jingwei Wang, Engineer of the Institute of Software, Chinese Academy of Sciences, openEuler.

Abstract: The LLVM Parallel Universe Project for openEuler is an ambitious exploratory effort to gradually transition openEuler and its broad software ecosystem from GCC to LLVM-based toolchains. Initiated by the Institute of Software, Chinese Academy of Sciences (ISCAS) and openEuler Compiler Lab, the project focuses on the RISC-V architecture while maintaining full compatibility with openEuler’s official codebase, release cycles, and quality standards.By the time of the openEuler 25.03 release, the project had moved to an RVA22 compiler baseline, with support for the Vector extension already activated.

Bio: A member of the openEuler Technical Committee responsible for maintaining the RISC-V SIG, and a participant in the RISC-V Advocate Program, dedicated to strengthening the RISC-V ecosystem within the openEuler community.

To page top — To session T1.5 — To talk T1.5.07

Real-Time Trace: The Key to Streamlined Embedded System Development and Validation

Video . Slides

. T1.5.08, Tue 13 at 15:12, in Gaston Berger (S2).

By Soufian Elmajdoub, Country Manager LAUTERBACH France, Lauterbach.

Abstract: This lightning talk demonstrates how real-time trace technology significantly accelerates embedded system development cycles on RISC-V platforms. We’ll showcase how our JTAG debug tools provide developers with unprecedented visibility into system behavior, enabling faster troubleshooting, more efficient validation processes, and reduced time-to-market.

Bio: Soufian El-Majdoub leads Lauterbach operations in France as Country Manager. With significant experience in the semiconductor industry, he previously held positions at STMicroelectronics and NXP. His technical expertise covers embedded systems, debugging technologies, ARM architectures, embedded Linux, and microcontroller environments, giving him a perfect understanding of the challenges and opportunities in the RISC-V ecosystem. Based in the Paris region, Soufian combines deep technical understanding with business development skills, allowing him to bridge the gap between Lauterbach’s complex debugging solutions and customer needs in the growing RISC-V ecosystem.

To page top — To session T1.5 — To talk T1.5.08

Contribution towards European sovereignty for embedded processors

Video . Slides

. T1.5.09, Tue 13 at 15:14, in Gaston Berger (S2).

By Florian (Flo) Wohlrab, CEO of the OpenHW group, TRISTAN & ISOLDE.

Abstract: The European Union is supporting and advancing the RISC-V ecosystem helping european SME to leverage and build their soverain systems while usign leading technology, The Tristan and Isolde project running since over 2 years and we will give an brief update what we are doing and where you can find details of the generated IP and the status.

Bio: Flo is the Head of the OpenHW Foundation an international non profit organization located in Bruessels and dedicated to curate and maintain high quality, industrial grade, open source RISC-V Cores. Flo is fascinated by RISC-V and help to smoothen accessibility to high quality RISC-V and help promote the RISC-V ISA worldwide. He is also one of the first RISC-V International Ambassadors. Before leading the OpenHW Group Flo was Head of Sales for a commercial RISC-V provider where he took care of the markets in Japan, Europe and Middle East.

To page top — To session T1.5 — To talk T1.5.09

Semidynamics, NPU chip architecture reinvented for ultra-powerful AI with zero latency

Video . Slides

. T1.5.10, Tue 13 at 15:16, in Gaston Berger (S2).

By Volker Politz, CSO, Semidynamics.

Abstract: Semidynamics is revolutionizing NPU with a single RISC-V ISA AI solution. Discover the solutions that we offer and how they can help you in your projects.

Bio: Volker Politz is the Chief Sales officer at Semidynamics, responsible for all IP sales and business development activities as well as product marketing. Prior to this, he was VP sales at Roviero, an AI IP start-up in California, held EU Sales and Global Auto Business management positions in Verisilicon and worked as IP sales manager in Synopsys Europe. He was Vice President of Product and Segment Marketing at Imagination Technologies. He is an international marketing, business development and management executive with over 30 years’ experience in semiconductor and technology companies. He also held roles and responsibilities in Europe, Asia and the United States with experience built from engineering, marketing, sales, and general management positions at Hitachi and Renesas. He has broad know-how in vertical domains such as digital multimedia, broadcast technologies, automotive, industrial, mobile, security and AI. Volker holds a Masters engineering degree in communication electronics from Fachhochschule Konstanz, Germany and an MBA from Open University, United Kingdom.

To page top — To session T1.5 — To talk T1.5.10

The RISC-V momentum continues.

Video . Slides

. T1.5.11, Tue 13 at 15:18, in Gaston Berger (S2).

By Manfred Schlett, Senior Director, SiFive.

Abstract: SiFive will highlight our latest progress in embedded and automotive applications, showcasing how we are driving innovation.

Bio: As SiFive’s Business Director for Automotive, Manfred’s background encompasses executive roles at Automotive Tier 1 suppliers, as well as business and technical leadership across prominent semiconductor companies like Qualcomm, Cambridge Silicon Radio, and Renesas, and innovative startups such as Hyperstone. His Ph.D. in Mathematics complements an exhaustive track record in the design of microprocessors and related platforms.

To page top — To session T1.5 — To talk T1.5.11

Tuesday 13, 15:30-16:30

Session chair: Katzalin Olcoz, University Complutense of Madrid.

Booths and posters in expo area (S1, S2, & S3).

Demos in Louis Armand East amphitheater (S3).

VASCO: ASIC Test Platform for Cybersecurity on FD-SOI

Video . Slides

. T1.6.01, Tue 13 at 15:35, in Louis Armand East (S3).

By Stefano Di Matteo, Research Engineer, Ph.D., CEA.

Abstract: As cybersecurity threats continue to evolve, hardware security has become a critical issue in the design of electronic devices. The advent of quantum computing has forced standardization bodies to rethink cryptographic foundations, leading to the rise of Post-Quantum Cryptography (PQC) as a strategic priority. At the same time, the RISC-V open-source instruction set architecture is emerging as a key enabler of secure hardware, offering new opportunities to design intrinsically secure microarchitectures. To address these research opportunities, CEA has developed VASCO, an ASIC platform designed to innovate, implement and characterize secure hardware primitives. It supports the development of robust countermeasures against side-channel attacks, fault injection and other physical security threats. In addition, VASCO Is adopted for characterization of security primitives such as True Random Numbers Generators (TRNGs) and Physically Unclonable Functions (PUFs). VASCO focuses also on PQC, which requires specialized hardware accelerators to achieve efficient and secure implementations. This demo will present the latest advancements made with VASCO#2, which was fabricated in 2022. Furthermore, the demo will offer a preview of VASCO#3, which will be taped-out in 2025. With an enhanced set of features, VASCO#3 will further extend the platform’s ability to anticipate and mitigate emerging cybersecurity threats.

Bio: Stefano Di Matteo got his master and Ph.D. degrees from the University of Pisa respectively in 2019 and 2023. Currently, he is junior chair in hardware implementation of Post-Quantum Cryptography at CEA in Grenoble. His research interests include hardware implementation of PQC with countermeasures against physical attacks, RISC-V architectures and Instruction Set Extensions for PQC. He contributed to multiple European-funded projects such as European Processor Initiative (SGA1 and SGA2), TEXTAROSSA and AREO, and he has co-authored over 20 publications on hardware implementation of cryptographic algorithms. He supervises Ph.D. and master’s students at CEA.

To page top — To session T1.6 — To talk T1.6.01

CV32A60X - First industrial-grade verified configuration

T1.6.02, Tue 13 at 15:45, in Louis Armand East (S3).

By Jean Roch Coulon, Thales, André Sintzoff, Thales.

Abstract: CV32A60X - First industrial-grade verified configuration

Bio: Jean Roch Coulon is RISC-V Architect at Thales group in France, he designed processors to add security in ARM, SPARC, proprietary and now RISC-V implementations. Expert in processor, toolchain, security, cryptography or code size density. His main contributions in RISC-V are the 32bits version of CVA6 (CV32A6), CV-X-IF and verification. He is an OpenHW group committer; developing, reviewing and merging CVA6 and CORE-V-VERIF pull requests.

Bio: André Sintzoff is Senior Engineer at Thales and currently the verification leader for CV32A60X core at Thales DIS France. He received a master’s degree in microelectronics from UCLouvain, Belgium.He has worked in industry for several positions related to embedded software (3G modems, smartcards). Since 2019, he is working on open source RISC-V processors.

To page top — To session T1.6 — To talk T1.6.02

RISC-V on-chip debug & trace solution: Tessent UltraSight-V

Slides . T1.6.03, Tue 13 at 15:55, in Louis Armand East (S3).

By Devan Sharma, Account Technology Manager (EMEAI), Siemens.

Abstract: Modern applications demand increased compute power resulting in exponential increase in design complexity. These complex RISC-V based SoCs can’t rely on traditional way of debugging, requiring an efficient way of debugging & tracing. In this presentation, we will unveil Tessent UltraSight-V, an end-to-end solution consisting of embedded IP and software designed to provide comprehensive, efficient debugging and trace capabilities that integrates with industry standard tool to further empower embedded software engineers in developing high-performance embedded software. The integration of Tessent UltraSight-V on-chip IP modules and host software empowers engineers to efficiently diagnose the root causes of unexpected behaviour and underperformance. Utilizing effective, non-intrusive techniques such as encoded processor trace based on the Efficient Trace (E-trace) standard, logging, high-speed interfaces (USB 2.0) and DMA for fast code uploads, this solution minimizes debugging delays and accelerates your SoC projects, ensuring they meet their market deadlines.

Bio: Devan holds a master’s degree in digital systems design as well as a post graduate diploma in VLSI technology. Devan spent many years on the technical side, where he designed products which involved writing code in VHDL, Verilog-C and assembler. He was involved in overall FPGA designs vastly experienced working for/with both Altera and Xilinx products. Over the past 15 years, Devan made successful transition into technical sales, held several customer-facing commercial roles in various capacities. Most recently, Devan was responsible for sales of XMOS products in EMEA territory.

To page top — To session T1.6 — To talk T1.6.03

How TRISTAN & ISOLDE contribute to the RISV-C ecosystem

Video . T1.6.04, Tue 13 at 16:05, in Louis Armand East (S3).

By Florian (Flo) Wohlrab, CEO of the OpenHW group, TRISTAN & ISOLDE.

Abstract: The European Union is supporting and advancing the RISC-V ecosystem helping european SME to leverage and build their soverain systems while usign leading technology, The Tristan and Isolde project is represented on the European RISC-V Summit and we will give an overview from our co-exhibitors what each has done in the field of RISC-V within the Tristan&Isolde project, this will be a lightning style talk highlighting different projects.

Bio: Flo is the Head of the OpenHW Foundation an international non profit organization located in Bruessels and dedicated to curate and maintain high quality, industrial grade, open source RISC-V Cores. Flo is fascinated by RISC-V and help to smoothen accessibility to high quality RISC-V and help promote the RISC-V ISA worldwide. He is also one of the first RISC-V International Ambassadors. Before leading the OpenHW Group Flo was Head of Sales for a commercial RISC-V provider where he took care of the markets in Japan, Europe and Middle East.

To page top — To session T1.6 — To talk T1.6.04

Tuesday 13, 16:30-18:00

Session chair: Kevin Martin, Université Bretagne-Sud.

Plenary keynotes and presentations in Gaston Berger amphitheater (S2).

The Custom Silicon Imperative: Addressing Manufacturing and Supply Chain Realities

Video . Slides

. T1.7.01, Tue 13 at 16:30, in Gaston Berger (S2).

By Pablo Valerio, Supply Chain section Editor, EETimes.

Abstract: The semiconductor industry faces creative disruption due to the rise of bespoke silicon driven by demands for AI and high-performance computing, where RISC based cores are displacing traditional stakeholders. This trend presents manufacturing and supply chain challenges due to the cost of development and the complexity of international supply chains. Open-source architectures like RISC-V are gaining traction as an alternative, offering customization and potentially reducing reliance on unstable supply chains, particularly in Europe.

Bio: Pablo Valerio is a seasoned engineer with 30+ years of experience. For over 10 years, he has been a contributing editor and analyst for EE Times (where he edits the Supply Chain section). He also wrote for EPSNews, InformationWeek, EBN, LightReading, Network Computing, and IEEE Xplore. His coverage spans Supply Chain, Semiconductors, Networks, IoT, Security, and Smart Cities. He holds an MEng, Electrical and Electronics Engineering from The Ohio State University.

To page top — To session T1.7 — To talk T1.7.01

Accelerating GenAI Workloads by Enabling RISC-V Microkernel Support in IREE

Video . Extended abstract

. Slides

. Poster

. T1.7.02 (sub. #99), Tue 13 at 16:45, in Gaston Berger (S2).

By Adeel Ahmad, 10xEngineers. Nouman Amir, 10xEngineers. Ahmad Tameem Kamal, 10xEngineers. Bilal Zafar, 10xEngineers. Saad Bin Nasir, 10xEngineers.

Abstract: This project aims to enable RISC-V microkernel support in the IREE Machine Learning Compiler. It includes enabling the lowering of the MLIR operations to IREE microkernel calls and implementing microkernel functions for RISC-V. A comprehensive analysis of RISC-V ISA would also be provided as part of the project to identify areas where it lags behind x86 and ARM when targeting GenAI models. This project is a work in progress, and hence, the proposed methodology is discussed in the extended abstract. We aim to improve the RISC-V software ecosystem and spark community interest in expanding RISC-V support in ML compilers and kernel libraries.

To page top — To session T1.7 — To talk T1.7.02

RISC-V based GPGPU on FPGA: A Competitive Approach for Scientific Computing ?

Extended abstract . Slides

. Poster

. T1.7.03 (sub. #35), Tue 13 at 17:00, in Gaston Berger (S2).

By Eric Guthmuller, Univ. Grenoble Alpes, CEA, List. Jérôme Fereyre, Univ. Grenoble Alpes, CEA, List.

Abstract: FPGA architectures include increasingly complex arithmetic operators and optimized hard IPs, such as memory subsystems and Networks-on-Chip (NoC). This evolution leads to higher compute density also linked with high memory bandwidth. It represents an opportunity to tailor an architecture to niche application needs while being competitive with a costly ASIC implementation. More specifically, scientific computing requires high precision ($>$~32 bits) floating point computation. However, GPU vendors are progressively favoring low precision performance for AI needs, and are even phasing out support for 64-bit floating point compute. We present an analytical study motivating the need to investigate the implementation of an open source 64-bit GPGPU architecture on a state of the art FPGA, as an alternative to GPUs for scientific computing.

To page top — To session T1.7 — To talk T1.7.03

Panel -- Catalysing a new era of European computing innovation with RISC-V

Video . T1.7.04, Tue 13 at 17:15, in Gaston Berger (S2).

Panelists: Russel Haggar (Silicon Catalyst). Yuning Liang (DeepComputing). Roger Espasa (Semidynamics).

Moderator: Trina Watt, Head of Marketing, Rivos.

Argument: RISC-V is driving new waves of local innovation on a worldwide scale with companies and countries using its open and flexible nature to create new products, solutions and initiatives customized to their local needs, that they can also sell on to a worldwide market. This panel will explore how we can make the most of the opportunity for Europe, how RISC-V can catalyse new businesses and initiatives, the opportunities available, and what problems need to be solved to maximize their chances of success.

To page top — To session T1.7 — To talk T1.7.04

Wednesday 14, 08:00-09:00

Session chair: Andrea Gallo, RISC-V International.

Community breakfast in Louis Armand amphitheater (S3).

Panel -- Panel Discussion with RISC-V Ambassadors

Video . T2.0.01, Wed 14 at 08:00, in Louis Armand East (S3).

Panelists: Fatima Saleem (Manager & Senior Engineer, 10xEngineers). Dr. Florian Zaruba (Principal Engineer, Axelera AI). Jeffrey Osier-Mixon (Distinguished Community Architect, Red Hat).

Moderator: Andrea Gallo, VP of Technology, RISC-V International.

Argument: R&D and Industry Insights? What is going right in the RISC-V Community? And what are we missing?

To page top — To session T2.0 — To talk T2.0.01

Wednesday 14, 09:00-10:30

Session chair: Andrea Gallo, RISC-V International.

Plenary keynotes and presentations in Gaston Berger amphitheater (S2).

The case for Open Source Hardware at Thales: Motivations and Recent Miletones with CVA6

Video . Slides

. T2.1.01, Wed 14 at 09:00, in Gaston Berger (S2).

By Bernhard Quendt, Chief Technical Officer Thales Group, Thales.

Abstract: ( need more time)

Bio: Dr. Bernhard Quendt holds engineering degrees from the University of Stuttgart and Télécom Paris (ENST), and completed a PhD at the Technical University of Munich, where he was awarded the Rohde & Schwarz Prize. Formerly Chief Technical Officer for Siemens Digital Industries, Dr. Bernhard Quendt joined the Siemens Communications division in 1999 before being appointed Vice President R&D for Siemens Rail Automation in 2005. In 2011 he took the responsibility for platform activities and R&D as Vice President for Siemens Industrial Automation Systems and since 2015, he held the position of the Chief Technical Officer at Siemens Digital Industries. Bernhard Quendt joined Thales in 2020 as Chief Technical Officer and Senior Vice President.

To page top — To session T2.1 — To talk T2.1.01

Enhancing your RISC-V SoC debug and optimization with embedded functional monitors

Video . Slides

. T2.1.02, Wed 14 at 09:15, in Gaston Berger (S2).

By Mat O’Donnell, Software Architect Lead, Siemens.

Abstract: A modern RISC-V SoC may have up to several thousand embedded processor cores, running highly optimized software workloads in the field. Time-to-market pressures, system performance and in-field reliability requirements drive a need for high visibility into large fleets of deployed devices executing real-life software workloads. Traditional debug solutions are typically not built for the complexity seen in today’s complex SoCs. In this presentation, we will explain how a scalable system of embedded functional monitors combined with embedded and host/cloud based analytic software can provide actionable data and insights that helps debug, validate, and optimize RISC-V SoC devices and systems from lab bring-up to reliable large scale deployment.

Bio: Mat O’Donnell is a Software Architect Tech Lead at Tessent Embedded Analytics, Siemens EDA. Mat has 25 years of experience working in the Software Industry across multiple successful startups. In March 2017 Mat joined Tessent Embedded Analytics providing software solutions for its embedded silicon IPs where he leads a team of engineers specializing in efficient host-based software support for functional monitoring.

To page top — To session T2.1 — To talk T2.1.02

XiangShan KMHv2: An Open Source RISC-V Core with >15/GHz for SPECCPU2006

Video . Slides

. T2.1.03, Wed 14 at 09:30, in Gaston Berger (S2).

By Yungang Bao, Deputy director of ICT/CAS and Chief Scientist of Beijing Institute of Open Source Chip , BOSC.

Abstract: Xiangshan is an open-source high-performance RISC-V core that was initiated in 2020 (https://github.com/OpenXiangShan/XiangShan). After five years of development, Xiangshan has undergone three architectural upgrades and four tape-outs, all of which have met the expected performance targets. Currently, the latest generation of Xiangshan KMHv2, has completed its RTL design and verification, achieving a performance score of 15/GHz for SPECCPU2006, with comprehensive performance close to that of ARM Neoverse N2. It has already been delivered to companies for SoC development. Notably, not only is the RTL codes of Xiangshan itself open-source, but a series of development and verification tools are also open-source. More information will be introduced in the talk.

Bio: Yungang Bao is a professor of Institute of Computing Technology (ICT), Chinese Academy of Sciences (CAS) and the deputy director of ICT, CAS. Prof. Bao founded China RSIC-V Alliance (CRVA) and serves as the secretary-general of CRVA. His research interests include computer architecture and computer systems. He is leading the XiangShan project (https://github.com/OpenXiangShan/XiangShan), which aims to build an open-source high performance RISC-V core. He launched the One Student One Chip (OSOC) Initiative in 2019. His work was published on top conferences and journals such as ASPLOS, Communication of the ACM, HPCA, ISCA, MICRO etc. and was selected to IEEE Micro Top Picks. He was the winner of CCF-Intel Young Faculty Award of the year for 2013 and the winner of CCF-IEEE CS Young Computer Scientist Award and China’s National Lofty Honor for Youth under 40 of the year for 2019.

To page top — To session T2.1 — To talk T2.1.03

Scaling Open Compute: RISC-V, Chiplets, and the Future of AI and Robotics

Video . Slides

. T2.1.04, Wed 14 at 09:45, in Gaston Berger (S2).

By Wei-Han Lien, Chief Architect and Senior Fellow, Tenstorrent.

Abstract: As artificial intelligence and autonomous systems become increasingly pervasive, the demand for scalable, high-performance, and open computing platforms is more critical than ever. This presentation outlines Tenstorrent’s approach to advancing RISC-V beyond its embedded roots into mainstream high-performance and automotive markets through mature IP and modular architecture.We introduce Tenstorrent’s RISC-V CPU roadmap, featuring the Ascalon and Callandor cores, designed for high SPECINT performance, and the Ascalon-Auto variant, which incorporates ISO 26262-compliant safety features for ADAS and autonomous driving applications. These processors are implemented using chiplet-based design and are paired with Tensix AI accelerators, enabling efficient support for AI workloads across edge devices, data centers, and automotive platforms.Central to this platform strategy is the Open Chiplet Architecture (OCA)—a layered, open standard that facilitates interoperability across chiplets from different vendors. OCA standardizes interfaces across software, system management, transport, and physical layers, enabling modular, composable system integration and fostering a collaborative ecosystem for heterogeneous compute systems.Together, these technologies represent a unified hardware-software strategy to support ubiquitous AI computing. They position RISC-V as a competitive, open alternative to proprietary architectures, ready to power the next generation of AI-enabled and automotive systems. This presentation underscores the role of openness, scalability, and performance in shaping the future of personalized and distributed intelligence through high-performance RISC-V platforms.

Bio: (Wei-Han Lien is a Chief Architect and Senior Fellow in Machine Learning hardware architecture. He is currently leading an architecture team in defining a high-performance RISC-V CPU, fabric, system caching, and high-performance memory subsystem for the Tenstorrent heterogeneous high-performance computation platform for AI and HPC computing. He is also leading the definition of Tenstorrent’s chiplet architecture for constructing scalable, configurable, and composable SiP with cohesive power management, security, and system management architectural definitions for compatibility.Before joining Tenstorrent, Wei-Han joined Apple through the PA Semi acquisition. He led Apple design team on the microarchitectural definitions of two of the most transformative Apple iPhone/iPad application processors from scratch, the A6 and A7 CPU projects. The Apple A7 CPU core is a solid CPU microarchitecture substrate for future generations of A-series (A7-A14) iPhone/iPad mobile processors and M-series (M1) MacBookPro processors. Before Apple, he was a distinguished architect leading P.A.Semi’s PWRficient PA6T dual O-o-O triple-issue superscalar PowerPC CPU cores. At Raza Microelectronics, he led the microarchitectures of the single-chip 40Gb scalable shared-memory switching chip and distributed-shared-memory cache coherent Ethernet switch. He joined Nexgen and AMD after graduating from the University of Michigan; he was part of a team designing the Nx586 (AMD K6), the most competitive microprocessor product to the Intel Pentium processor from 1997-1999 in the market.

To page top — To session T2.1 — To talk T2.1.04

Cloud based RISC-V servers: How and why we built them, how you can use them

Video . Slides

. T2.1.05, Wed 14 at 10:00, in Gaston Berger (S2).

By Fabien Piuzzi, R&D Engineer, Scaleway.

Abstract: Tasked with investigating the readiness of RISC-V servers, Scaleway Labs identified the lack of readily available RISC-V servers as a missing piece for the wider RISC-V ecosystem. Based on recently released hardware, Scaleway launched the first cloud based RISC-V offer, making it available to everyone in a few clicks and a few minutes. This presentation outlines the motivation, challenges, and technical efforts behind this initiative, detailing the process from research to deployment and the lessons learned. We also discuss the future of RISC-V in datacenters and our expectations from hardware manufacturers to accelerate RISC-V adoption. Scaleway, founded in 1999, provides managed solutions for bare metal, containerization, and serverless, offering a robust, scalable infrastructure for AI and machine learning workloads, and is recognized as a key innovator in this domain in Europe.

Bio: Fabien Piuzzi is an R&D Engineer at the cloud provider Scaleway, where he leads the company’s RISC-V initiatives. With over 20 years of experience in open source software and hardware, he has a strong background in Linux servers, embedded systems, and a particular focus on energy efficiency. As part of his role, he has been tasked with assessing the readiness of RISC-V for server applications and led Scaleway’s project to launch the first cloud-based RISC-V servers in 2024.

To page top — To session T2.1 — To talk T2.1.05

Wednesday 14, 10:30-11:30

Session chair: Teresa Cervero, BSC.

Booths and posters in expo area (S1, S2, & S3).

Demos in Louis Armand East amphitheater (S3).

Using CMSIS for simplified migration to RISC-V

Video . T2.2.01, Wed 14 at 10:35, in Louis Armand East (S3).

By Keith Graham, Vice President of University and Customer Experience Program, Codasip.

Abstract: CMSIS was originally designed to enable Arm applications to run seamlessly across the Arm processor portfolio. By leveraging Codasip’s CMSIS-DSP and CMSIS-NN libraries, we enable applications developed for legacy Arm cores to run on cutting-edge, domain-optimized RISC-V implementations without the need for modifications to the software.

Bio: I began as a hardware engineer developing memory management unit and cache for a multi-processor server. My career moved into selling semiconductors and becoming a small business owner as a manufacturer sales representative. My next career landed me as an Associate Chair of the ECEE Dept at the University of Colorado teaching both undergraduate and graduate courses. I am leading Codasip’s University Program working with universities globally to enhance both undergraduate and graduate curriculum and with Research Faculty to solve tomorrow’s computational challenges.

To page top — To session T2.2 — To talk T2.2.01

openEuler for RISC‑V Servers: Challenges & Roadmap

Video . Slides

. T2.2.02, Wed 14 at 10:45, in Louis Armand East (S3).

By Yanjun Wu, Deputy Director and Chief Engineer of the Institute of Software, Chinese Academy of Sciences, openEuler.

Abstract: With the release of the RISC-V Server Platform SPEC and strong backing from RISC-V International, RISE, and other leading vendors, standardized RISC-V servers featuring cutting-edge IP such as SiFive’s P870 and Xiangshan’s Kunminghu are set to debut around 2025 and 2026. As a dedicated server operating system, openEuler is ideally positioned to capitalize on this momentum. In the upcoming 26.03 release, openEuler will offer comprehensive support for the RISC-V Server Platform SPEC. Our clearly defined roadmap takes a phased approach to addressing both kernel and userspace requirements. The first phase focuses on robust kernel support by enabling the 6.6 LTS kernel to integrate ServerPlatform Generic Drivers and by validating the RVA23 standard; this will be followed by targeted userspace enhancements. In this initial phase, optimization efforts will concentrate on enhancing performance for compile and storage servers while actively collaborating with hardware vendors to establish a robust, unified kernel foundation.

Bio: Chairman of the RISC-V Ecosystem & Industry of China Electronics Standardization Association(RVEl),former member of the Technical Steering Committee (TSC) of RVI,His research interest includes Operating System

To page top — To session T2.2 — To talk T2.2.02

Cervell™: Revolutionizing AI Compute with Scalable RISC-V NPU Architecture

Video . T2.2.03, Wed 14 at 10:55, in Louis Armand East (S3).

By Roger Espasa, Ceo & Founder, Semidynamics.

Abstract: Cervell™, developed by Semidynamics, is a scalable RISC-V Neural Processing Unit that integrates CPU, Vector, and Tensor functionalities for zero-latency AI workloads. With configurable performance from 8 to 64 TOPS, it delivers efficient AI acceleration for LLMs, Deep Learning, Edge AI, and Datacenters. Fully programmable with standard RISC-V ISA, Cervell™ ensures flexibility and eliminates vendor lock-in, redefining high-efficiency with a single ISA AI solution.

Bio: Roger Espasa is the CEO and Founder of Semidynamics. Prior to the foundation of Semidynamics, Roger was Technical Director/ Distinguished Engineer at Broadcom leading a team designing a custom ARMv8/v7 processor on 28nm for the set-top box market. Before its experience at Broadcom, from 2002 to 2014, Roger led various x86 projects at Intel as Principal Engineer: SIMD/vector unit and texture sampler on Knights Ferry (45nm), L2 cache, texture sampler on Knights Corner (22nm), the out-of-order core on Knights Landing (14nm) and the Knights Hill core (10nm). From 1999 to 2001 he worked for the Alpha Microprocessor Group on a vector extension to the Alpha architecture. Roger got his Phd in Computer Science from Universitat Politècnica de Catalunya in 1997 and has published over 40 peer-reviewed papers on Vector Architectures, Graphics/3D Architecture, Binary translation and optimization, Branch Prediction, and Media ISA Extensions. Roger holds 9 patents with 41 international filings.

To page top — To session T2.2 — To talk T2.2.03

Making RISC-V Market-Ready: The Economic Case for Formal Verification

Video . Slides

. T2.2.04, Wed 14 at 11:05, in Louis Armand East (S3).

By Ashish Darbari, Founder & CEO, Axiomise.

Abstract: RISC-V architecture accelerates innovation by allowing different types of chip applications, from embedded to data centres and hyperscalers to edge AI. Designing a RISC-V processor is not the most challenging task, but with a myriad of customisations possible with open-source architecture, verification remains a bottleneck in making RISC-V market-ready. The processors should be verified beyond doubt for functionality, and as energy remains the centre focus for AI-based chips as well as mobile and embedded – power, performance and area optimisation are critical. This talk will share how automated formal methods could shrink time-to-market and costs to get the RISC-V processors and SoCs ready, going beyond compliance verification with the highest possible quality of certification possible through formal methods based bug hunting, exhaustive proofs and coverage. We have made formal easy and fast to adopt for functional verification as well as PPA, safety and security.

Bio: As CEO of Axiomise, Dr Ashish Darbari co-founded and led Axiomise in successfully deploying the unique combination of training, consulting, services, custom solutions, and verification IP. Under his leadership, Axiomise acquired over 20 customers in 7+ years with zero VC funding and turned Axiomise into a multi-million-pound organisation with a team of 25 staff members. Ashish holds a Bachelor’s in EEE from BIT Mesra, India, a Master’s from TU Dresden, Germany and a DPhil in Computer Science from the University of Oxford, focusing on formal verification. Before starting Axiomise, Ashish worked in OneSpin Solutions, Imagination Technologies, General Motors, Arm and Intel. Ashish is a Fellow of the British Computing Society and a senior member of IEEE and ACM. From 2015-1018, he was a Royal Academy of Engineering Visiting Professor at the University of Southampton. A keen innovator in formal verification, Ashish has 67 US, UK and EU patents in formal verification.

To page top — To session T2.2 — To talk T2.2.04

Wednesday 14, 11:30-13:00

Session chair: Olivier Sentieys, INRIA.

Plenary keynotes and presentations in Gaston Berger amphitheater (S2).

A Safe Software Convergence: How Automotive and Industrial Designs are Eliminating Boundaries and Creating Opportunities

Video . Slides

. T2.3.01, Wed 14 at 11:30, in Gaston Berger (S2).

By Edward Wilford, Senior Research Manager, Omdia.

Abstract: For decades, the automotive sector has been considered something of an island, with a high moat and a unique development cycle. However, in recent years and spurred mainly by a rich crop of new entrants from China, automotive technology has accelerated and broadened. A new focus on more general-purpose compute, driven by a software-first approach, has as an unintended but beneficial consequence opened up the barriers between automotive and industrial applications, and paved the way for product development shaped more by function than application. This talk will demonstrate that the various software-defined system revolutions are in fact a single phenomenon happening across industries, anywhere where advanced edge deployments are on the rise. Furthermore, why this presents itself as a unique opportunity for RISC-V will be discussed.

Bio: Edward is the Senior Research Director, Automotive, at Wards Intelligence and Omdia Automotive, having previously covered automotive AI and semiconductors as Omdia’s Senior Principal Analyst, IoT. He has written extensively on embedded applications processors, edge AI, advanced connectivity, and novel semiconductor architectures such as RISC-V. He started in the industry in 2016 when he joined Arm as a market intelligence analyst, leading market research and forecasting in the automotive and IoT division. He has also worked in financial services and media roles in London. He has a BA from Durham University and an MPhil in Linguistics from the University of Cambridge.

To page top — To session T2.3 — To talk T2.3.01

Exhaustive Security Verification of CHERI Processors

Video . Extended abstract

. Slides

. Poster

. T2.3.02 (sub. #63), Wed 14 at 11:45, in Gaston Berger (S2).

By Anna Lena Duque Antón, RPTU Kaiserslautern-Landau. Johannes Müller, RPTU Kaiserslautern-Landau. Philipp Schmitz, RPTU Kaiserslautern-Landau. Tobias Jauch, RPTU Kaiserslautern-Landau. Alex Wezel, RPTU Kaiserslautern-Landau. Lucas Deutschmann, RPTU Kaiserslautern-Landau. Mohammed R. Fadiheh, Stanford University. Dominik Stoffel, RPTU Kaiserslautern-Landau. Wolfgang Kunz, RPTU Kaiserslautern-Landau.

Abstract: CHERI is a promising approach to safeguarding data in memory by providing and enforcing fine-grained memory protection directly in hardware. The recently published VeriCHERI verification flow can verify global confidentiality and integrity properties for CHERI systems “spec-free”, i.e., without relying on a golden ISA model. We present a case study to demonstrate the effectiveness and scalability of VeriCHERI on the CHERIoT Ibex RISC-V processor.

To page top — To session T2.3 — To talk T2.3.02

The RISE Project: Advancing RISC-V Software

Video . Slides

. T2.3.03 (sub. #171), Wed 14 at 12:00, in Gaston Berger (S2).

By Nathan Egge, Google. Ludovic Henry, Rivos.

Abstract: The RISC-V Software Ecosystem (RISE) Project is in high gear investing time and money on software to support RISC-V, including more than $500K on contracts for further enhancements. This talk will highlight the way RISE prioritizes projects, and will outline some of our key achievements in the past year.

We have many ideas for further development and investments in 2025. Please join us for a deep dive into the latest developments shaping the RISC-V software ecosystem.

To page top — To session T2.3 — To talk T2.3.03

CVA6S+: A Superscalar RISC-V Core with High-Throughput Memory Architecture

Video . Extended abstract

. Slides

. Poster

. T2.3.04 (sub. #186), Wed 14 at 12:15, in Gaston Berger (S2).

By Riccardo Tedeschi, University of Bologna. Gianmarco Ottavi, University of Bologna. Nils Wistoff, ETH Zurich. Zexin Fu, ETH Zurich. Filippo Grillotti, STMicroelectronics. Fabio De Ambroggi, STMicroelectronics. Elio Guidetti, STMicroelectronics. César Fuguet, Univ. Grenoble Alpes, Inria. Luca Benini, ETH Zurich, University of Bologna. Davide Rossi, University of Bologna.

Abstract: Open-source RISC-V cores are increasingly adopted in high-end embedded domains such as automotive, where maximizing instructions per cycle (IPC) is becoming critical. Building on the industry-supported open-source CVA6 core and its superscalar variant, CVA6S, we introduce CVA6S+, an enhanced version incorporating improved branch prediction, register renaming and enhanced operand forwarding. These optimizations enable CVA6S+ to achieve a 43.5% performance improvement over the scalar configuration and 10.9% over CVA6S, with an area overhead of just 9.30% over the scalar core (CVA6). Furthermore, we integrate CVA6S+ with the OpenHW Core-V High-Performance L1 Dcache (HPDCache) and report a 74.1% bandwidth improvement over the legacy CVA6 cache subsystem.

To page top — To session T2.3 — To talk T2.3.04

A RISC-V based accelerator for Post Quantum Cryptography

Video . Extended abstract

. Slides

. Poster

. T2.3.05 (sub. #112), Wed 14 at 12:30, in Gaston Berger (S2).

By Ambily Suresh, Silicon Austria Labs. Andrew Wilson, Silicon Austria Labs. Diego Gigena-Ivanovich, Silicon Austria Labs. Manuel Freiberger, Silicon Austria Labs. Willibald Krenn, Silicon Austria Labs.

Abstract: Post-Quantum Cryptography (PQC) is a topic of increased interest in the past decade, both with regards to the cryptosystem definition and the hardware and software implementations to perform at optimum efficiency. We present our ongoing work on the implementation of RISC-V based accelerators for PQC algorithms, in particular the Classic McEliece Key Encapsulation Mechanism. Our system includes a PQC accelerator and an Open-HW Group CVA-6 core along with a PQC-specific instruction set. This presentation describes the architecture, performance estimates, and demonstration plans in the future.

To page top — To session T2.3 — To talk T2.3.05

Implementing Runtime-Configurable Endianness in RISC-V: Challenges and Solutions

Video . Extended abstract

. Slides

. Poster

. T2.3.06 (sub. #105), Wed 14 at 12:45, in Gaston Berger (S2).

By Lawrence Hunter, Codethink. Roan Richmond, Codethink. Ben Dooks, Codethink.

Abstract: The RISC-V Privileged Specification introduced dynamic endianness switching in version 1.12, though no commercial hardware yet supports it. This work extends QEMU to enable big-endian execution, allowing the booting of a big-endian Linux system with OpenSBI. Modifications were required across QEMU, OpenSBI, the Linux kernel, and supporting libraries to ensure correct memory operations, instruction encoding, and runtime patching. The project demonstrates the feasibility of big-endian support for RISC-V, providing a foundation for future hardware and software development.

To page top — To session T2.3 — To talk T2.3.06

Wednesday 14, 13:00-14:30

Session chair: Nick Kossifidis, FORTH-ICS.

Booths and posters in expo area (S1, S2, & S3).

Demos in Louis Armand East amphitheater (S3).

Running Data Center and AI Inference Applications on the Veyron V2 Thunderhill FPGA Platform

Video . Slides

. T2.4.01, Wed 14 at 13:05, in Louis Armand East (S3).

By Andrew Jones, Principal Software Engineer, Ventana, Robin Dapp, Ventana.

Abstract: Experience the performance and design maturity of Ventana’s Veyron V2, showcased on the Thunderhill FPGA platform. This demo features full data center software stacks and AI inference workloads running on Ubuntu, highlighting platform readiness for real-world deployment.

To page top — To session T2.4 — To talk T2.4.01

Breaking Performance Barriers

Video . Slides

. T2.4.03, Wed 14 at 13:25, in Louis Armand East (S3).

By Graham Wilson, Head of Product, Akeana.

Abstract: Akeana enables next generation SoC with leading edge performance. This performance comes from CPU compute capability, single and multi-threaded, along with performance scalability of multi-core, multi-cluster systems. Along with processing performance, data computation performance is key with vector extension and custom instructions, but also parallel processing, data movement and optimized interconnect fabrics. These performance strengths enable customers SoC in a broad range of applications including Automotive, AI Hyper scalar, AI Edge and Security applications.

Bio: Graham has over 25 years of experience in the semiconductor, IP industry with 15 years in processor IP, working at companies as Tensilica/Cadence, Synopsys and SiFive. His main area of focus has been DSP, Vector processors, with recent focus on AI computation processors. At Akeana, Graham is responsible for product management and product marketing.

To page top — To session T2.4 — To talk T2.4.03

The Innovation and Application of RISC-V Intelligent Computing Chips

Video . T2.4.04, Wed 14 at 13:35, in Louis Armand East (S3).

By Haibo Lu, Executive VP of Embodied Intelligence Business Group, ESWIN.

Abstract: The speech covers an introduction to ESWIN Computing company and its intelligent computing chips. The chips being introduced feature a 64-bit RISC-V processor and self-developed highly energy-efficient NPU. They support video codec standards like H.264 and H.265, along with a wide range of audio and video interfaces. The chips deliver computing power of up to 40T. We can offer a diverse range of products, including chips, computing power cards, and AI Boxes, customized to meet users’ specific requirements. We provide high-efficiency solutions for customers in fields such as large-scale models, cloud computing, and smart devices.

Bio: Mr. Haibo Lu has more than 20 years of R&D and management experience in the field of integrated circuits. His main technical strengths include artificial intelligence network accelerator architecture, machine learning, audio and video codec technology, cloud computing, etc., and he has several years of overseas work experience. During the period of working at ESWIN Computing Company, he took the lead in the development of the company’s first RISC-V edge computing SoC and multi-purpose intelligent computing SoC, and promoted the solution products in multiple scenarios. He once served as the head of the system architecture department, virtualization team, and driver team of a well-known Chinese intelligent chip enterprise. During that period, he led the team to complete the development of several core computing chips and participated in the development of several intelligent computing chips. He also served as the CTO of a Chinese digital TV and multimedia chip enterprise. The multiple SoCs he led in development achieved remarkable sales volume in the industry.

To page top — To session T2.4 — To talk T2.4.04

Wednesday 14, 14:30-15:30

Session chair: Christian Fabre, CEA.

Plenary keynotes and presentations in Gaston Berger amphitheater (S2).

RISC-V: Powering the Future of High Performance Computing?

Video . Slides

. T2.5.01, Wed 14 at 14:30, in Gaston Berger (S2).

By Nick Brown, Senior Research Fellow, EPCC.